# Power Delivery System Design Automation

Tao Xu taoxu@sigrity.com

A Proposal for Specification of System-Level Design Requirements

Asian IBIS Summit, Beijing China, September 11, 2007

- PDS affects I/O performance

- Technology trends

- Time domain analysis

- SSN simulation with IBIS

- Frequency domain analysis

- PDS impedance approach

- Recent PDS design automation

- Target Impedance in IBIS

- PDS Design Flow

Why is good PDS design important?

#### PDS Affects I/O Performance

Noise from bad PDS affects signal quality

Noise from bad PDS affects

- PDS affects I/O performance

- Technology trends

- Time domain analysis

- SSN simulation with IBIS

- Frequency domain analysis

- PDS impedance approach

- Recent PDS design automation

- Target Impedance in IBIS

- PDS Design Flow

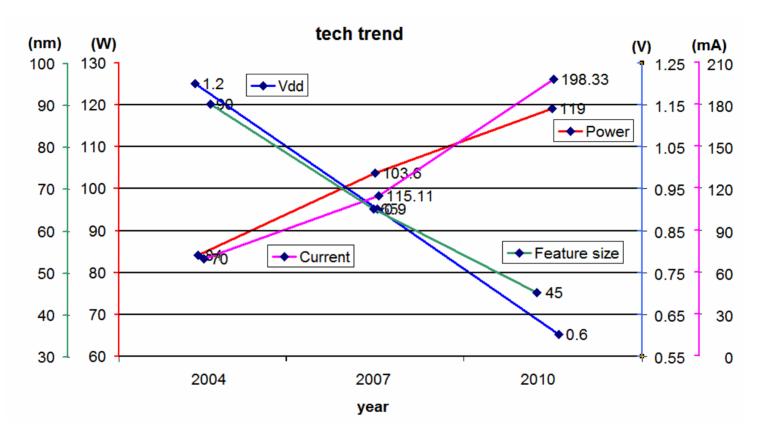

# **Technology Trends**

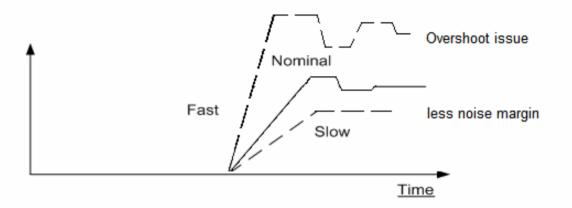

with process size shrinking, system voltages dropping, load currents rising, and clock rates increasing, good PDS design is now crucial to system performance.

- PDS affects I/O performance

- Technology trends

- Time domain analysis

- SSN simulation with IBIS

- Frequency domain analysis

- PDS impedance approach

- Recent PDS design automation

- Target Impedance in IBIS

- PDS Design Flow

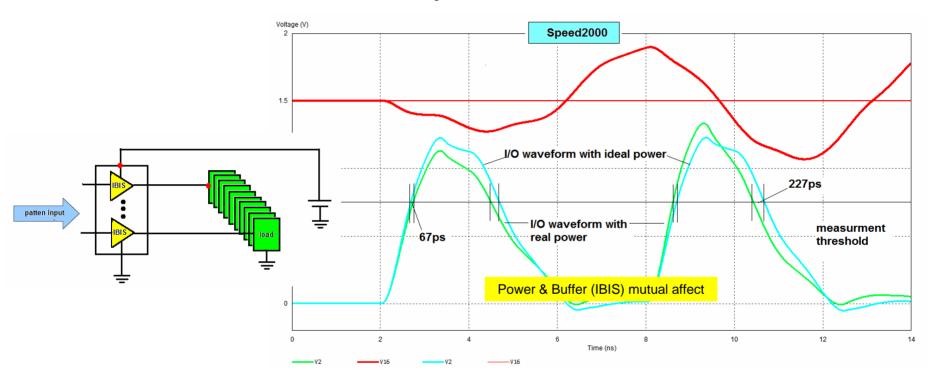

IBIS enables time domain PDS performance verification.

# Time Domain Analysis SSN analysis with IBIS

- IBIS provides effective ways to study how PDS interacts with signals in time domain

- direct indication on Peak-to-Peak noise; easily know final signal waveform with real power supply models

- rely on pattern assumptions, one simulation for one input vector

- Good way to validate the final performance of system

- PDS affects I/O performance

- Technology trends

- Time domain analysis

- SSN simulation with IBIS

- Frequency domain analysis

- PDS impedance approach

- Recent PDS design automation

- Target Impedance in IBIS

- PDS Design Flow

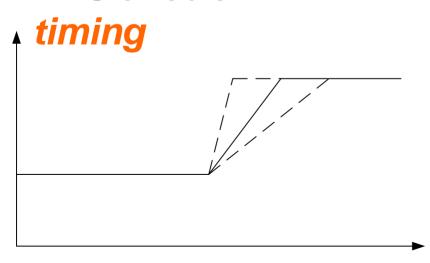

Frequency

domain is

efficient, but

what

impedance to

specify?

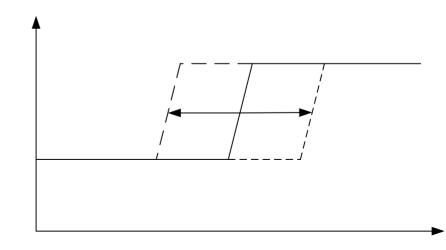

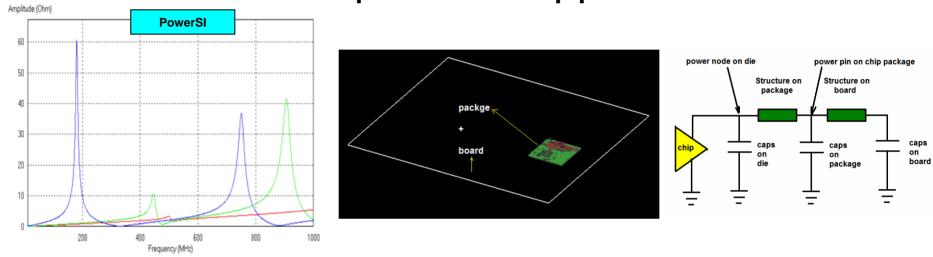

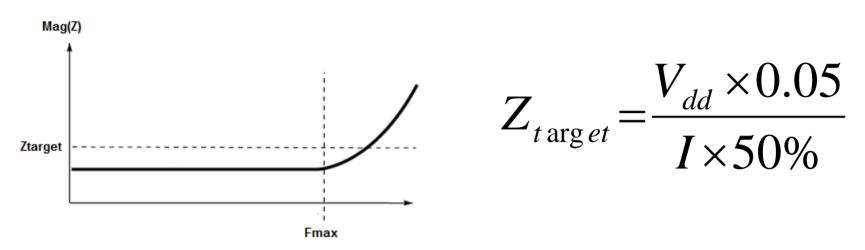

# Frequency Domain Analysis PDS impedance approach

- Higher PDS performance corresponds to lower input impedance seen from the component (chip) into the system.

- PDS impedance at the chip, looking into the package or board, can be simulated accurately with EDA tools, including the effects of: VRM, board, package, and decaps

- PDS design success can be judged by comparison of impedance to a "target" or "reference" impedance (*Z\_target*).

- PDS affects I/O performance

- Technology trends

- Time domain analysis

- SSN simulation with IBIS

- Frequency domain analysis

- PDS impedance approach

- Recent PDS design automation

- Target Impedance in IBIS

- PDS Design Flow

New PDS analysis and optimization

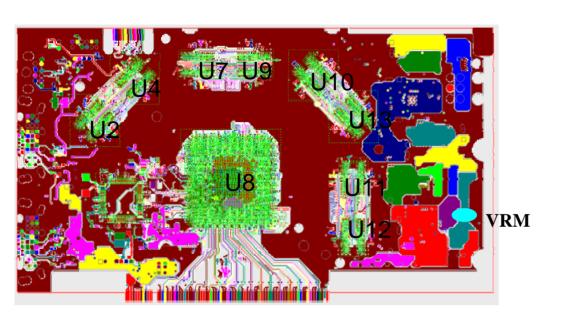

### Automated PDS Design Flow

- Performance and Cost Optimization

- Input for PDS design

- Physical: stack-up, layout, decap library

- Electrical: initial decap placement or Z\_target

- Analysis and Optimization tasks for PDS

- Frequency domain, full-wave PDS analysis

- Optimization of decap placement/selection

- Results of automated EDA design flow

- Lowest manufacturing cost for specified system-level performance

- Highest performance for a range of cost

- Reduced design area

- Interactive cost-performance tradeoffs

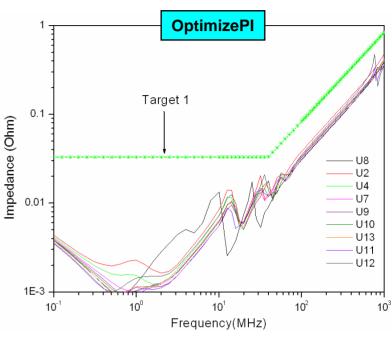

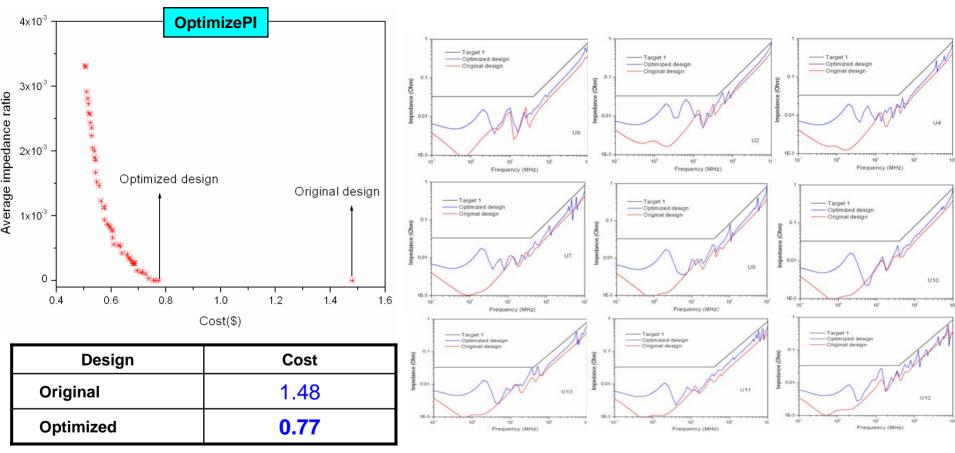

#### Case 1

- Nine component impedances control the optimization process.

- Green curve is user-specified Z\_target.

- original design used as a reference.

### Optimum Performance vs. Cost

- Cost reduced by half, while maintaining the required systemlevel performance.

- Component-level performance details are shown.

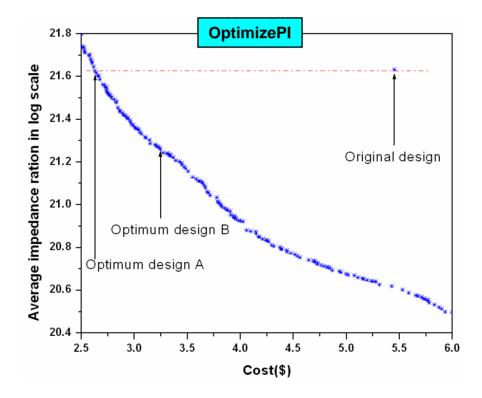

#### Case 2

- Eleven component impedances control the optimization process

- No Z\_target was provided by component manufacturer

- Original design impedance used as a reference

- Interactive cost-performance tradeoffs are examined

# Capacitor Configurations

|                     | Average Impedance<br>Ratio | Cost(\$) |  |

|---------------------|----------------------------|----------|--|

| Original Design     | 21.633                     | 5.49     |  |

| Optimum<br>Design A | 21.628                     | 2.67     |  |

| Optimum<br>Design B | 21.270                     | 3.32     |  |

| Optimum<br>Design A |     | Optimum<br>Design B |     | Original<br>Design |     |

|---------------------|-----|---------------------|-----|--------------------|-----|

| Cap ID              | Qty | Cap ID              | Qty | Cap ID             | Qty |

| 1                   | 1   | 1                   | 1   | 1                  | 32  |

| 2                   | 3   | 2                   | 2   | 3                  | 2   |

| 3                   | 5   | 3                   | 2   | 7                  | 30  |

| 4                   | 13  | 4                   | 3   | 9                  | 2   |

| 5                   | 5   | 5                   | 6   | 11                 | 1   |

| 6                   | 45  | 6                   | 47  | 23                 | 3   |

| 20                  | 4   | 10                  | 3   | 20                 | 14  |

| 23                  | 4   | 20                  | 8   | 27                 | 1   |

|                     |     | 23                  | 4   | 28                 | 8   |

|                     |     |                     |     |                    |     |

Cost: \$2.67 Cost: \$3.32 Cost: \$5.49

■ Interactive cost-performance tradeoffs quickly determine designs with both better performance and lower cost.

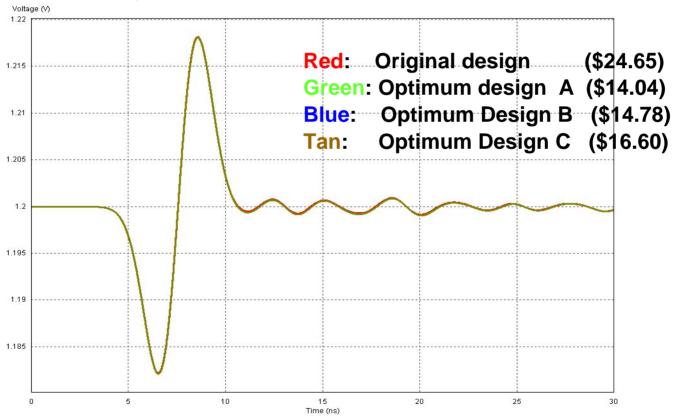

#### Case 3 - Time Domain Verification

- Frequency-domain optimization was performed first.

- All devices driven simultaneously with Gaussian current pulses.

- Time domain voltage noise performance provides an alternative mean of verifying the frequency-domain impedance performance prediction

- PDS affects I/O performance

- Technology trends

- Time domain analysis

- SSN simulation with IBIS

- Frequency domain analysis

- PDS impedance approach

- Recent PDS design automation

- Target Impedance in IBIS

- PDS Design Flow

Where to get

Z\_target to

define PDS

design goals?

### Target Impedance

- Z\_target from simple calculation

- more detailed and accurate simulations are usually available

- Z\_target from reference design (chip manufacturer)

- I/O design has applied and can generate Z\_target requirements

- Available EDA tools are able to extract Z\_target of reference and demo designs

- Z\_target from previous successful design (system manufacturer)

- Meet or beat actual PDS impedance of previous generation system

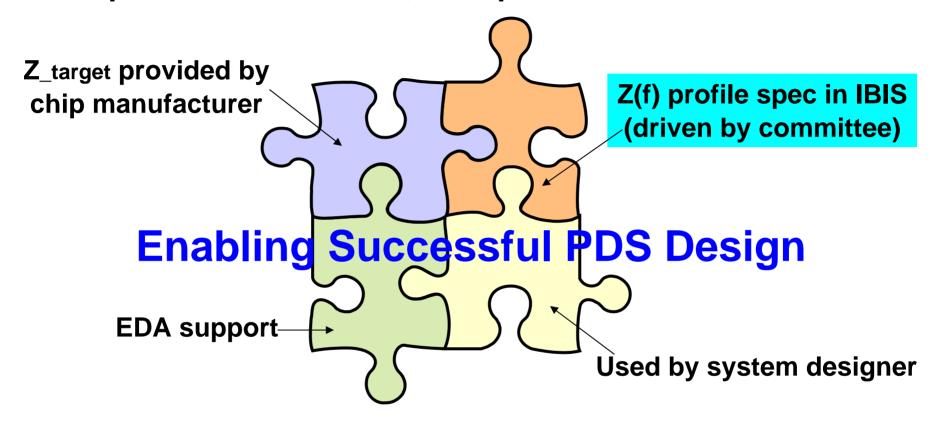

#### Proposal for Z\_target Specification in IBIS

#### A win-win-win scenario:

- System designers require Z<sub>target</sub> to define PDS design goals.

- Chip manufacturer's existing component-specific PI knowledge can be leveraged in a standard manner.

- EDA vendors can provide support of Z\_target specification in IBIS to enable automated and successful PDS design.

- PDS affects I/O performance

- Technology trends

- Time domain analysis

- SSN simulation with IBIS

- Frequency domain analysis

- PDS impedance approach

- Recent PDS design automation

- Target Impedance in IBIS

- PDS Design Flow

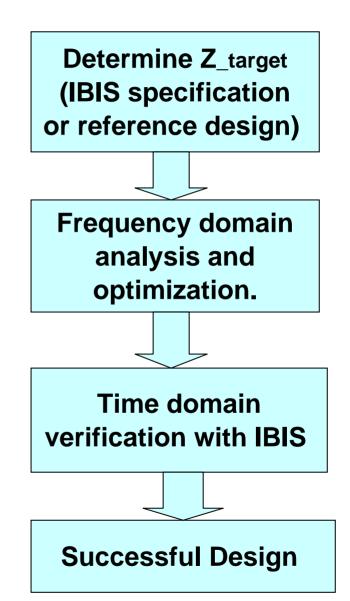

# PDS Design Flow

- Z\_target profile definition should be added to IBIS.

- leverages existing knowledge of chip vendors.

- enables system design goals to be defined.

- EDA vendors will quickly apply this information with PDS analysis and optimization tools.

- Verification with IBIS in time domain is suggested, applying actual current profiles.

#### Thank You!

Advanced Power and Signal Integrity Solutions for Chips, Packages and Boards