# SiSoff

## **IBIS "Over Clocking" Case**

Robert Haller Eric Brock rhaller@sisoft.com Signal Integrity Software, Inc. 978-461-0449 X 15

#### When Does "Over Clocking" Occur

- VT curve time comparable to simulation data rate

- Excessive Dead time in VT curves

- Large variation between Slow and Fast VT Curves

- Results in Unpredictable Simulator Behavior

- · i.e. SPICE

- Others ?

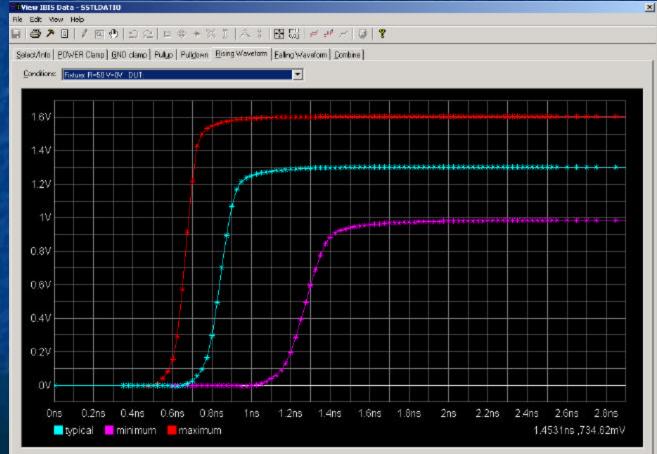

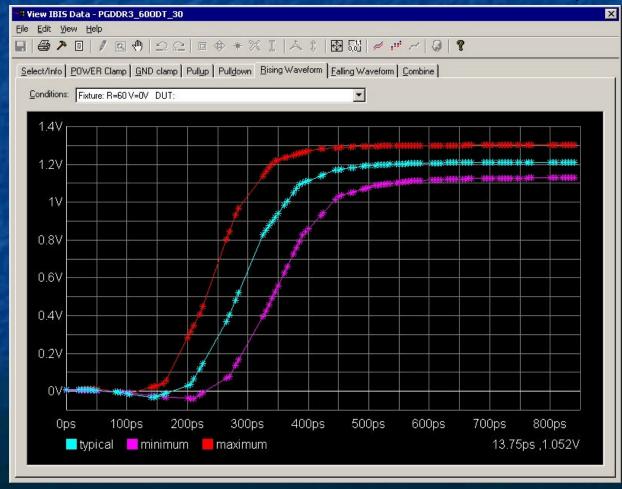

#### Example VT Curve

VT curve time small versus data rate (Final DC levels ~ 3.5ns)

1 of 4 VT curves shown (Rise, Fall, VDD, Ground) ~ 1ns Delta

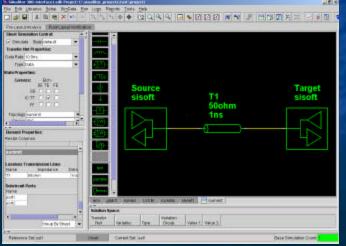

## **Example Simulation**

Simulation results 100 MHz (10ns Cycle time, 5 ns Data rate)

SiSoff

#### **Over Clocked Case – VT Before**

#### • VT curve time comparable to data rate

#### - Large delta between beginning of Fast and end of Slow Process corners ~.7ns

#### SiSofi

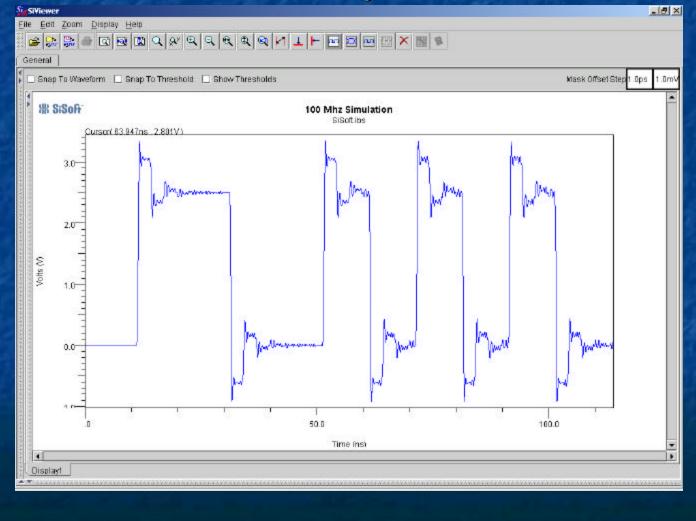

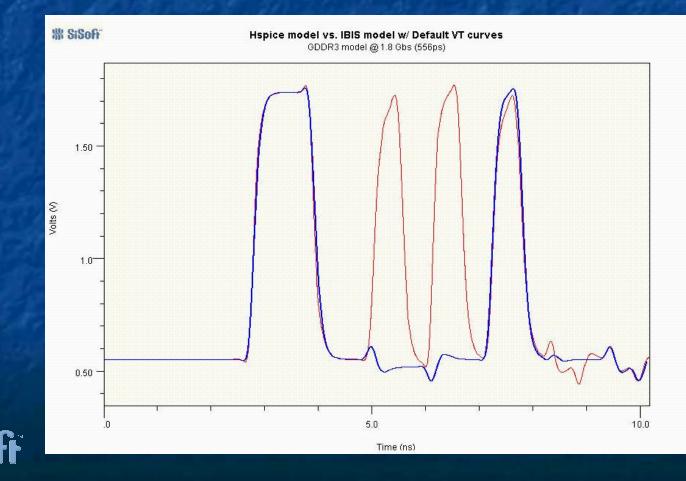

#### **Over Clocked Case – Simulation Before**

- Hspice versus IBIS Correlation

- Simulation results 1.8 GHz (0.556 ns Data rate)

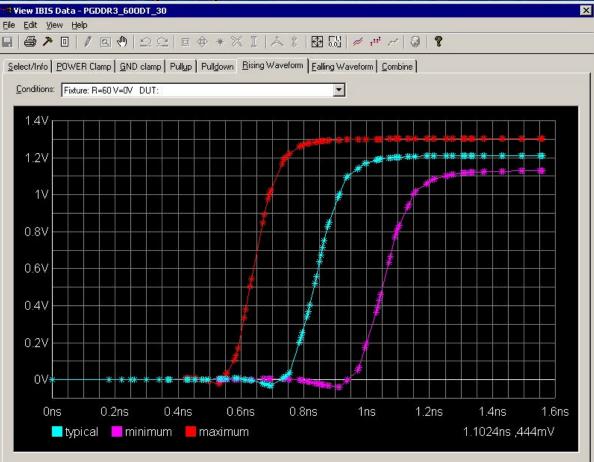

#### **Over Clocked Case – VT After**

#### VT curve time Shifted

- Reduce delta between Fast and Slow Process corners (~ 450ps)

## SiSoff

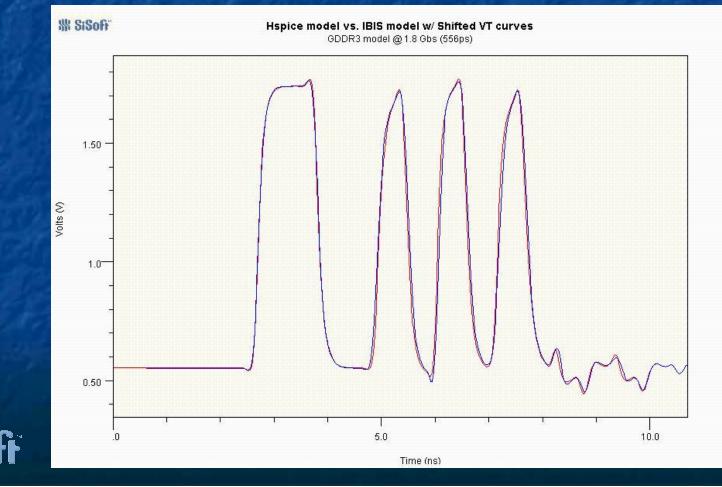

## **Over Clocked Case – Simulation After**

Hspice versus IBIS Correlation

SiS

Simulation results 1.8 GHz (0.556 ns Data rate)

#### SiSoft Implementation

- Implemented parameter (in .ibs file)

- SiSoft uses "|Sisoft" parameters to augment IBIS capabilities

- "|" character is a comment character for IBIS

- Industry tools will ignore

- SiSoft is Keyword in SiAuditor / Quantum SI

- SiSoft parameter used

- SPICE2IBIS processing

- |SiSoft VT\_offset typ, min, max

- Lost FF to SS timing relationship

- Comment in .ibs file to document

#### SiSoff