# Modeling the Radiated Emission of Micro-controllers

**Etienne Sicard**

etienne.sicard@insa-tlse.fr

http://intrage.insa-tlse.fr/~etienne

Christian MAROT

**Etienne SICARD**

### Contents

- 1. Context of the study

- 2. System design methodology for EMC

- 3. The IERSET project on EMC for ICs

- 4. Core emission model

- 5. Emission model with los

- 6. Emission model in TEM cell

- 7. Conclusion

### 1. Context of the study

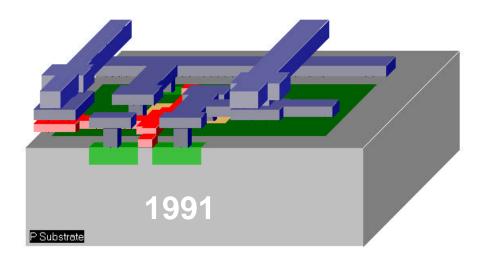

0.7µm, 2 metal layers

Up to 100,000 devices on a chip

CPU frequency 50MHz

○ 0.12µm, 6 metal

○ Up to 200,000,000 devices

○ CPU frequency 1GHz

10 years of evolution

### **1. Context of the study**

## **1. Context of the study**

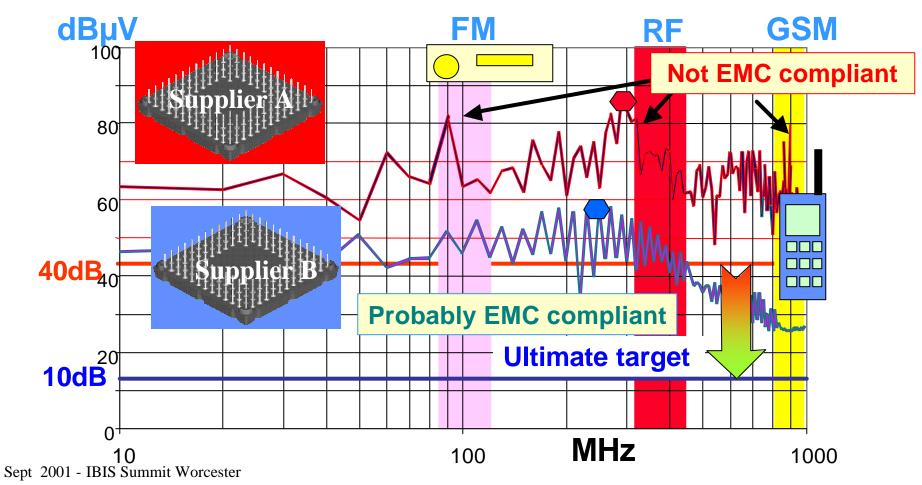

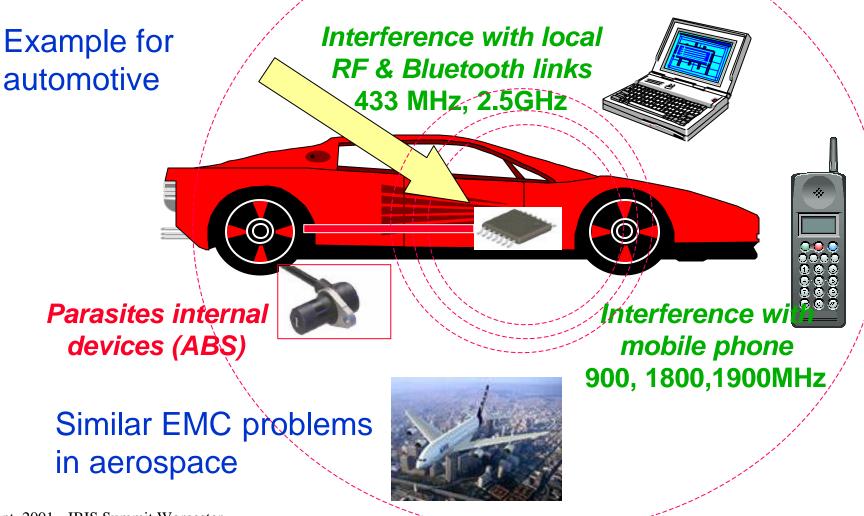

#### Low parasitic emission is a key argument

SUR LES SYSTEMES ELECTRONIQUES POUR LES TRANSPORTS

## 1. Context of the study

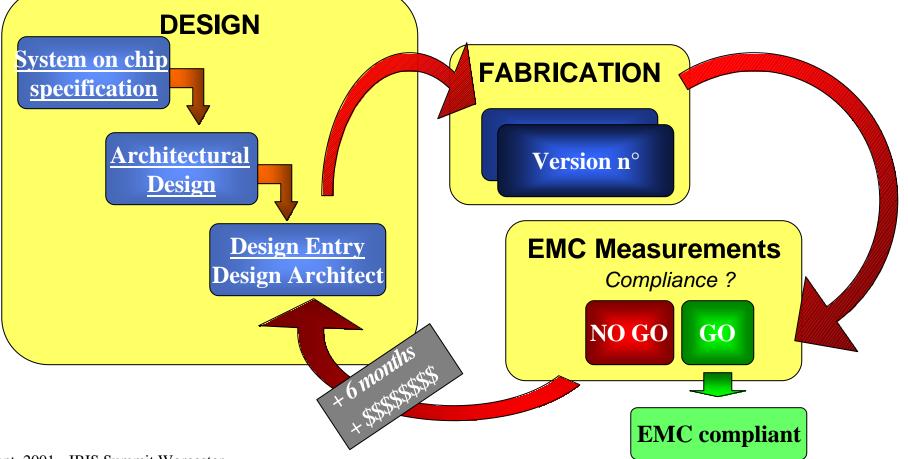

#### **Obsolete Design Methodology**

#### **Obsolete Design Methodology**

PCB design

dB peaks

Prototype board

**EMC** scan

Electromagnetic incompatibility found too late

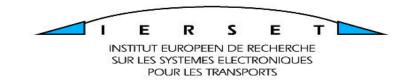

#### Target Design Methodology

(

#### Target Design Methodology

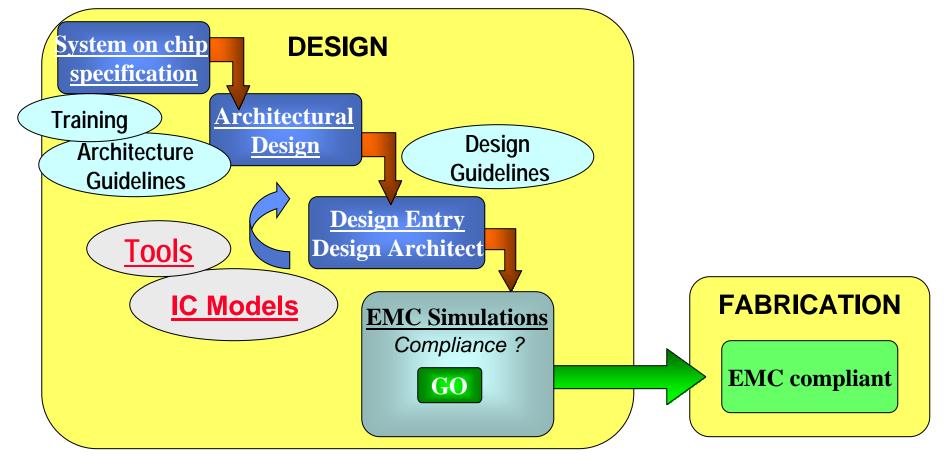

A core model is mandatory for accurate emission prediction

#### 2. The IERSET project

European Research Centre on Electronics for Transportation identifies and co-ordinate co-operative research.

#### **Objectives**

- Definition and validation of a model to be used in PCB CAD tools to guarantee the EMC of electronic systems

- One model from 1MHz to 1GHz, for conducted *and* radiated emission

# 2. The IERSET project

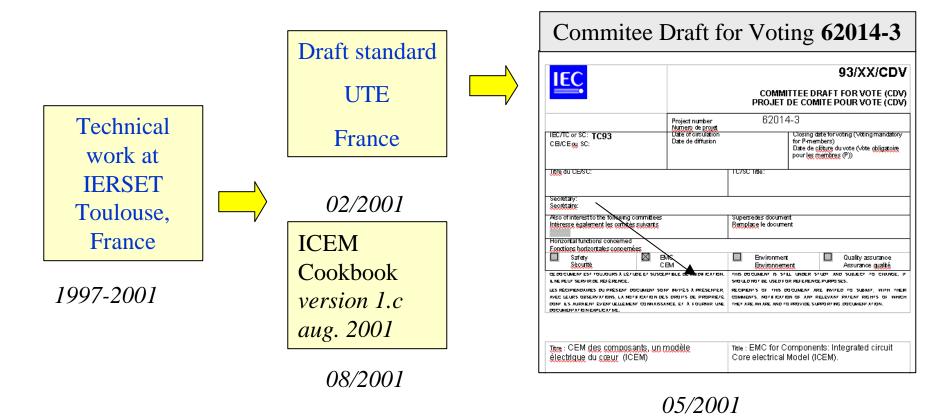

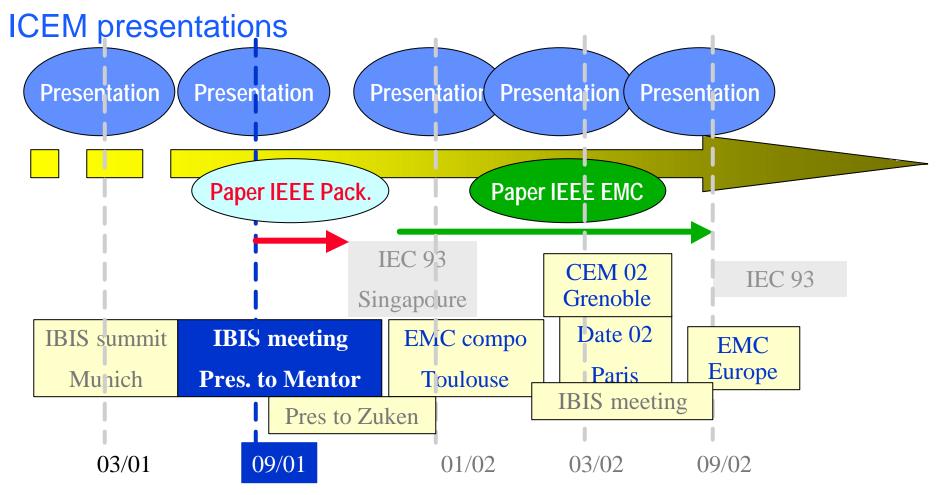

#### ICEM (Integrated Circuit Electromagnetic compatibility Model)

## 2. The IERSET project

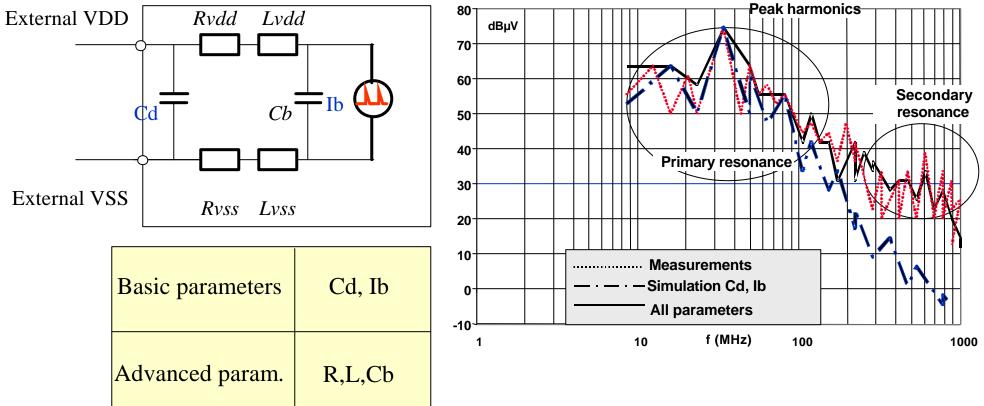

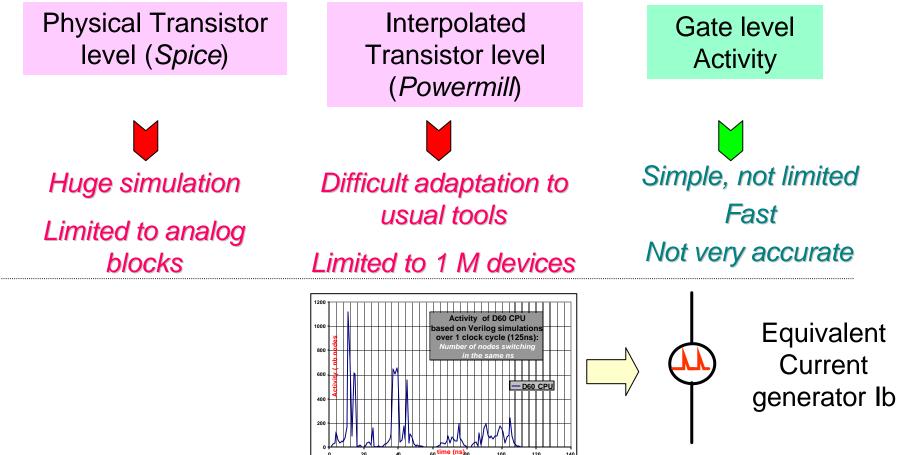

## **4. Core Emission Model**

#### ICEM includes a simple core model, not handled by IBIS

Sept 2001 - IBIS Summit Worcester

## **4. Core Emission Model**

Current generator estimation

## **5. Emission Model with IOs**

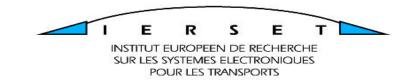

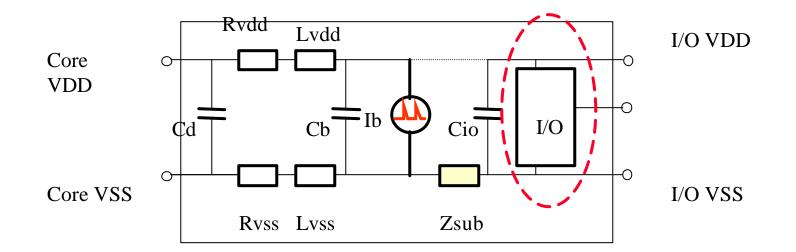

#### Validation for a 16 bit micro-controller

Comparison between simulation and measurement on a 16 bit micro-controller

## **5. Emission Model with IOs**

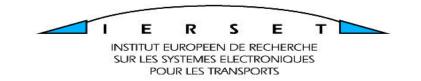

#### Add IBIS I/O data

Zsub: basically a 1-10Ω serial resistance Cio : decoupling capacitance for IO supply IO block: reuse of IBIS

## **5. Emission Model with IOs**

IO modify the spectrum at high frequencies (>300MHz)

Validation

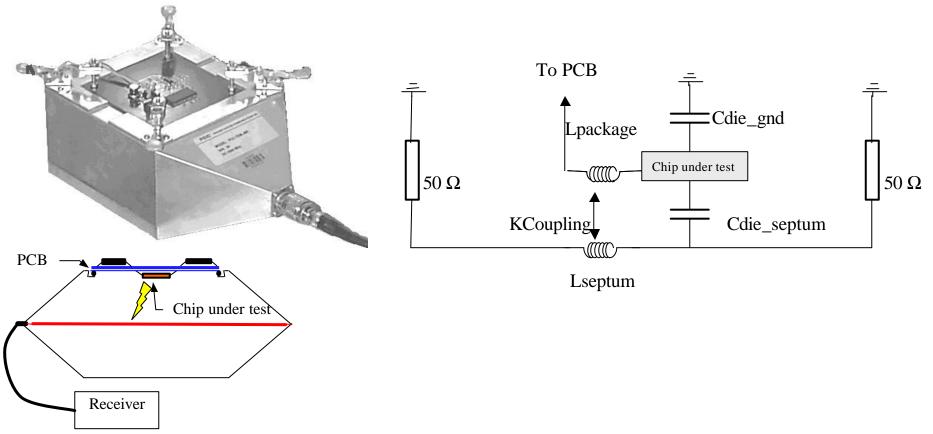

## 6. Emission in TEM cell

#### Proposed model: capacitance & inductance coupling

## 6. Emission in TEM cell

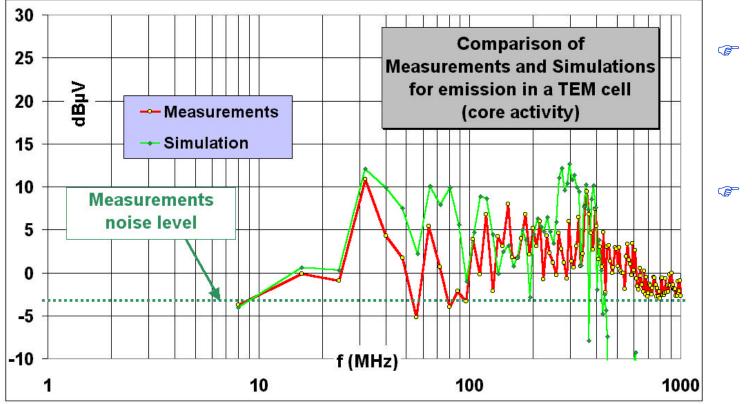

#### Validation for the core alone

Model fits

correctly up to

400MHz

At high

frequencies,

close from

noise floor

## 6. Emission in TEM cell

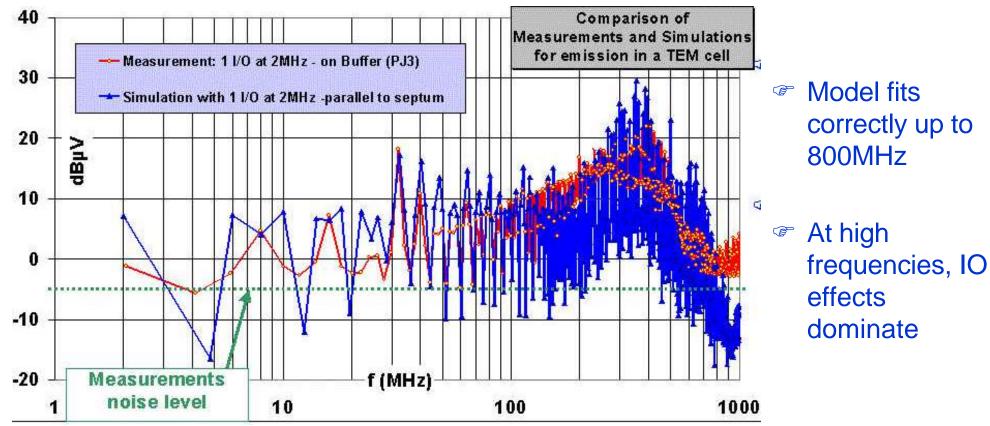

#### Validation for the core & IOs

## Conclusion

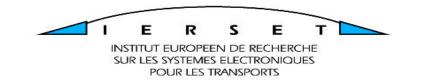

- Technology scale down illustrated

- More complex chips increase parasitic emission

- An EMC model for Ics is mandatory

- A simple model has been proposed

- Satisfactory prediction of conducted emission

- Prediction of the core emission in TEM investigated

- Model proposal standardized by UTE (ICEM)

- Presentation and promotion to CAD & IC providers