## Some Results for General K-table Extraction Proposal Using SPICE

Bob Ross, Teraspeed Labs bob@teraspeedlabs.com Xuefeng Chen, Synopsys xfchen@synospsys.com

> EPEPS IBIS Summit San Jose, California October 28, 2015

(From material originally presented January 30, 2015)

### **Updated Material**

- More derivation detail: January 30, 2015, "General K-Table Extraction Proposal Using SPICE"

- http://www.ibis.org/summits/jan15/ross2.pdf

- Contains Summit references

- Some results and other observations here

- Purpose Use SPICE for PROTOTYPING IBIS extraction algorithms (with general C\_comp, on-die, package structures and fixture loads)

#### Overview

- Fixed C\_comp to local GND for extraction

- Detailed C\_comp model from S-parameters or IBIS-ISS allowed

- IBIS Interconnect BIRD proposal adds on-die and package models

- SPICE-based extraction proposal supports total path measurement with more detailed C\_comp/ondie/package structures

- Limitations exist

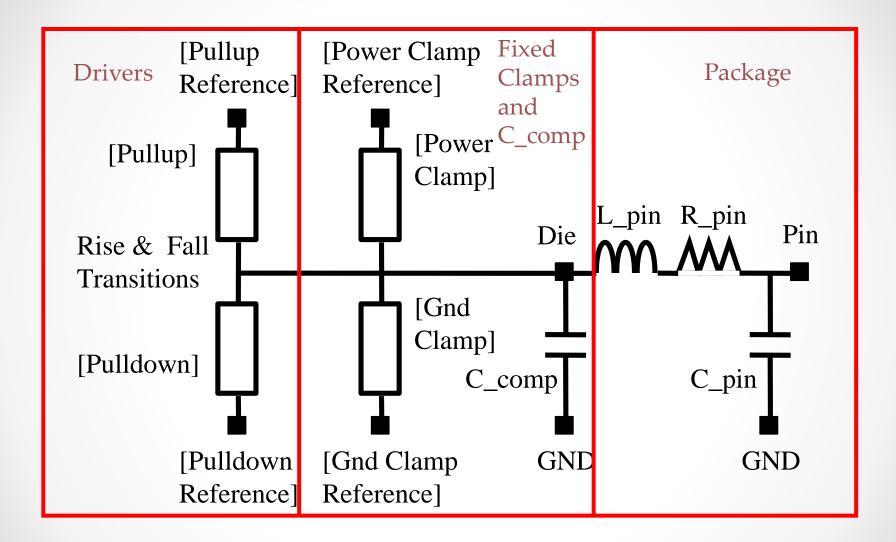

### Standard IBIS Model

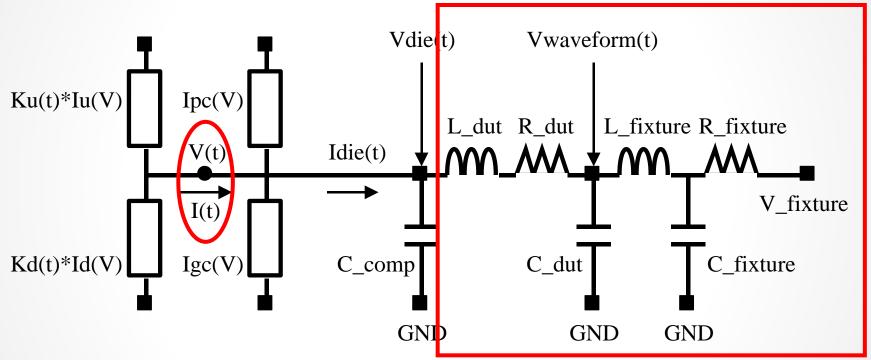

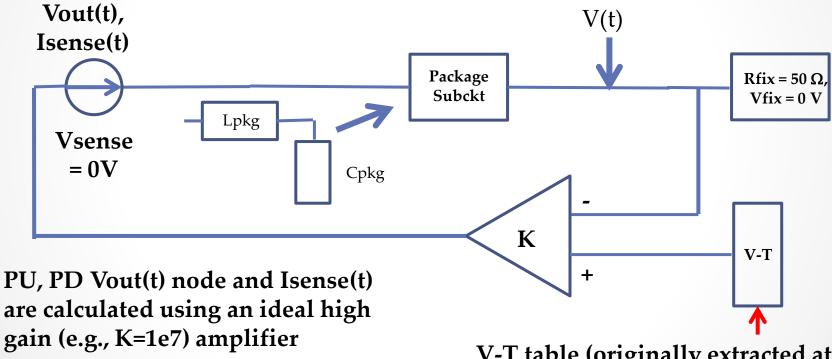

# Generalized V-T Extraction Load (with L/R/C\_dut)

Calculate V(t) and I(t) from load information

### Direct V(t), I(t) Solution

- Xuefeng Chen, Asian IBIS Summit (China),

September 11, 2007: V(t), I(t) extracted directly for L/R/C/V\_fixture by applying i=C\*dv(t)/dt and v=L\*di(t)/dt

- Extension can include L/R/C\_dut (where L/R/C\_dut replaces the L/R/C\_pin values for the measured pin)

- Ku(t) and Kd(t) tables extracted using the 2equations/2-unknowns (2EQ/2UK) method (later)

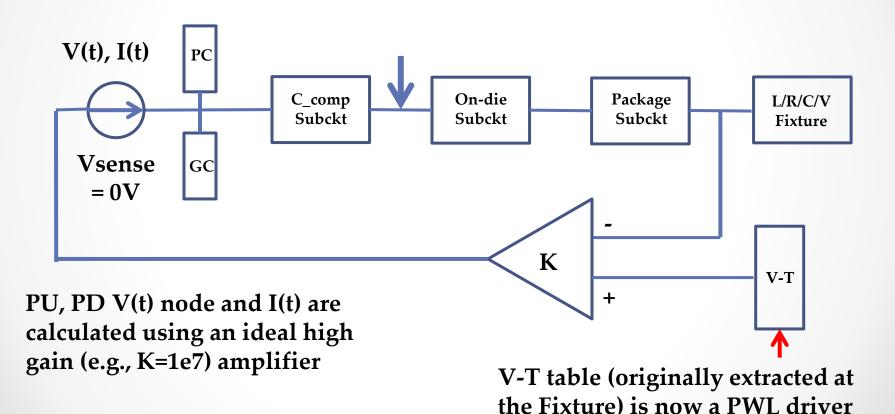

### Indirect Feedback Solution Next

- Avoids encoding equations for complex structures

- Calculates K-tables with high-gain (e.g., 1E7) feedback loop multiplier

- Kur(t), Kdr(t) from two rising V-T waveforms and fixtures

- Kuf(t), Kdf(t) from two falling V-T waveforms and fixtures

- Calculated and specified responses converge

- Requires vendor-specific SPICEs (versus IBIS-ISS)

- Tables

- Feedback loop issues with tables

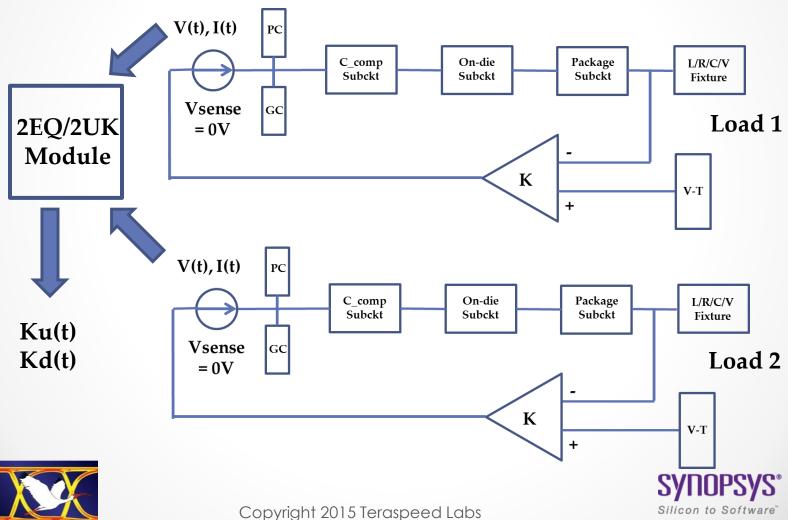

## Partial SPICE Circuit Showing 2EQ/2UK K-Table Extraction

```

*

FEEDBACK TABLE ADJUSTMENT

CUR='(I(VDN2)*I(VUP1)-I(VDN1)*I(VUP2))/

GDET

NDET

VDET

NDET

GND

GKUR

NKU

GND

(PIN2D *I(VDN1)-V(IN1)-V(PIND) *I(VDN2))/I(VDET)'

VKUR

NKU

GND

Kur

*

GKDR

GND

NKD

(⟨V (IN1) -V (PIN1)) *I (VUP2) - ⟨V (IN2) -V (PIN2) *I (VUP1)) /I (VDET) '

VKDR

NKD

GND

Kdr

*

```

$$I_{I}(t) = Ku(t)*Iu(V_{I}(t)) + Kd(t)*Id(V_{I}(t))$$

$$I_2(t) = Ku(t)*Iu(V_2(t)) + Kd(t)*Id(V_2(t))$$

### SPICE Encoding

- I-V tables: G elements (VCCS)

- V-T tables: PWL voltage sources

- Voltage rails: Entered

- SPICE interpolation

- Allows higher resolution time steps in V-T tables

- Interpolates G table currents

- I-V and V-T tables extended from final values

- Convergence criteria adjustable

- K-tables printed for Kur(t), Kdr(t); Kuf(t), Kdf(t)

- Simulation done with K-table drivers:

- G elements for K-tables

- Scaled controlled ramp (1V/nS)

- Step stimuli (0 to 1, 1 to 0)

## Part of SPICE Encoded IBIS Prototype for Simulation

```

* HIGH SIDE

OUT1

VCC

XUP

NU1

PULLUP

VUP

NU1

VCC

()

(I(VKUR)*I(VON)+I(VKUF)*(1-I(VON)))'

VCC

CUR='-I(VUP)

GUP

OUT1

POWER CLAMP

VCC

XPC

OUT1

Kur, Kdr

Kuf, Kdf

* LOW SIDE

XDN

PULLDOWN

OUT1

GRD

ND1

GRD

0

VDN

ND1

CUR='-I(VDN)^*(I(VKDR)*I(VON)+I(VKDF)*(1-I(VON)))'

OUT1

GRD

GDN

XGC

OUT1

GNDC

GND CLAMP

*

* C COMP AND DUT PACKAGE

Table switching control

XCAP

OUT1

GRD

C COMP

PACKAGE

OUT1

GRD

XPKG

PTN1

* LOAD

PTN1

GRD

PTN9

GRD

Z0=50 TD=1N

TLOAD

Enter simulation load

PIN9

50G

RLOAD

GND

* VOLTAGE CONTROL

(AMPLITUDE (0 TO 1), PULSE WIDTH & PERIOD)

VPULSE STEP

GRD

PULSE (1 0 OP 1P 1P 5N 10N)

```

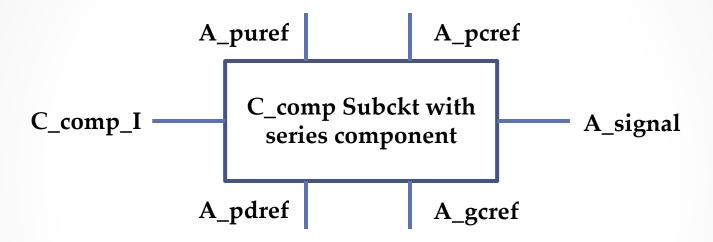

## General Proposed Single-ended C\_comp Subckt Model

- (Notation and details under development)

- C\_comp\_I: If needed for series path

- Resistance needs to be de-embedded from I-V tables

- A\_signal: Output

- Extend model for differential connections

# SPICE Extraction of V(t), I(t) Setup and C\_comp A\_signal Node

## 2EQ/2UK SPICE Setup to Generate Ku(t), Kd(t) Tables

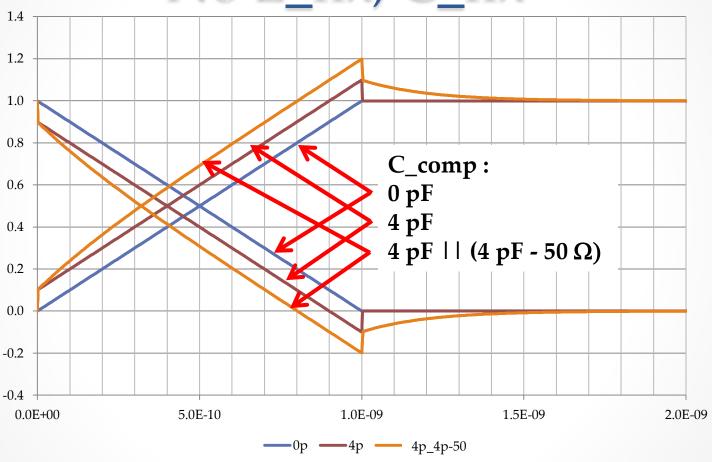

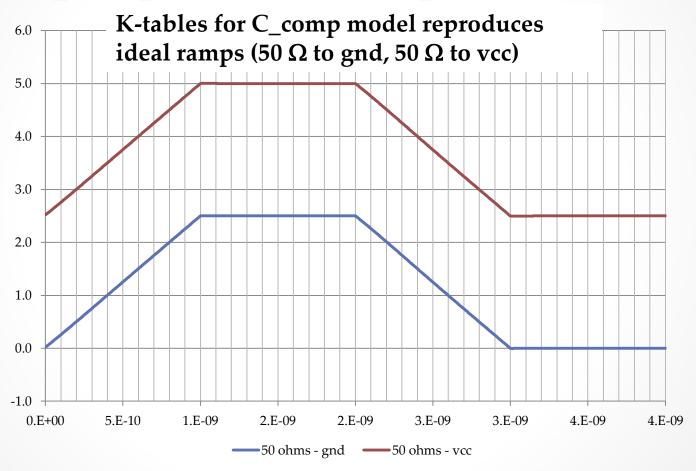

### Ideal Ramp Test Cases

- Reference Waveforms

- $\circ$  1 ns ramp (0% to 100%) into 50  $\Omega$ -to-gnd and 50  $\Omega$ -to-vcc loads

- o 5 V supply

- 2 ns duration

- C\_comp cases

0 pF4 pF(0p)(4p)

$\circ$  4 pF | | (4 pF - 50  $\Omega$ ) (4p\_4p-50)

- Pullup/Pulldown I-V tables

- $\circ$  50  $\Omega$  straight lines

- 1001 point extractions (not critical)

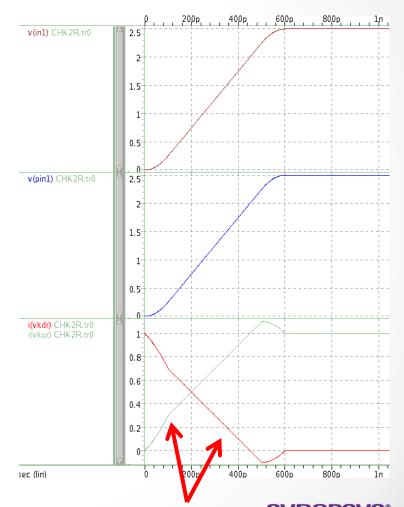

### K-tables Shapes Versus Time (s)

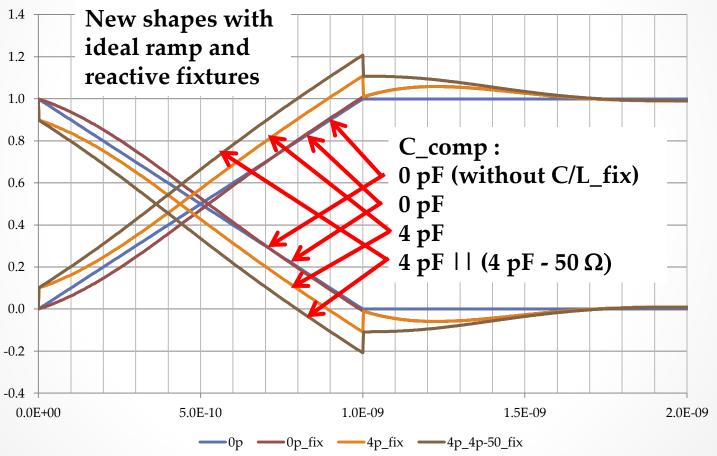

# K-tables Versus Time (s) – With L\_fix=10 nH, C\_fix=4 pF Fixtures

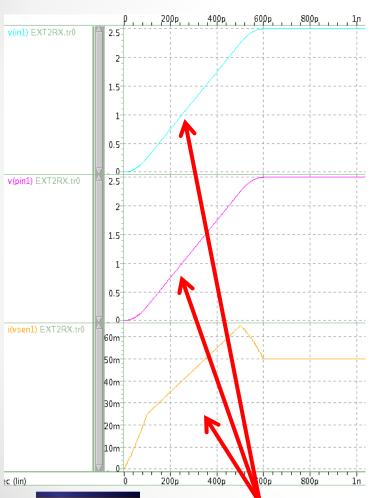

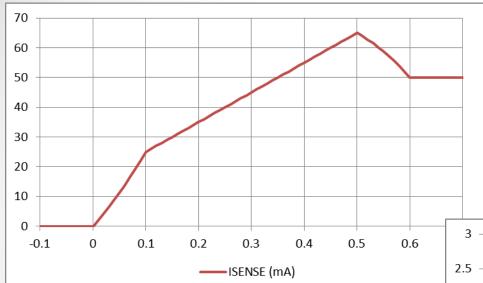

# 4 ns Cycle Simulations for 4p\_4p-50 C\_comp Model

## Test Case <u>Notation Change</u> for Vout(t) & Isense(t); Given V(t)

No C\_comp, no clamps, just a Package model which could be a C\_comp model or an on-die model

V-T table (originally extracted at the Fixture) is now a PWL driver

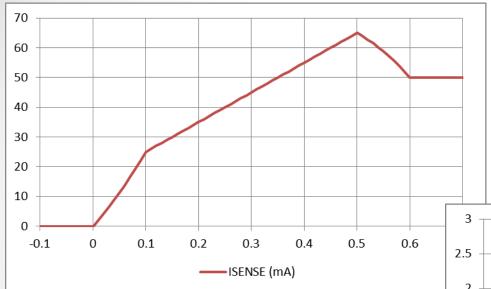

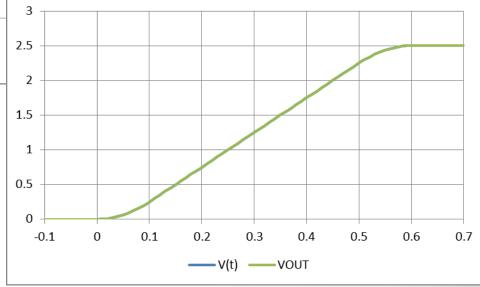

## Lpkg = 0 nH, Cpkg = 0.004 nF

Closed-form references (50  $\Omega$  to GND)

Continuous V(t) and dV(t)/dt

### Extractions using Laplace Element

Same as closed-form references

Copyright 2015 Teraspeed Labs

K-tables

SYIIUPSYS

Silicon to Software

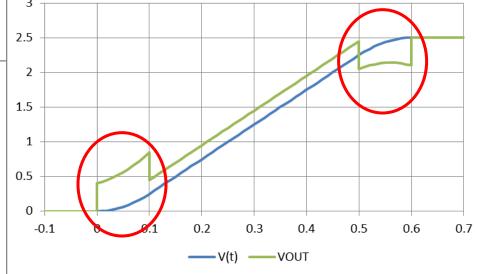

## Lpkg = 2 nH, Cpkg = 0.004 nF

**VOUT discontinuities:** Feedback loop fails

Closed-form references (50  $\Omega$  to GND)

### Observations and Conclusions

- Result accuracy

- K-table extraction insensitive to K=1e5 to K=1e9 feedback multipliers

- Requires SPICE maximum accuracy settings

- Not sensitive to number of extraction points

- Severe test cases

- Sharp waveform derivative discontinuity in ideal ramp

- Large C\_comp model load can be used

- Large L\_fixture, C\_fixture reactive loads are ok

- BOTH L\_pkg, and C\_pkg do not converge (even with smooth waveforms) – therefore topology limited and must use tooldependent methods

- Fails for T-line models (delay in feedback loop)

- Works for S-parameter, Laplace transform, lumped models