# System-Level Timing Closure Using IBIS Models

Barry Katz

President/CTO, SiSoft

Asian IBIS Summit

# **Agenda**

- High Speed System Design

- Establishing timing model

- Derivation of timing equations

- Idealized timing analysis

- The role of signal integrity

- Reconciling signal integrity with timing

- Pre-route exploration

- Driving physical design

- Post-route validation

- Design analysis reuse

- Case study: DDR2 memory

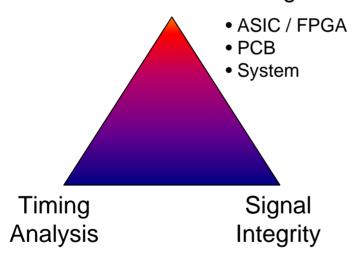

# High Speed System Design ... Not Just "Signal Integrity"

#### Constraint-Driven Design

- High Speed Design involves multiple disciplines

- Changes in any area drive changes in others

- Mastery of modeling details & process flow is <u>essential</u> for success

# **System Level Timing Closure**

- Successful high speed design requires a rigorous methodology for ensuring positive design margin across all combinations of:

- Component timing (process)

- Voltage & temperature

- Package & PCB routing lengths

- PCB manufacturing variations ( $Z_0$ , loss)

# **Establishing Timing Budgets**

- High speed interfaces have one or more "transactions" that require timing closure

- Memory example:

- Address/control

- Data read

- Data write

- Strobe to Clock

- Timing relationships must be identified and closed for each different transaction

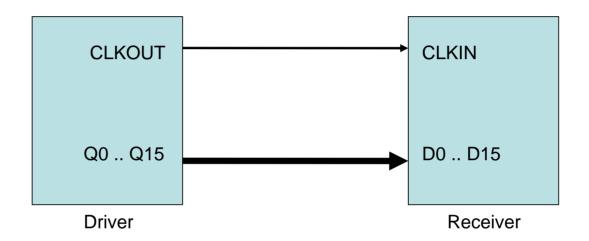

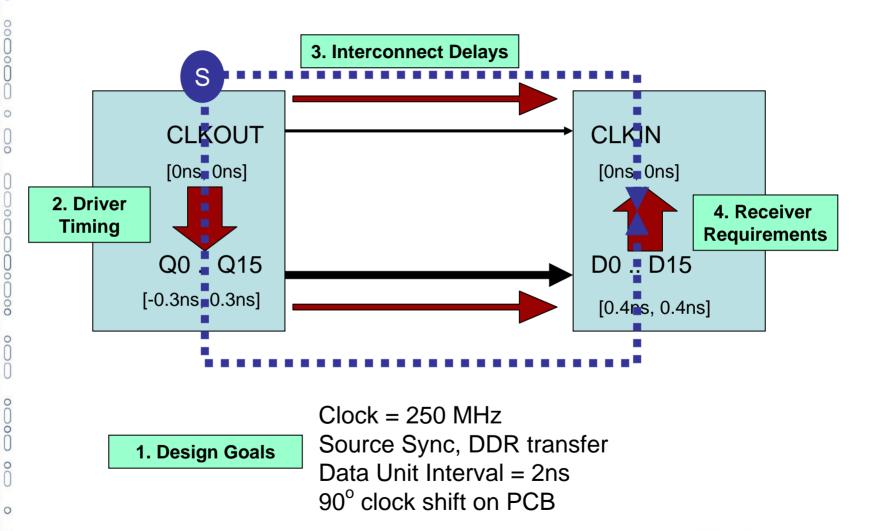

# **Source-Sync Transaction Example**

- Establish component timing & transfer protocol

- Derive timing equations

- Idealized timing analysis

- Signal integrity analysis and Timing Closure

#### **Component Timing, Transfer Protocol**

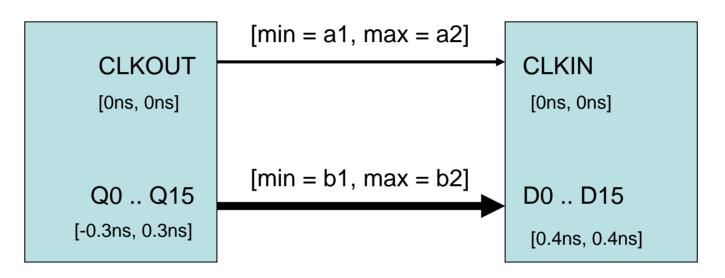

# **Derive Timing Equations**

```

Setup margin = [early clock] – [late data] – [setup requirement]

= [0ns + a1] - [0.3ns + b2] - [0.4ns]

= a1 - b2 - 0.7ns

```

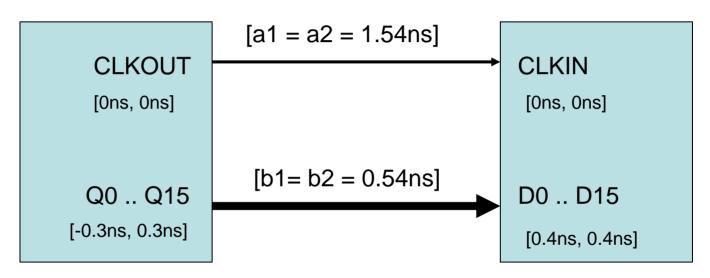

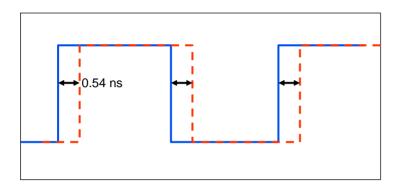

# **Idealized Timing Analysis**

Minimum data length = 3", at 180ps/in = 0.54ns

Setup margin =

$$a1 - b2 - 0.7ns$$

=  $1.54ns - 0.54ns - 0.7ns$

=  $0.3 ns$

# The Role of Signal Integrity

**Idealized Delays**

Real-World Delays

- Detailed analysis of digital switching behavior

- IBIS or HSpice models define I/O buffer behavior

- Accounts for

- Actual circuit loading

- Reflections / ringing

- Circuit topology

- Inter-symbol interference

- Switching thresholds

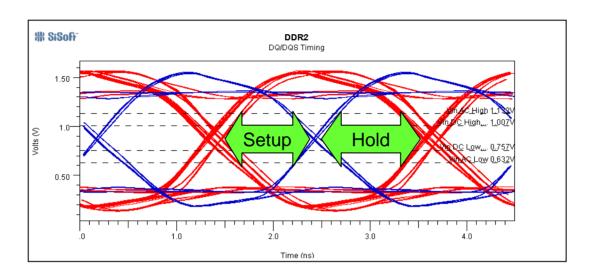

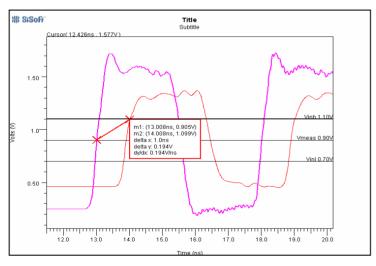

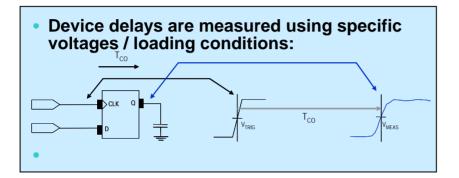

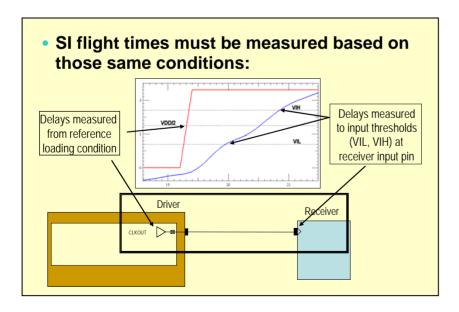

# **Reconciling SI with Timing**

- Static timing and signal integrity measurements <u>must</u> be compatible

- SI measurements are "normalized" to conditions under which loading is specified

- IBIS Vref, Cref, Rref, Vmeas

- Timing Closure occurs when integrated timing/SI results show acceptable setup/hold margins

#### **Building an Executable Timing Model**

- For each interface, all transactions must be validated for all cases:

- Component timing (process)

- Voltage, temperature

- PCB variations

- Creating an executable timing model to perform automatic regression is ideal

- Possibilities

- Excel

- Custom scripting

- EDA tools

$$t_{\text{cycle}} = t_{\text{co}} + t_{\text{final settling}} + t_{\text{setup}} + t_{\text{skew}} + t_{\text{jitter}} + t_{\text{SSO}} + t_{\text{ISI}}$$

### **Pre-Route SI Exploration**

- Pre-route simulations model planned

- Drivers

- Receivers

- Routing topology & lengths

- Termination

- Simulated interconnect delays are extracted and plugged back into the Executable Timing Model

- Setup and hold margins are calculated for temperature, process and voltage corners

Asian IBIS Summit - Shanghai, China - October 27, 2006

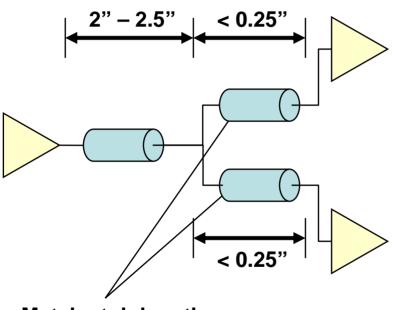

# **Driving Physical Design**

Match stub lengths to within 0.2"

- Pre-route SI/Timing analysis defines PCB routing rules

- Rules usually include pin ordering, length limits and stub matching

- Driving automated rules into PCB CAD is essential

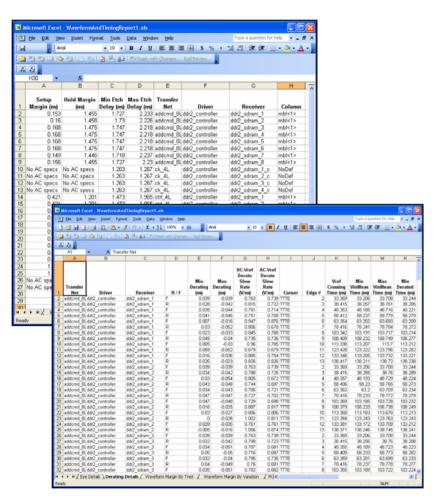

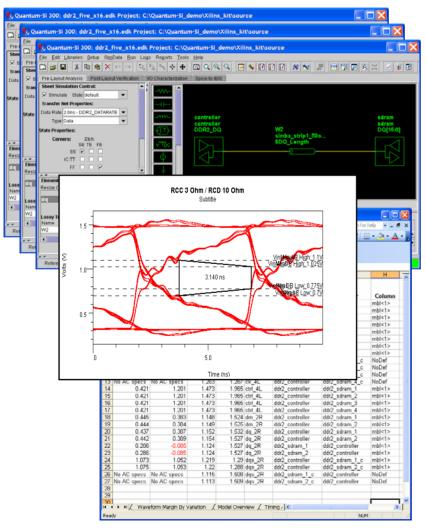

#### **Post-Route Validation**

- Routed topologies are extracted from PCB database and simulated

- Simulated interconnect delays are extracted and plugged back into system timing model

- Setup and hold margins are calculated for temperature, process and voltage corners

7. 2006

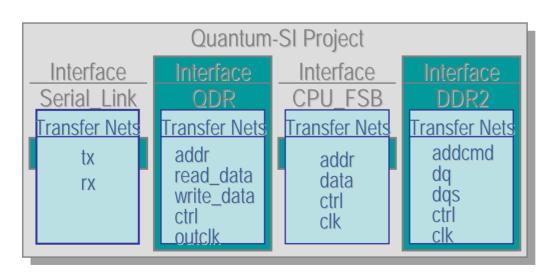

# **Design Analysis Reuse**

Once all the SI/timing data for an interface has been captured, it should be possible to directly reuse that information for multiple instances in a project or other projects

Each interface kit contains net class schematics, timing data & SI models

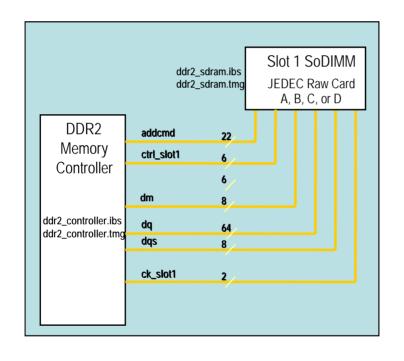

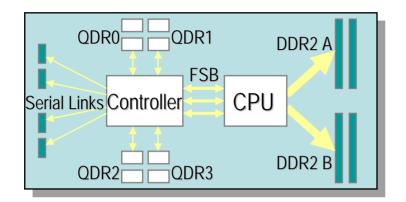

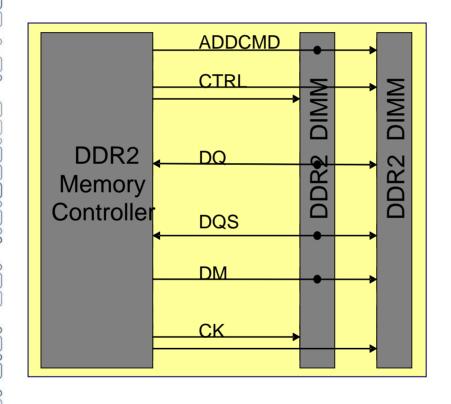

#### Case Study: DDR2 System Memory

- DDR2 supports one or two DIMM modules

- DIMM Modules

- Registered and Unbuffered

- 4 to 18 memory devices

- Two module, data write transaction is presented here

- Complete case study:

"Features and Implementation of High-Performance 667Mbs and 800Mbs DDRII Memory Systems"

- Presented by Micron & SiSoft

- DesignCon West, 2005

- http://www.sisoft.com/papers.asp

# **DDR2 Data Write Configuration**

| Write Configurations |          |                           |                |           |                |           |  |

|----------------------|----------|---------------------------|----------------|-----------|----------------|-----------|--|

| Configuration        | Write to | DQ Active-Term Resistance |                |           |                |           |  |

|                      |          | Controller                | Dram at Slot 1 |           | Dram at Slot 2 |           |  |

|                      |          |                           | Front Side     | Back Side | Front Side     | Back Side |  |

| 2R / 2R              | Slot 1   | No Term                   | No Term        | No Term   | 50 or 75 ohm   | No Term   |  |

| 211 / 211            | Slot 2   | No Term                   | 50 or 75 ohm   | No Term   | No Term        | No Term   |  |

| 2R / 1R              | Slot 1   | No Term                   | No Term        | No Term   | 50 or 75 ohm   | Empty     |  |

|                      | Slot 2   | No Term                   | 50 or 75 ohm   | No Term   | No Term        | Empty     |  |

| 1R / 2R              | Slot 1   | No Term                   | No Term        | Empty     | 50 or 75 ohm   | No Term   |  |

|                      | Slot 2   | No Term                   | 50 or 75 ohm   | Empty     | No Term        | No Term   |  |

| 1R / 1R              | Slot 1   | No Term                   | No Term        | Empty     | 50 or 75 ohm   | Empty     |  |

| IN/IN                | Slot 2   | No Term                   | 50 or 75 ohm   | Empty     | No Term        | Empty     |  |

| 2R / Empty           | Slot 1   | No Term                   | 150 ohm        | No Term   | Empty          | Empty     |  |

| Empty / 2R           | Slot 2   | No Term                   | Empty          | Empty     | 150 ohm        | No Term   |  |

| 1R / Empty           | Slot 1   | No Term                   | 150 ohm        | Empty     | Empty          | Empty     |  |

| Empty / 1R           | Slot 2   | No Term                   | Empty          | Empty     | 150 ohm        | Empty     |  |

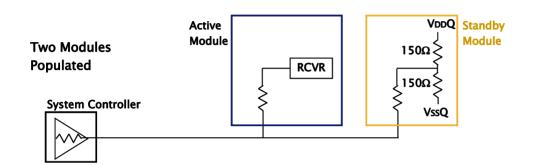

- Termination strategy is dynamic; depends on how many DIMMs are present and which device is receiving

- Simulation

environment must

switch receiver

models based on

which case is being

analyzed

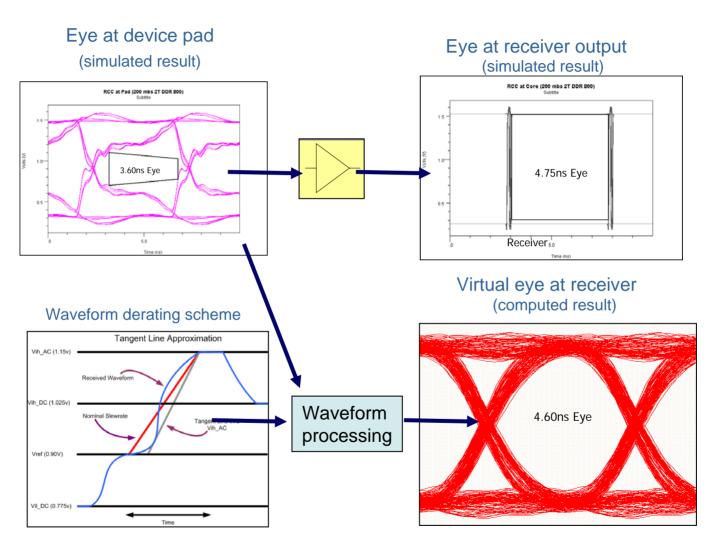

# Slew Rate Derating – "Virtual Eye"

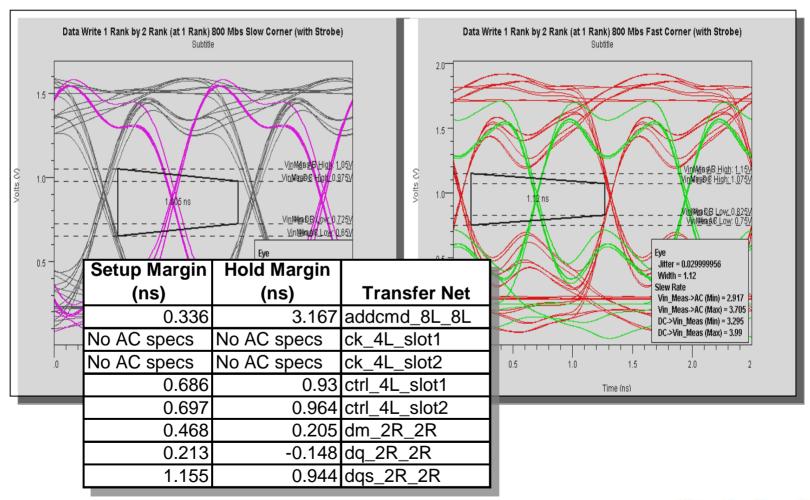

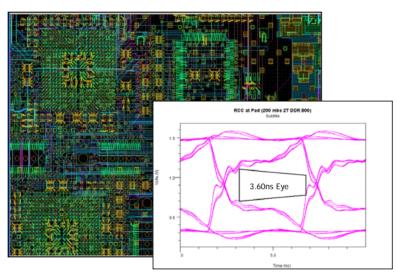

# DDR2 Analysis Results Data Write Slow / Fast Corners

0000

### **Summary**

| Setup Margin | Hold Margin |               |

|--------------|-------------|---------------|

| (ns)         | (ns)        | Transfer Net  |

| 0.336        | 3.167       | addcmd_8L_8L  |

| No AC specs  | No AC specs | ck_4L_slot1   |

| No AC specs  | No AC specs | ck_4L_slot2   |

| 0.686        | 0.93        | ctrl_4L_slot1 |

| 0.697        | 0.964       | ctrl_4L_slot2 |

| 0.468        | 0.205       | dm_2R_2R      |

| 0.213        | -0.148      | dq_2R_2R      |

| 1.155        | 0.944       | dqs_2R_2R     |

- High-speed system design requires a rigorous, repeatable methodology for achieving Timing Closure

- Static Timing, Signal Integrity, and physical design rules are all interrelated

- An Executable Timing Model allows for a user to validate all transactions across all cases

- Signal Integrity analysis must be performed in accordance with the system timing model