Ken Willis - Cadence Design Systems Asian IBIS Summit, Shanghai, PRC November 13, 2017

#### Overview

- In writing EDI CON paper "Signal Integrity Methodology for Double-Digit Multi-Gigabit Interfaces", different IBIS modeling techniques were applied

- Wanted to share some of the IBIS modeling methods we've been using

- [External Model]

- AMI equalization adaptation

- Backchannel training

- Applying IBIS-AMI to DDR applications

- [External Model]

- AMI equalization adaptation

- Backchannel training

- Applying IBIS-AMI to DDR applications

#### **Preliminary IBIS Modeling**

- Can get started with:

- Voltage swing

- Pad capacitance

- Output impedance

- Rise time

- Even easier to model using [External Model] syntax

```

[Model]

pcie4 out

Model type Output

Polarity Non-Inverting

| variable

max

typ

0.50pF

0.50pF

0.50pF

C comp

-50

[Temperature Range]

1.0

[Voltage range]

[Pulldown]

Voltage

I(typ)

I(min)

I (max)

-1.0000e+00

-2.0000e-02 -2.0000e-02 -2.0000e-02

0.0000e-00

1.0000e+00

2.0000e-02 2.0000e-02 2.0000e-02

[Pullup]

Voltage

I(typ)

I(min)

I (max)

-1.0000e+00

2.0000e-02 2.0000e-02 2.0000e-02

0.0000e-00

-2.0000e-02 -2.0000e-02 -2.0000e-02

[Ramp]

| variable

max

dV/dt r

0.60/0.020n

0.60/0.020n

0.60/0.020n

dV/dt f

0.60/0.020n

0.60/0.020n

0.60/0.020n

R load = 50

```

#### **External Model**

- Originally introduced in IBIS 4.1!

- Enabled VHDL, Verilog-A, and Spice syntax to be used for buffer models instead of VI/VT table syntax

- Spice syntax has proven very useful to us

```

D:\kenw\Working\sla_test\sla_example_em.ibs - Notepad++

File Edit Search View Encoding Language Settings Tools Macro Run Plugins Window ?

`a 😝 🗎 🖫 😘 😘 🛦 | ¼ 🖍 🖍 🕽 🗷 el 🐞 🗽 | 🤏 👒 | 🖎 🖫 📠 🗂 🖫 🐷 🔊 🔊 💿 💿 🕟 🕟 🖼

| Example SerDes Rx [External Model] using SPICE:

64

65

[Model] sla in em

66 Model type Input

67 Vinl=0.4

69

71 [Voltage Range]

[External Model]

75

Language SPICE

rx spice simple.sp rx single50

rx spice simple.sp rx single36

83 | Ports List of port names (in same order as in SPICE)

84 Ports A pcref A gcref A signal my receive

86 | A to D d port

vhigh corner name

87 A to D D receive my receive

-400m

600m Typ

A_to_D D_receive my_receive

89

A to D D receive my receive

90

91 [End External Model]

92

93 [Algorithmic Model]

94 Executable Windows_VisualStudio10.0.30319_32 amirx.dll amirx.ami

95 Executable Windows VisualStudio10.0.30319 64 amirx.dll amirx.ami

96 Executable Linux gcc4.1.2 64 amirx.dll amirx.ami

97 [End Algorithmic Model]

98

Normal text file

Unix (LF)

UTF-8

length: 5,777 lines: 149

Ln:1 Col:1 Sel:0|0

```

# Spice [External Model]s Convenient for Early Feasibility

- Sometimes the IBIS model you want is not available for preliminary / pre-design analysis

- Easy to write (or use) simple parameterized Spice subcircuits for IO buffers when IBIS availability does not align with your project schedule

- Can sweep parameters and cover a big portion of the design space quickly and easily

```

- - X

D:\kenw\Working\sla_test\rx_spice_simple.sp - Notepad++

File Edit Search View Encoding Language Settings Tools Macro Run Plugins Window ?

le_em.ibs 🗵 🗎 rx_spice_simple.sp 🗵

subckt rx single 0 pwr ngnd pos outof rx

+ r pwr=1e08

+ rx c comp=0.1p

* Developed by Cadence using SystemS:

* This is an example Rx circuit model

* This model takes the following parameters:

* rx rt > pullup termination

c1 pos ngnd 'rx c comp

r2 pos outof rx 1e-06

.ends rx single50

length: 2,913 lines: 107

Ln:1 Col:24 Sel:0|0

Unix (LF)

```

#### **Analog Buffer Model Extensions**

Incorporated into IBIS 6.0

```

[External Model]

Language IBIS-ISS

| Corner corner name file name circuit name (.subckt name)

Corner

Typ

cdnstxrx.cir

tx subckt

| List of parameters

Parameters TSFile1

= cdns tx.param(CDNS Tx(Model Specific(Tstonefile)))

Parameters Tx Rseries

= cdns tx.param(CDNS Tx(Model Specific(Tx R)))

| List of converter parameters

Converter Parameters Vtx h = cdns tx.param(CDNS Tx(Model Specific(Tx V)))

| Ports List of port names (in same order as in SPICE)

Ports A signal pos A signal neg my driveP A pdref A puref

| D to A d port port1 port2 vlow vhigh trise tfall corner name polarity

D to A D drive my driveP A pdref 0 Vtx h 0.05n 0.03n Typ

[End External Model]

```

Tx/Rx Model described in external file

- Replaces the VI/VT curves

- Can now be parameterized when Language 'IBIS-ISS' is used

Parameter Definition is in a separate file

- Similar to AMI Parameters

- · Can be in .ami or any other

- User Selects Parameter Values from GUI

Parameter Value is passed to Simulator

- Using.param, the parameter value is passed to the simulator

- Converter\_Parameters are used appropriately in the stimulus/D\_to\_A

- [External Model]

- AMI equalization adaptation

- Backchannel training

- Applying IBIS-AMI to DDR applications

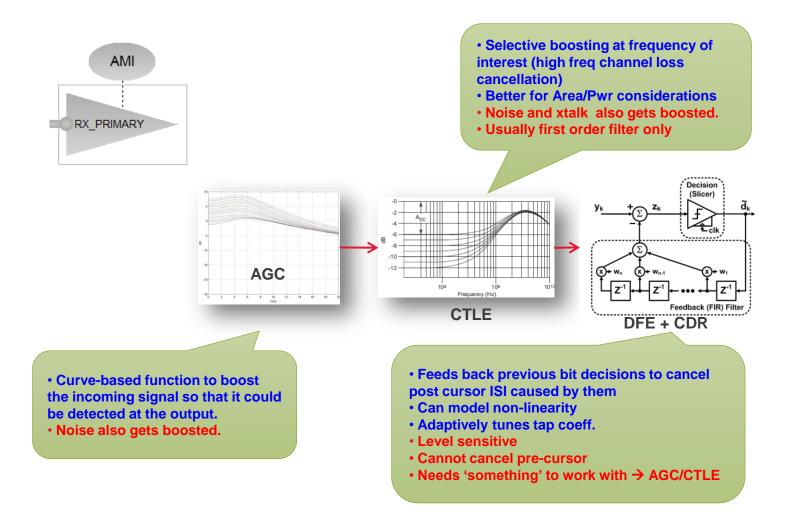

#### Anatomy of a Receiver AMI Model

- These different modules typically adapt at different rates

- Initial modules usually adapt more slowly than later ones

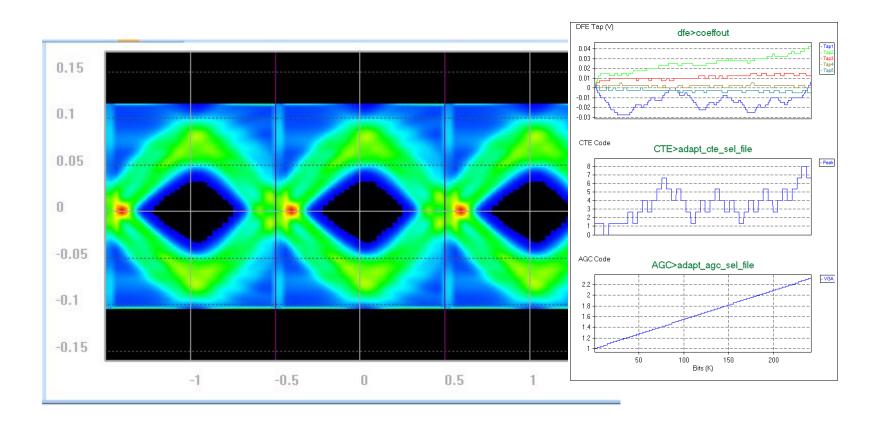

#### Rx With Default Adaptation

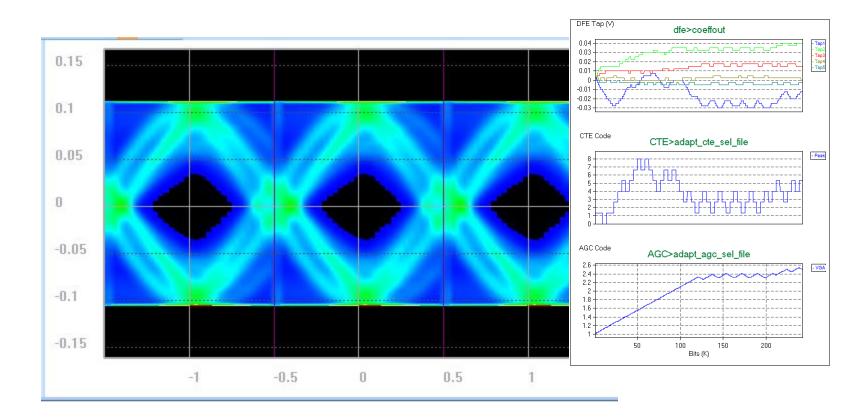

Note that adaptation coefficients don't converge

#### With Faster AGC Adaptation

Coefficients converge, but after 150k bits of traffic are passed

#### Ignoring the First 150k Bits

- Default was to ignore the first 40k bits

- Eliminates the noise from before coefficients converged

- Very important to be able to visualize how the adaptation is converging

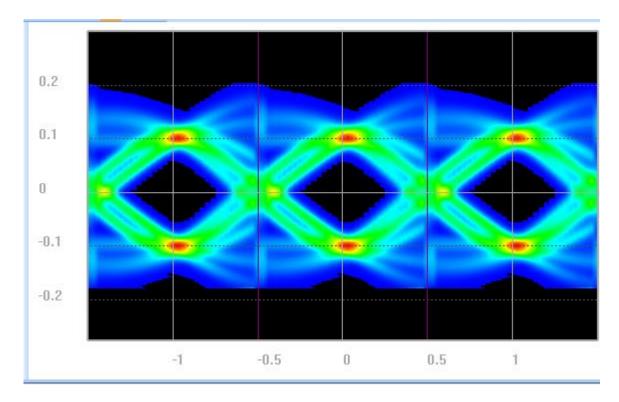

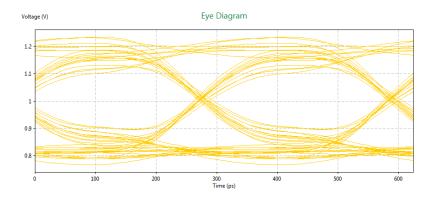

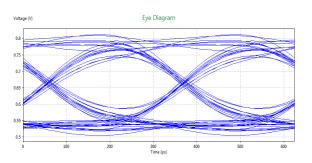

## Original Eye Contour vs. Final

Adjusting AGC adaptation time and Ignore\_Bits made a significant difference in eye height

- [External Model]

- AMI equalization adaptation

- Backchannel training

- Applying IBIS-AMI to DDR applications

## Backchannel Training (IBIS BIRD 147, in IBIS 7.0)

Rx feeds back EQ adjustments to Tx Start during training Tx sends Then data is passed Tx test with adjusted Tx adjusts EQ pattern settings in place Rx evaluates test **End** pattern **Training** Standard Rx SI OK? Serial Link phase recommends

complete

YES

NO

**EQ** adjustments

SI Flow

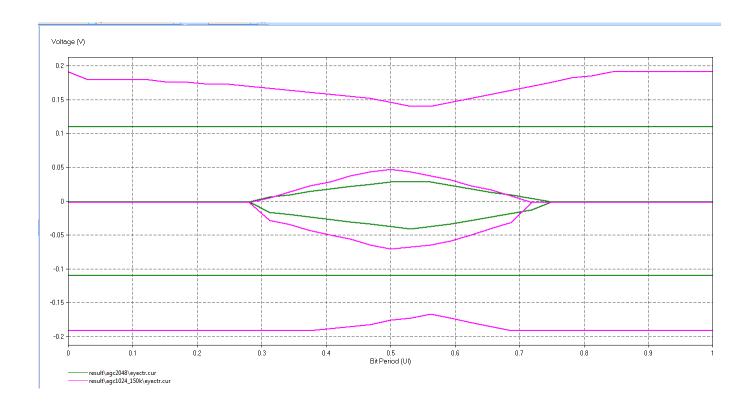

#### With and Without Backchannel

- Backchannel turned down Tx FFE settings somewhat

- Leaves more "heavy lifting" to Rx and its advanced adaptation

- Improves overall signal quality significantly

- [External Model]

- AMI equalization adaptation

- Backchannel training

- Applying IBIS-AMI to DDR applications

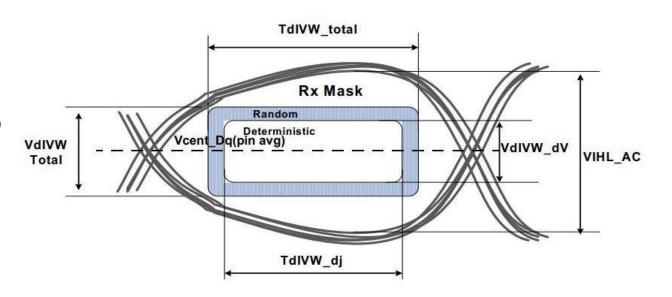

#### DDR4 Brought Some New Requirements

- Specified DQ mask compliance checking at a particular BER

- BER analysis requires extrapolation (bathtubs)

- Extrapolation requires a lot of traffic to be passed (need a lot of samples)

- Channel simulation can be applied

- Started to see equalization used at Controller side

- AMI modeling can be applied

- Worked with IP division to develop AMI model for DDR4 IP

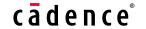

#### Simulation Testbench

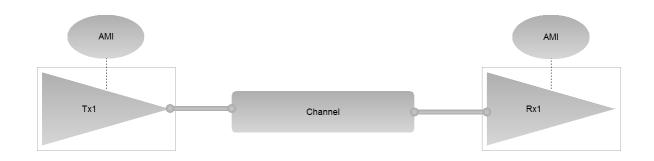

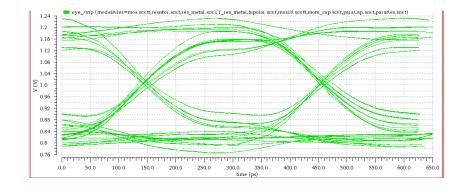

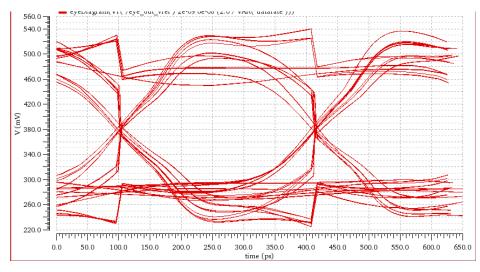

# CTLE Correlation: 3200Mbps

#### Input of receiver @pad

#### Output of CTLE

IBIS-AMI channel sim

Transistor-Level circuit sim

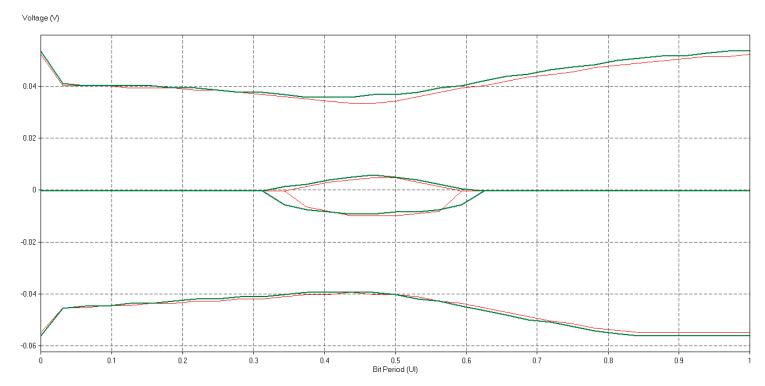

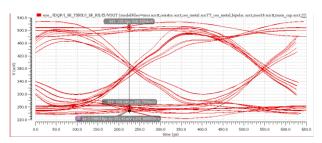

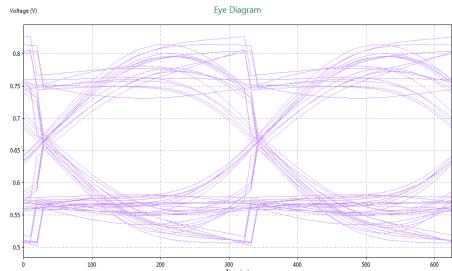

#### CTLE + DFE Correlation: 3200Mbps

Transistor-Level circuit sim

IBIS-AMI channel sim

#### Summary

- External Model syntax can be very useful for pre-design modeling, when detailed IBIS models are not available, and has had some recent additions in capability

- Building IBIS-AMI models is not the obstacle it used to be

- Adaptive equalization often has interplay between multiple sub-modules in real devices, and therefore also in AMI models

- If adaptive, understand if your EQ coefficients converge during simulation

- Backchannel training enables interplay between the Tx and Rx in simulation, and can produce more realistic results for devices that use backchannel

- Channel simulation and AMI modeling has been successfully applied to DDR4 IP (and more of this is expected with DDR5)

# cadence®

© 2017 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <a href="https://www.cadence.com/go/trademarks">www.cadence.com/go/trademarks</a> are trademarks or registered trademarks of Cadence Design Systems, Inc. All other trademarks are the property of their respective owners.