#### Skipper Liang

Asian IBIS Summit Shanghai, PRC November 13, 2017

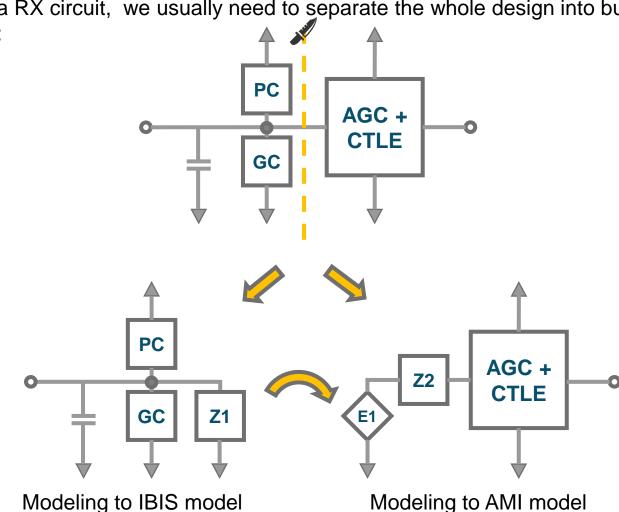

#### To Divide a RX Circuit:

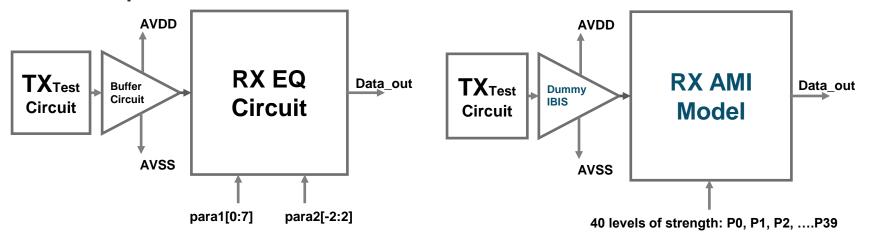

For modeling a RX circuit, we usually need to separate the whole design into buffer part and algorithm part:

- Question 1: What's the value of **Z1** and **Z2**?

- Question 2: What if the whole design is described in an encrypted netlist?

#### **IBIS** model

- generated from AMI generation tools

Many AMI generation tools will generate an IBIS model along with the AMI models generation:

- 1. Question 1: Can we use this IBIS model? YES

- 2. Question 2: If yes, is there any requirement of the circuit while modeling this circuit in this way?

The circuit should be a RX one composed of <u>linear</u> components.

3. Question 3: If my circuit could meet the requirement list above, how to do the modeling?

**Detailed in the following pages**

#### Thevenin's Theorem

#### Thévenin's theorem

From Wikipedia, the free encyclopedia

As originally stated in terms of DC resistive circuits only, Thévenin's theorem holds that:

- Any linear electrical network with voltage and current sources and only resistances can be replaced at terminals A-B by an equivalent voltage source V<sub>th</sub> in series connection with an equivalent resistance R<sub>th</sub>.

- The equivalent voltage V<sub>th</sub> is the voltage obtained at terminals A-B of the network with terminals A-B open circuited.

- The equivalent resistance R<sub>th</sub> is the resistance that the circuit between terminals A and B would have if all ideal voltage sources in the circuit were replaced by a short circuit and all ideal current sources were replaced by an open circuit.

- If terminals A and B are connected to one another, the current flowing from A to B will be V<sub>th</sub>/R<sub>th</sub>. This means that R<sub>th</sub> could alternatively be calculated as V<sub>th</sub> divided by the short-circuit current between A and B when they are connected together.

In circuit theory terms, the theorem allows any one-port network to be reduced to a single voltage source and a single impedance.

The theorem also applies to frequency domain AC circuits consisting of reactive and resistive impedances. It means the theorem applies for AC in an exactly same way to DC except that resistances are generalized to impedances.

Any black box containing resistances only and voltage and current sources can be replaced by a Thévenin equivalent circuit consisting of an equivalent voltage source in series connection with an equivalent resistance.

#### In short:

V<sub>TH</sub> = The voltage across the Port − "node A and B" while treating the Port − "node A and B" as **OPEN**

Isc = The current goes into node A and leaves node B while treating the Port – "node A and B" as **SHORT**

$R_{TH} = V_{TH}/I_{SC}$

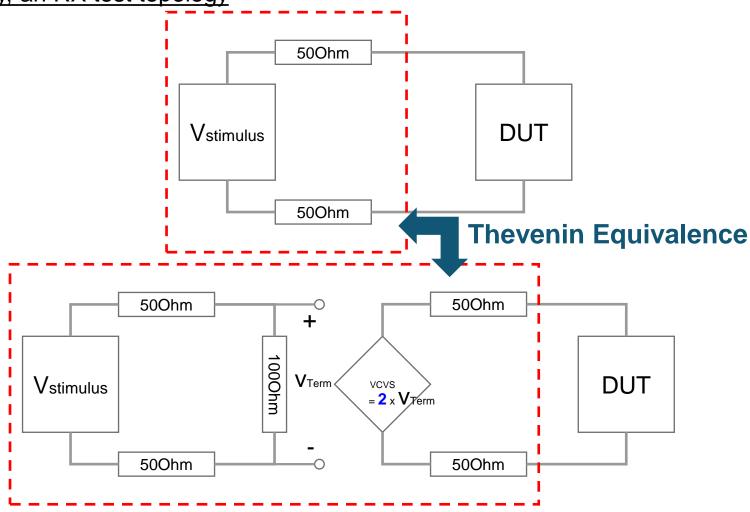

# **Thevenin Equivalence**

Typically, an RX test topology

## Thevenin Equivalence(Cont'd)

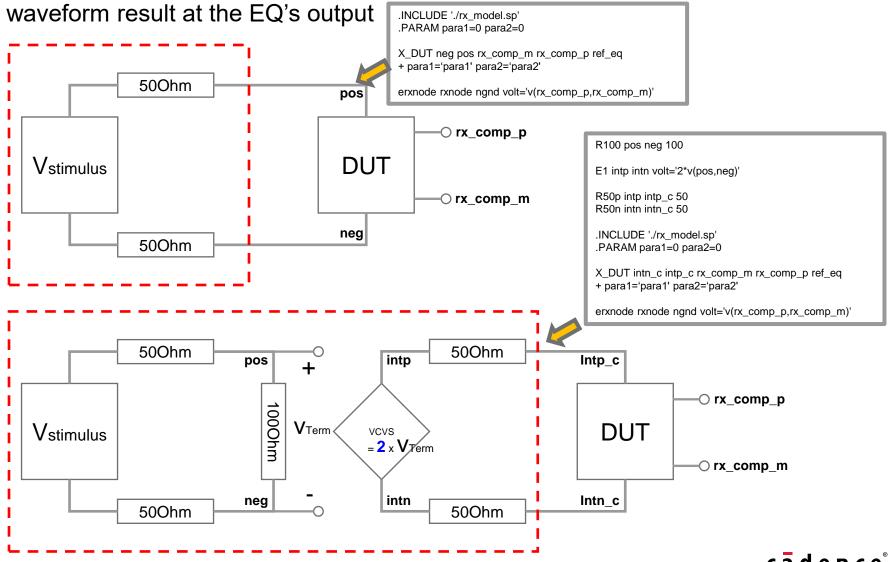

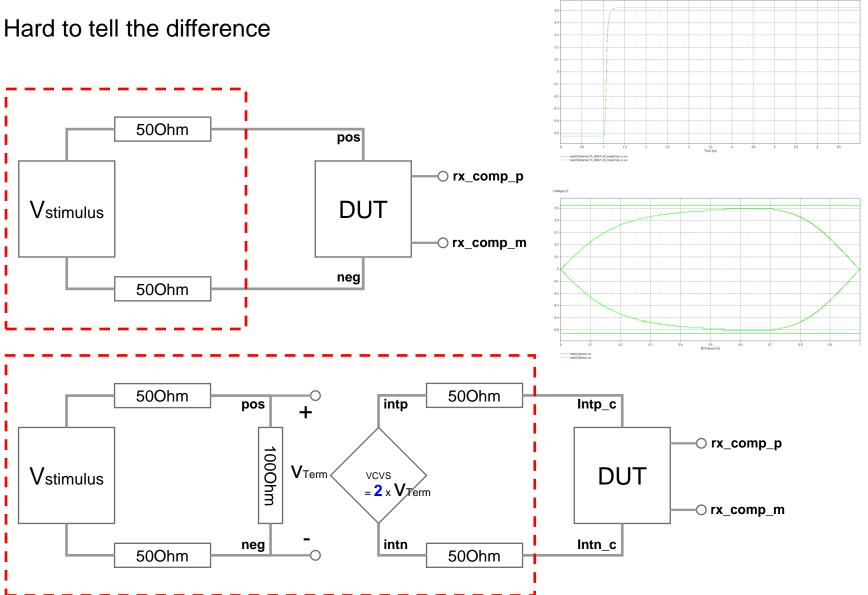

You can do a small experiment – the following 2 netlist will give the same

### Thevenin Equivalence(Cont'd)

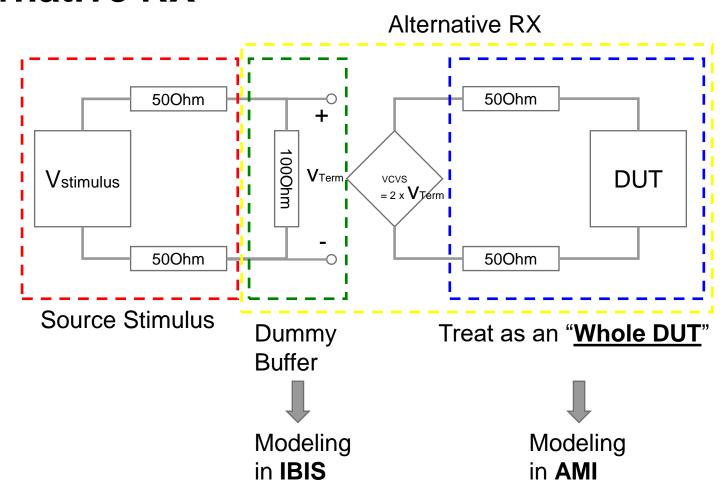

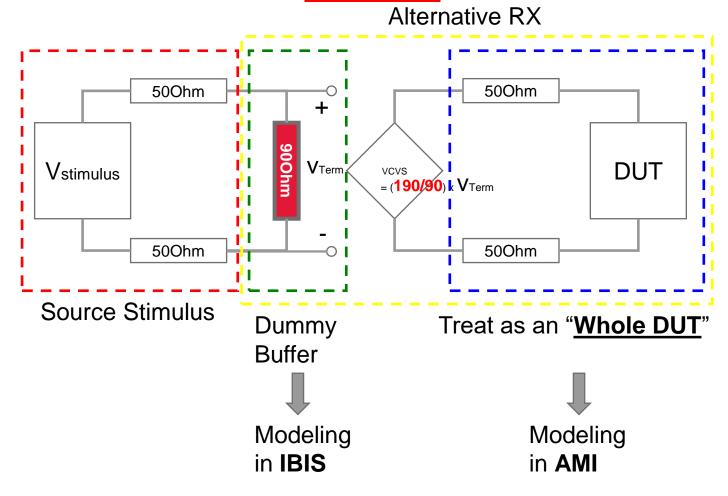

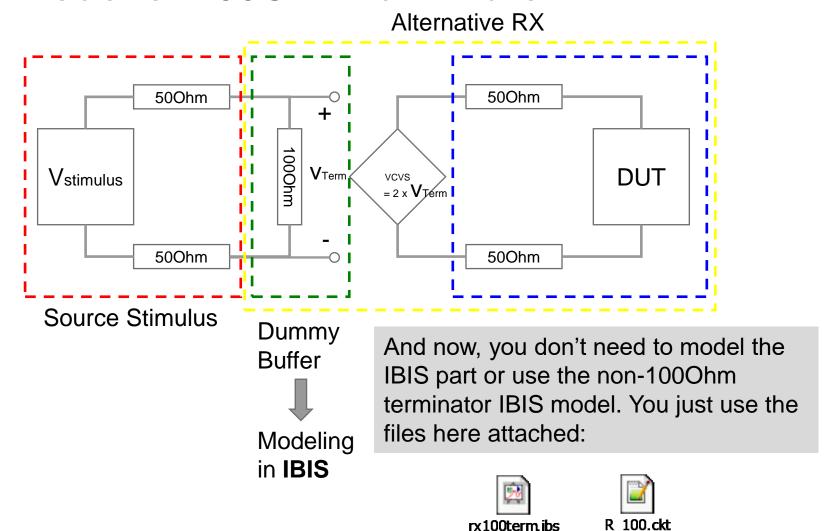

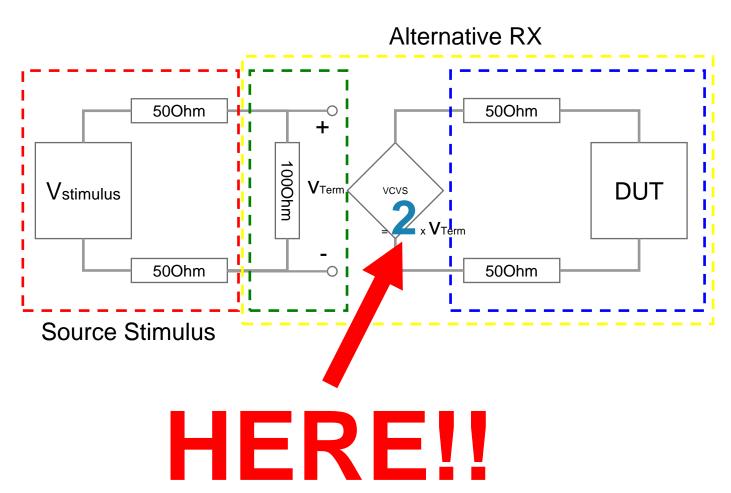

#### **Alternative RX**

### **IBIS** of the Dummy Buffer

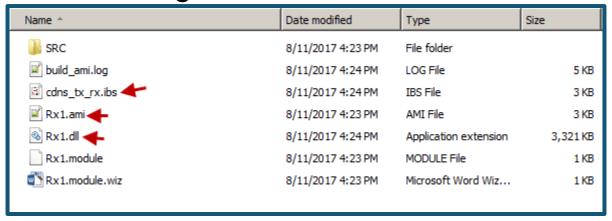

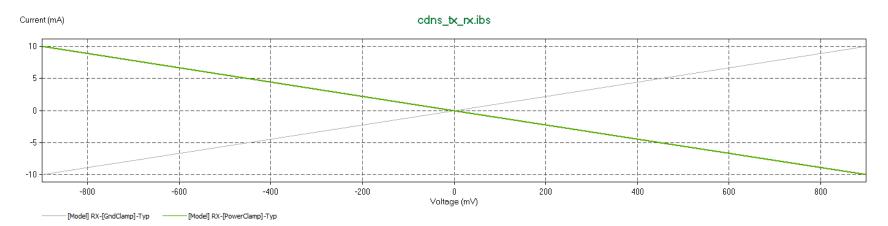

Check the RX IBIS model, which is generated along with the AMI model, to see if it's a 1000hm terminator between positive node and negative node:

For example, some AMI generation tools generate RX IBIS model with 900hm terminator between positive node and negative node – tell from the [Power Clamp] and [Ground Clamp]:

#### Alternative RX for a **900hm** terminator

#### **IBIS** model of 1000hm terminator

### IBIS model of 1000hm terminator (Cont'd)

The content of these files:

```

[Model] RX

Model type Input diff

[Voltage Range]

1.000V

1.0V

1.0V

[Ramp]

| variable

max

dV/dt r 0.120/0.001n

0.120/0.001n

0.120/0.001n

dV/dt f 0.120/0.001n

0.120/0.001n

0.120/0.001n

R load = 50.000

[External Model]

Language SPICE

| Corner corner name file name circuit name (.subckt name)

R 100.ckt

Corner

R 100

R 100.ckt

Corner

Min

R 100

Corner

R 100.ckt

R 100

| Ports List of port names (in same order as in SPICE)

Ports A puref A pdref A signal pos A signal neg

| A to D d port port1 port2 vlow vhigh corner name

A to D D receive A signal pos A signal neg -0.0 0.1 Typ

A to D D receive A signal pos A signal neg -0.0 0.1 Min

A to D D receive A signal pos A signal neg -0.0 0.1 Max

[End External Model]

[Algorithmic Model]

Executable Windows VisualStudio 64 RX HyperCore.dll RX HyperCore.ami

[End Algorithmic Model]

[End]

```

```

1 Subckt R 100 DVDD DVSS pos neg

2

3 Rp pos gnd 1e+15

4 Rn neg gnd 1e+15

5 Rdiff pos neg 100

6

7 .ends

```

### **Characterizing:**

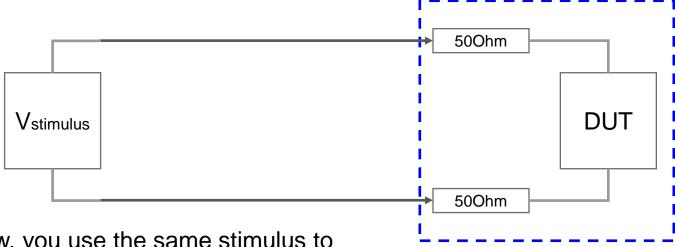

#### Alternative RX

Now, you use the same stimulus to characterize the circuit inside the Blue Dashed Box, that is:

Treat as an "Whole Equalizer"

- The same voltage swing

- 2. Fast rising time 1e-21sec (1e-9ps)

- 3. Small time steps, no more than 1ps

Which we use to characterize the channel.

### **Characterizing - Normalizing:**

```

RX_HyperCore

(CTE

( csvfilt

(file D:\Case CDNS 20160616 IBIS AMI\Modelize RX\CTLE TRAN 0 5

sel 0)

input 0.57

(\text{module\_off } 0)

( csvid_file CSVid.txt )

(td_filter_out cte td out.txt)

TX 500UT pos neg pwr in ngnd

24

( adapt_cte_sel_file cte out.txt )

25

E1 pos ngnd volt='0.47+0.57*v(in,ngnd)'

26

E2 neg ngnd volt='1.04-0.57*v(in,ngnd)

27

28

29

.ends

```

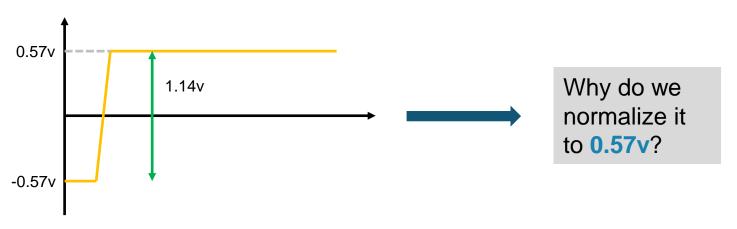

Normalize to the voltage swing you use to characterize the channel and the equalizer.

### **Characterizing – Normalizing (Cont'd):**

#### Beware!!:

```

RX_HyperCore

(CTE

( csvfilt

( file D:\Case CDNS_20160616 IBIS AMI\Modelize RX\CTLE TRAN 0 5

sel 0)

input 0.57

( module_off 0 )

( csvid_file csvid.txt )

(td_filter_out cte td out.txt)

TX 500UT pos neg pwr in ngnd

24

( adapt_cte_sel_file cte out.txt )

25

E1 pos ngnd volt='0.47+0.57*v(in,ngnd)

26

E2 neg ngnd volt='1.04-0.57*v(in,ngnd)

27

You may wonder the input

28

29

.ends

stimulus is 2x0.57=1.14V,

```

## **Characterizing – Normalizing (Cont'd):**

The answer is:

**Question**: What if you are using an IBIS model which is equivalent to a 900hm terminator instead of a 1000hm?

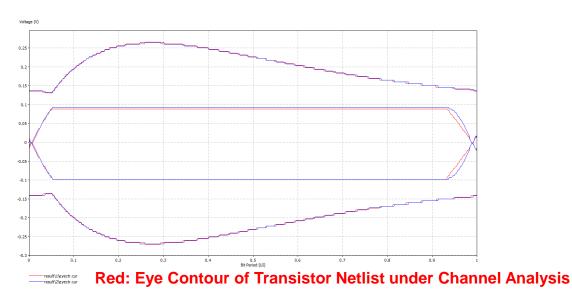

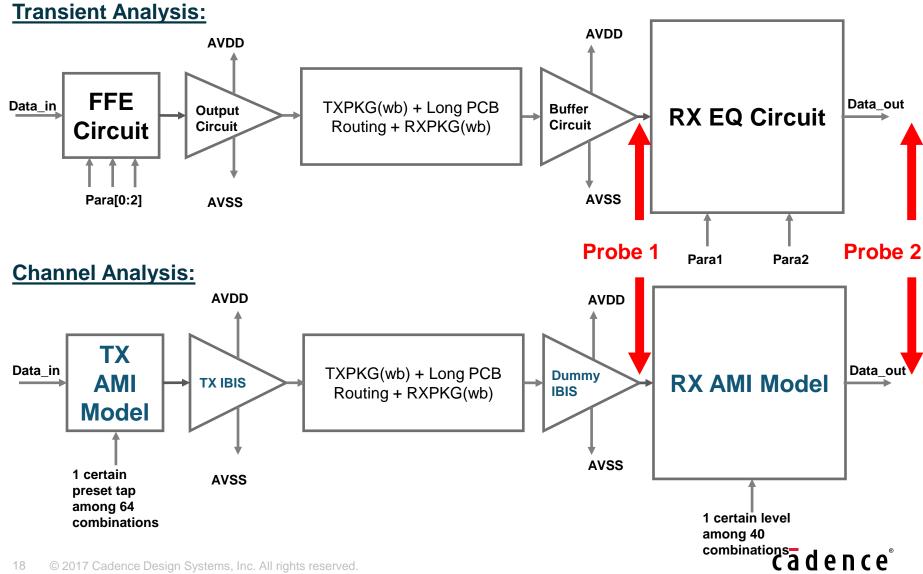

# **Correlation – Channel Analysis**

between the IBIS-AMI and the Transistor Netlist

#### Under a simple test environment:

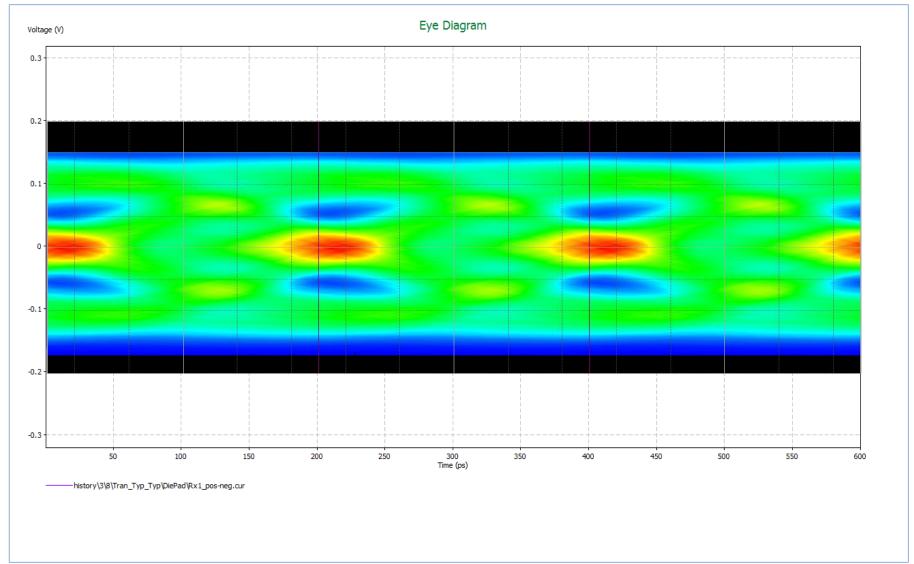

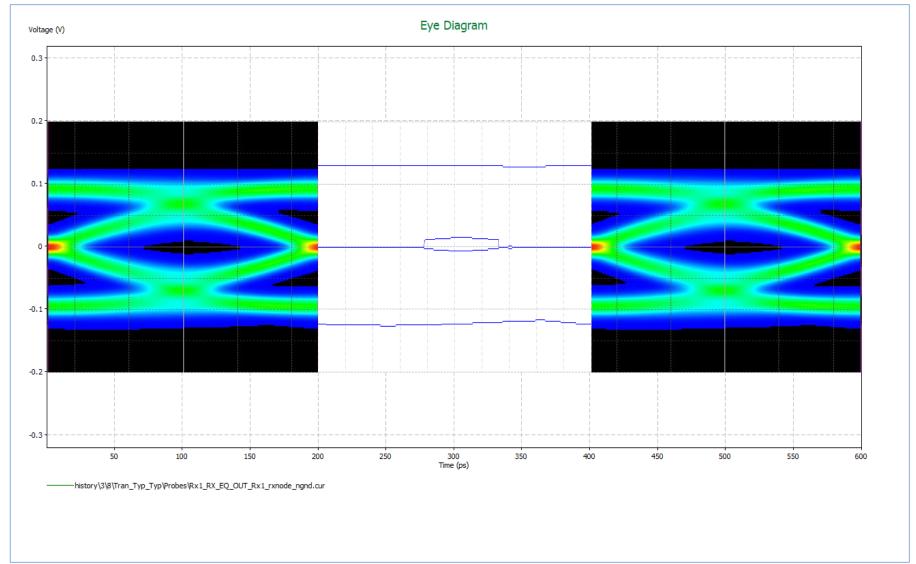

Blue: Eye Contour of IBIS-AMI model under Channel Analysis

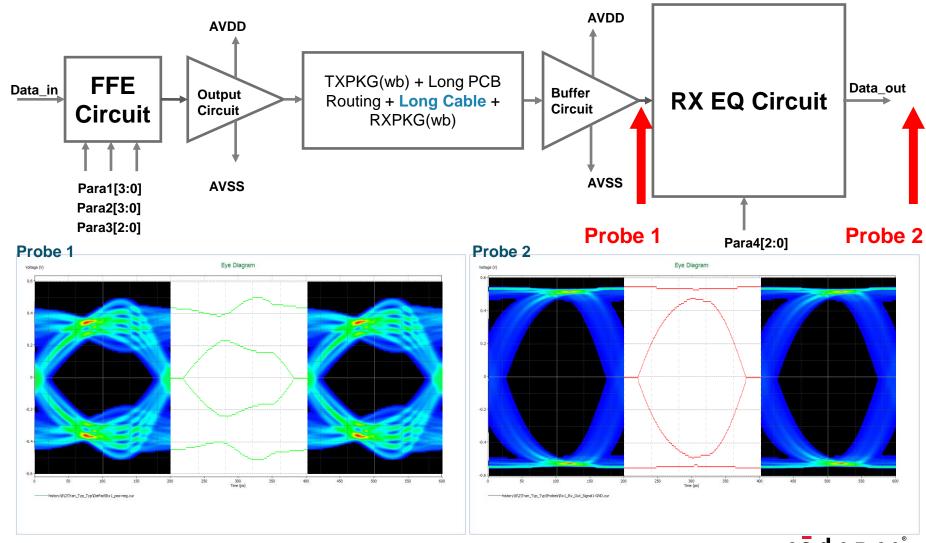

### Correlation – Mid Length Channel

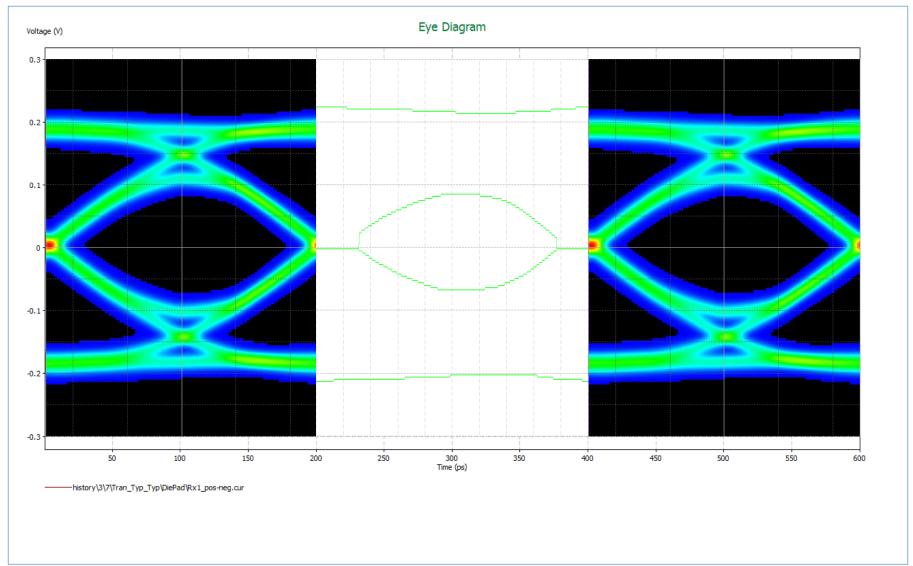

# **Correlation – Mid Length Channel (Probe 1)**

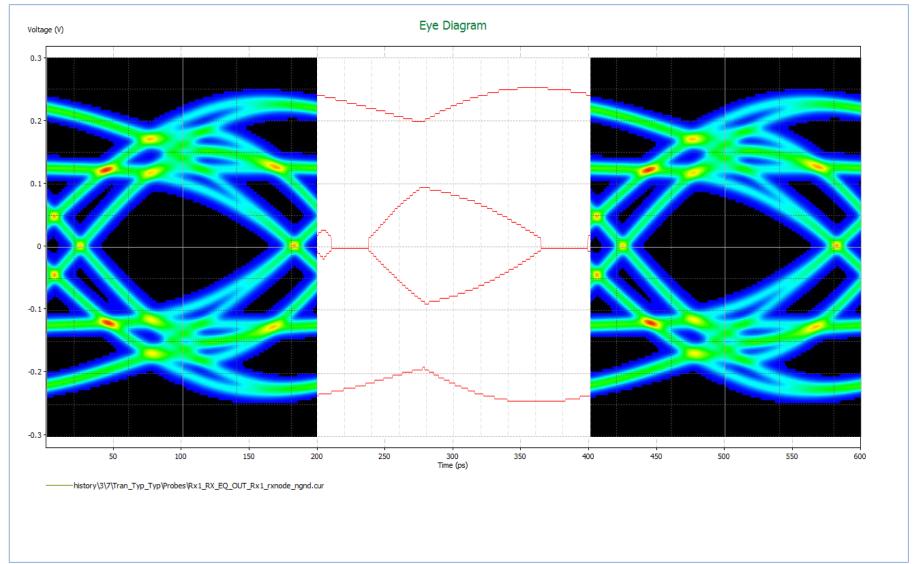

# **Correlation – Mid Length Channel (Probe 2)**

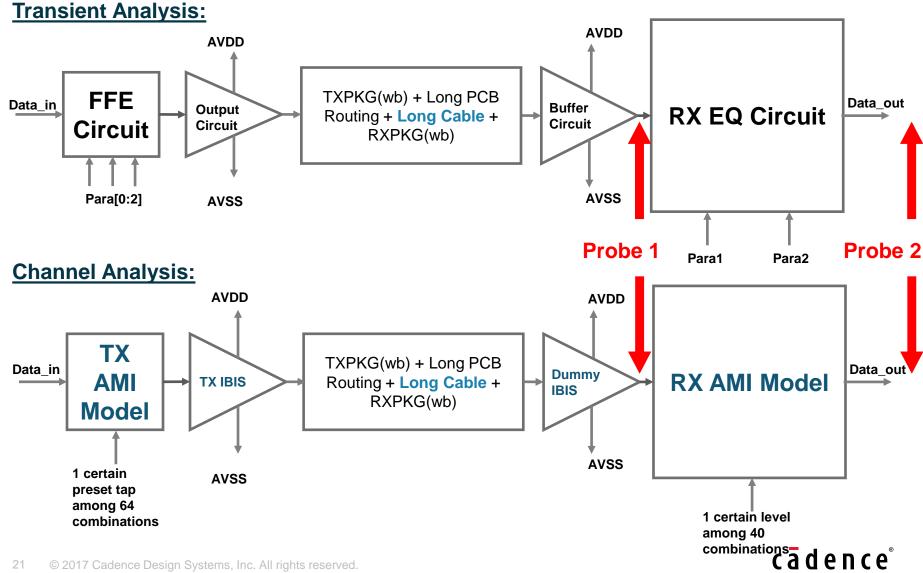

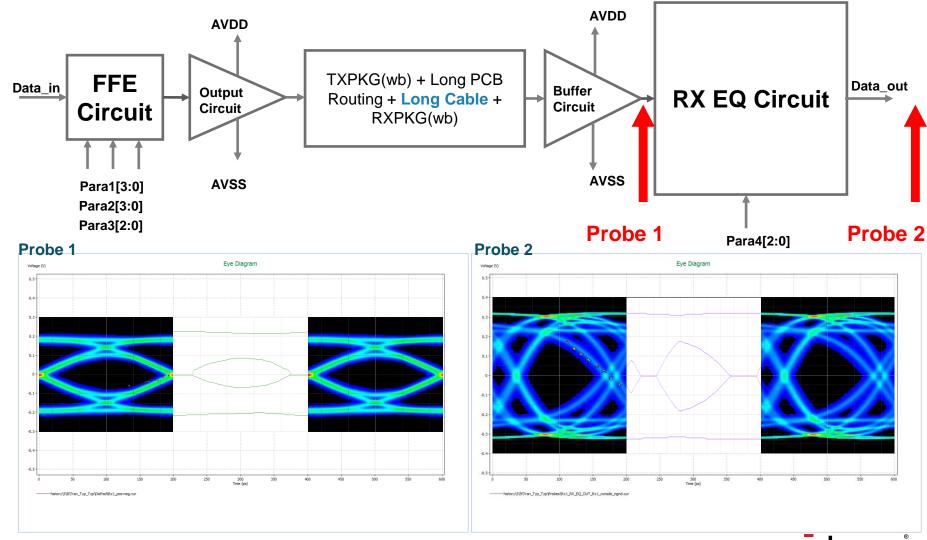

### Correlation – Long Length Channel

# **Correlation – Long Length Channel (Probe 1)**

# Correlation – Long Length Channel (Probe 2)

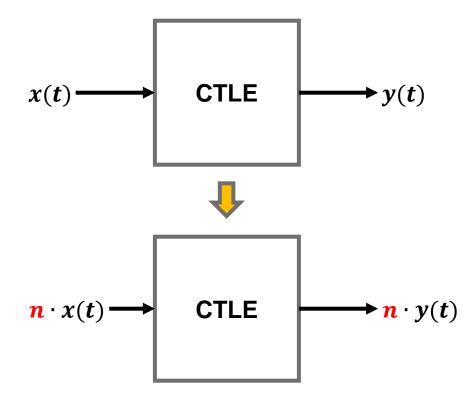

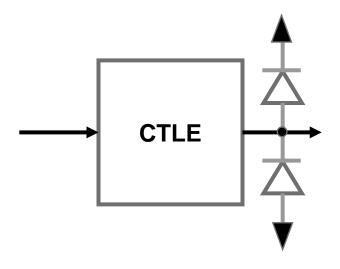

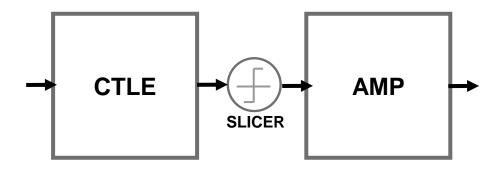

#### Limitation

This method is only valid while being applied to a pure CTLE which is composed of linear components, such as R, L, C, Linear E(VCVS), Linear F(CCCS)...etc.

Or in short, a CTLE which satisfies:

## **Limitation (Cont'd)**

There're still lots of circuits not suitable for this method. For example:

#### Conclusion

- Cutting/Dividing the whole design is a necessary process during RX IBIS-AMI modeling.

This slides provides a method which guarantees the combination of the sub-designs so-divided is exactly equivalent to the original whole design.

- Also, the method in this slides benefits modelers that they will no longer need to model a RX IBIS model. A dummy IBIS will be used for all cases while the buffer characteristics has been modeled into the AMI model. No cutting/dividing is needed any more.

- This slides provides a method to generate IBIS-AMI simply by characterizing the V/T of the netlist – away more accurate than generating IBIS-AMI by inputting parameters values.

- However, this method is only valid while being applied to a purely linear equalizer, that

is, there exists a purely linear relationship between the input and output of the

equalizer.

- What else? Can a TX FFE be modeled simply by characterizing? Can an non-linear RX CTE be modeled simply by characterizing?

#### **Correlation – Mid Length Channel**

In fact, now we've even developed a flow which can successfully model a **non-linear DFE-free** RX EQ with very good accuracy simply by characterizing: **Example 1**

## **Correlation – Long Length Channel**

In fact, now we've even developed a flow which can successfully model a **non-linear DFE-free** RX EQ with very good accuracy simply by characterizing: **Example 2**

#### See you on IBIS Summit 2018

# cādence®

© 2017 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo and Spectre are registered trademarks and Sigrity, SystemSI, and T2B are trademarks of Cadence Design Systems, Inc. in the United States and other countries.. All rights reserved. All other trademarks are the property of their respective owners.