#### Signal Integrity Analysis for 56G-PAM4 Channel of 400G Switch

Sophia Feng/Vincent Wen of Celestica sopfeng@celestica.com Asian IBIS Summit Shanghai, PRC November 13, 2017

### Agenda

- Background

- 200GBASE-KR4

- 400GAUI-8 C2M/200GBASE-CR4

- CEI-56G-VSR-PAM4

- Conclusion

### Background

- Celestica focuses on advanced switches, storage and server.

- The switch bandwidth is moving from 100G to 400G.

- Data rate is moving from 25 Gbps to 56 Gbps.

## Agenda

- Background

- 200GBASE-KR4

- 400GAUI-8 C2M/200GBASE-CR4

- CEI-56G-VSR-PAM4

- Conclusion

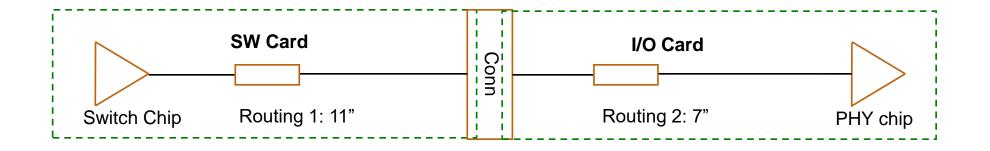

### 200GBASE-KR4- Channel Topology

• This channel is between switch chip and PHY chip.

• Megtron 4 level material is used for the analysis.

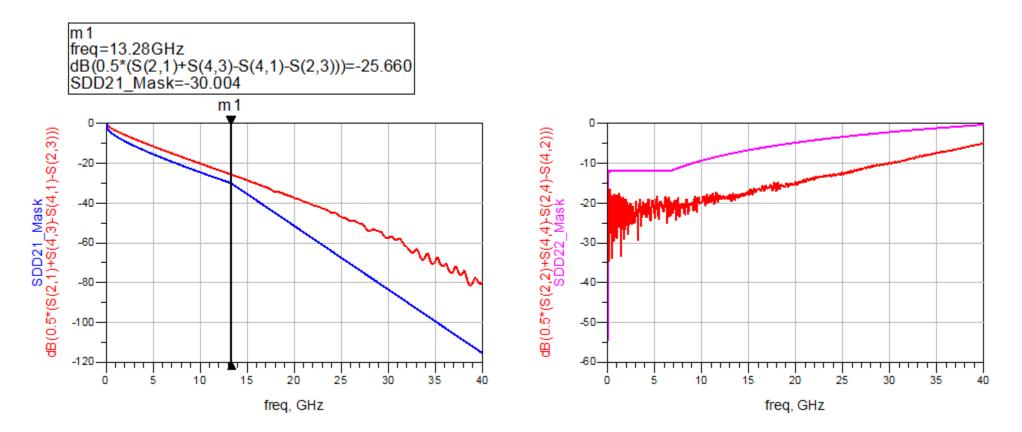

#### **200GBASE-KR4- Frequency Domain Simulation Results**

The simulation results are shown above. The channel includes an 11 inch trace on the Switch Card, a 7 inch trace on the I/O Card and one connector. The channel can meet the 200GBASE-KR4 specifications of the passive channel requirements.

Think Bigger. Reach Further.

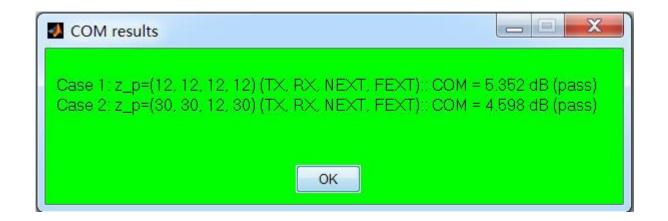

#### 200GBASE-KR4- COM Simulation

- Consideration of the 9 FEXT and 8 NEXT crosstalk models to run the COM.

- The crosstalk considers the crosstalk in BGA area and the crosstalk in connector area.

• Simulation results show that the 11 inch trace in Switch Card and 7 inch trace in I/O Card can pass the COM specification with default package model.

#### 200GBASE-KR4- Time Domain Simulation Results(1)

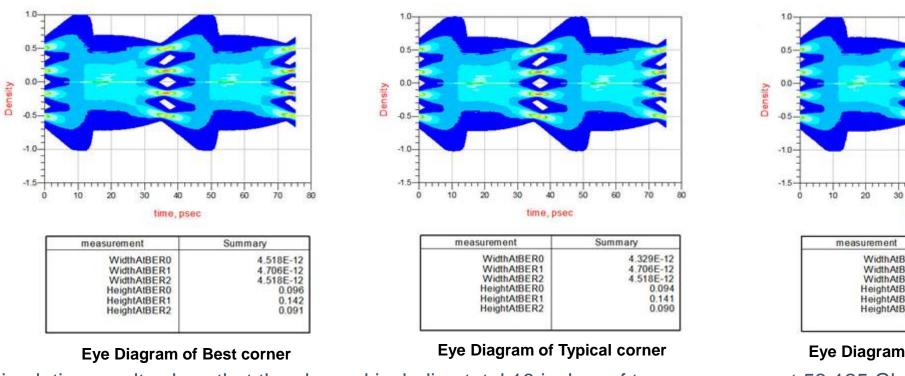

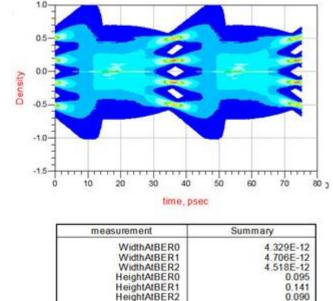

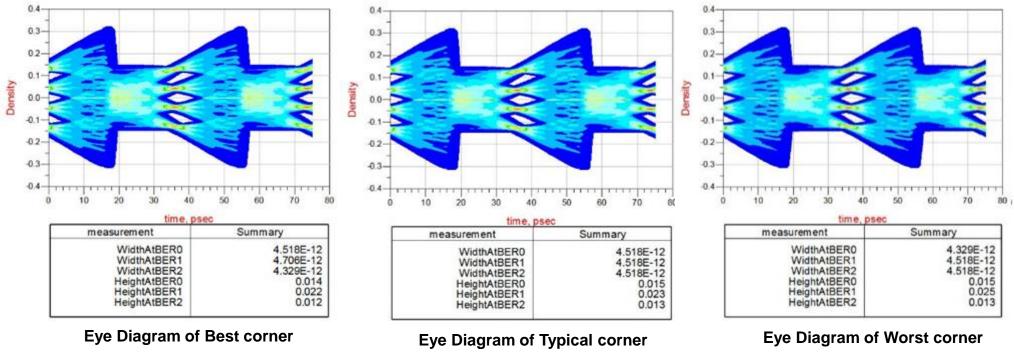

#### • The simulation settings and results are shown in the Table and Figure below. The channel is from switch chip to PHY chip.

| Trace Length                                          | PVT Corner: Best<br>Eye Width/Eye Height @BER=1e-6 in Sim | PVT Corner: Typical<br>Eye Width/Eye Height @BER=1e-6 in Sim | PVT Corner: Worst<br>Eye Width/Eye Height @BER=1e-6 in Sim |

|-------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------|

| 11inches in Switch<br>Card and 7inches<br>in I/O Card | 4.52ps/96mV                                               | 4.33ps/95mV                                                  | 4.33ps/141mV                                               |

|                                                       | 4.71ps/142mV                                              | 4.71ps/141mV                                                 | 4.71ps/141mV                                               |

|                                                       | 4.52ps/91mV                                               | 4.52ps/90mV                                                  | 4.52ps/90mV                                                |

#### Eye Diagram of Worst corner

Simulation results show that the channel including total 18 inches of trace can support 53.125 Gbps data rate.

#### 200GBASE-KR4- Time Domain Simulation Results(2)

9

• The simulation settings and results are shown in the Table and Figure below. The channel is from the PHY chip to switch chip.

Eye Diagram of Worst corner

There is some issues with the time domain simulation of PHY TX and switch chip RX. Celestica is working with the chip vendor.

## Agenda

- Background

- 200GBASE-KR4

- 400GAUI-8 C2M/200GBASE-CR4

- CEI-56G-VSR-PAM4

- Conclusion

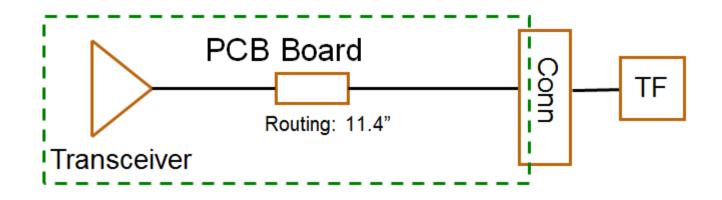

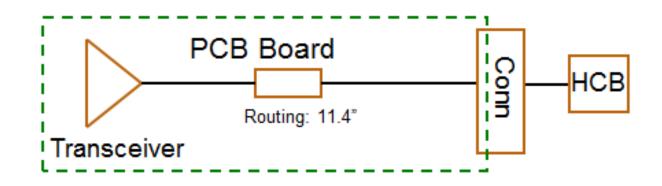

## 400GAUI-8 C2M/200GBASE-CR4- Interconnect Modeling

• The 400GAUI-8 C2M specification has defined the requirement from the host transmit to the test fixture. The topology is shown in the Figure below. Megtron 7 PCB material has been used in this channel.

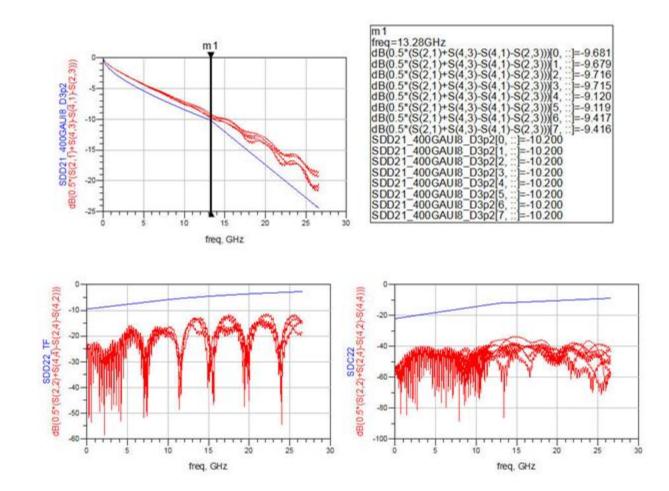

# 400GAUI-8 C2M/200GBASE-CR4- Host Channel Analysis in Frequency Domain

• Simulation results show that the channel, including 11.4 inches of trace, can meet the 400GAUI-8 C2M specification passive requirements.

### 400GAUI-8 C2M/200GBASE-CR4

- Loopback Channel Analysis, Topology and 2.5m Cable)

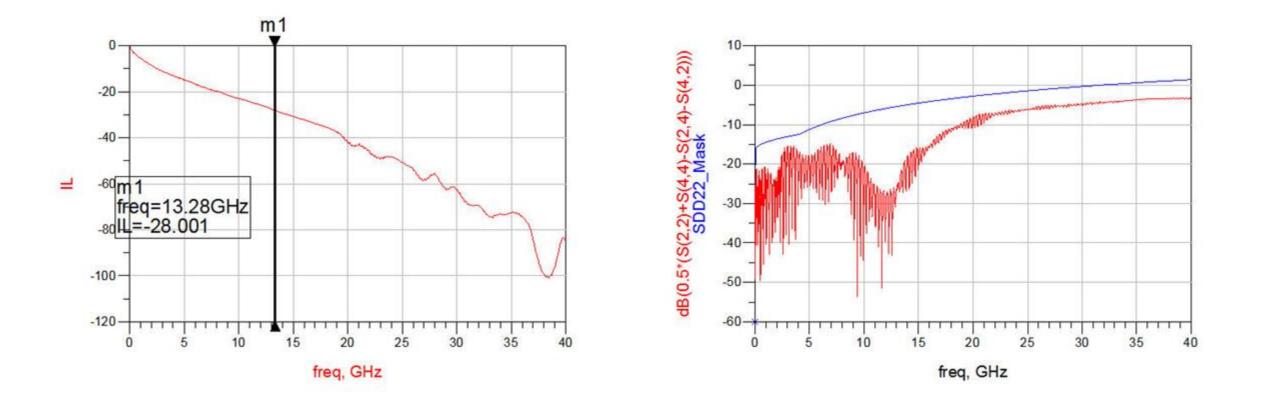

- PCB Board PCB Board <u>Conn</u> Conn Cable Routing: 11.4" Routing: 11.4" Transceiver Transceiver m1 10 dB(0.5\*(S(2,2)+S(4,4)-S(2,4)-S(4,2))) SDD22\_Mask 0--20 -10--40 1 -60m freq=13.28GHz -80HL=-26.621 -50 -100 -60 -120 -70-5 10 15 20 25 10 30 35 15 20 25 30 35 40 freq, GHz freq, GHz

- The copper cable loopback channel topology with 200GBASE-CR4 is shown below.

• Simulation results show the IL/RL of two 11.4 inch channels with a 2.5m 28AWG cable loop back can meet the 200GBASE-CR4 specification passive requirements.

#### 400GAUI-8 C2M/200GBASE-CR4 - Loopback Channel Analysis, 3m Cable

Think Bigger. Reach Further.

Simulation results show the IL/RL of two 11.4 inch channels with 3m 28AWG cable loop back can meet the 200GBASE-CR4 specification passive requirements.

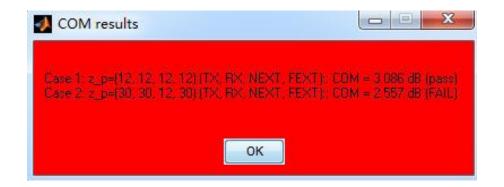

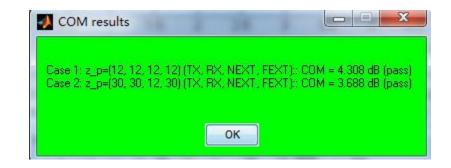

#### 400GAUI-8 C2M/200GBASE-CR4 - Loopback Channel Analysis, COM, 3m

- The channel margin shall be greater than or equal to 3dB after COM calculation for 200GBASE-CR4 Channel.

- 9 aggressor FEXT channels and 8 aggressor NEXT channels on both side of the victim channel are considered for the COM crosstalk analysis. The major contributors to crosstalk such as traces, vias, cable paddle card are considered for the crosstalk modeling. The detailed trace modeling with crosstalk is shown below.

Simulation results show that the channel including two 11.4 inch traces with 3m 28AWG QSFP-DD cable assembly, Case1 can pass and Case2 cannot meet the IEEE802.3cd Specification COM requirement for 200GBASE-CR4 based on the default package S parameters.

Simulation results show that the channel including two 11.4 inch traces with the 2.5m 28AWG QSFP-DD cable assembly, can meet the IEEE802.3cd/D2.2 Specification COM requirement for 200GBASE-CR4 based on the default package S parameters for both cases.

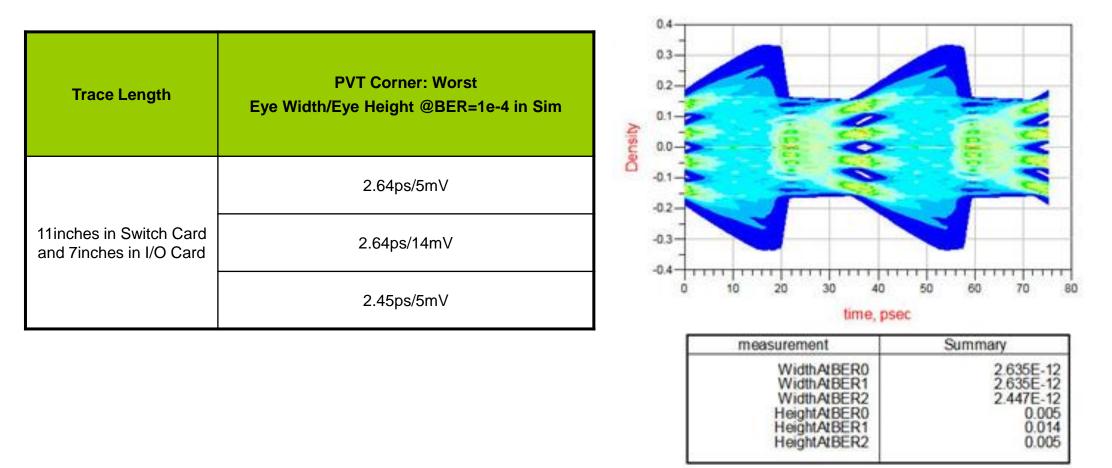

#### 400GAUI-8 C2M/200GBASE-CR4 - Loopback Channel Time Domain Analysis

• The simulation settings and results are shown in the Table and Figure below.

| Trace<br>Length | Cable       | PVT Corner: Best<br>Eye Width/Eye Height<br>@BER=1e-6 in Sim | PVT Corner: Typical<br>Eye Width/Eye Height<br>@BER=1e-6 in Sim | PVT Corner: Worst<br>Eye Width/Eye Height<br>@BER=1e-6 in Sim |

|-----------------|-------------|--------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------|

| 11.4inch        | 3m<br>28AWG | 4.52ps/14mV                                                  | 4.52ps/14mV                                                     | 4.52ps/14mV                                                   |

|                 |             | 4.71ps/22mV                                                  | 4.71ps/22mV                                                     | 4.71ps/22mV                                                   |

|                 |             | 4.33ps/12mV                                                  | 4.33ps/12mV                                                     | 4.33ps/12mV                                                   |

Simulation results show that the channel including two 11.4 inch traces can support the 3m 28AWG QSFP-DD cable for 53.125G rate.

17

### Agenda

- Background

- 200GBASE-KR4

- 400GAUI-8 C2M/200GBASE-CR4

- CEI-56G-VSR-PAM4

- Conclusion

#### CEI-56G-VSR-PAM4 - Interconnect Modeling

• The CEI-56G-PAM4-VSR specification defines the requirement from the host transmit to the external IO connector. The topology is shown in the Figure below. Megtron 7 PCB material has been used in this channel. Note that from Host PCB to Connector insertion loss is up to 8.5 dB.

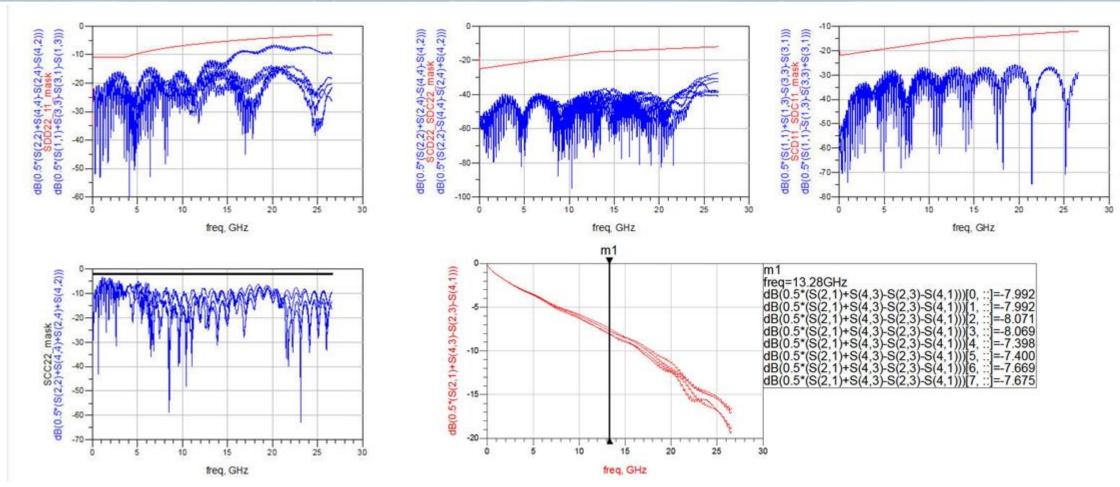

#### CEI-56G-VSR-PAM4 S - Host Channel Analysis in Frequency Domain

• Simulation results show that the channel including an 11.4 inch trace with one connector can meet the passive requirement of the CEI-56G-VSR-PAM4 specifications.

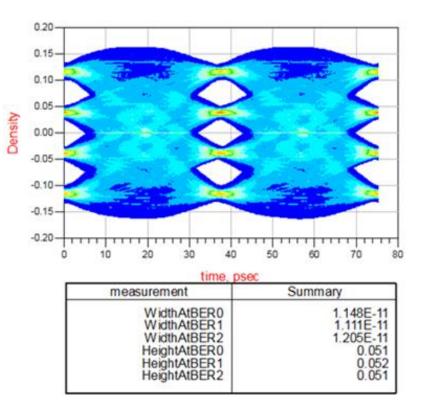

#### CEI-56G-VSR-PAM4 - Host Channel Analysis in Time Domain

• The simulation results are shown in the table below.

| Trace<br>Length | Eye Width/Eye Height<br>(@BER=1e-6 in Sim) | Eye Width/ Eye Height<br>(@BER=1e-6 in spec) |  |

|-----------------|--------------------------------------------|----------------------------------------------|--|

|                 | 11.48ps/51mV                               |                                              |  |

| 11.4<br>inches  | 11.11ps/52mV                               | >=8.28ps/35 mV                               |  |

|                 | 12.05ps/51mV                               |                                              |  |

• Simulation results show that the channel including a 11.4 inch trace with one connector can meet the eye height requirement of the CEI-56G-VSR-PAM4 specification at TP1a.

# Unlock the Potential of the Future