# Quality checks for power aware IBIS models

Asian IBIS Summit Tokyo, Japan November 18, 2016

Authors: Ashish Gupta (<u>asqupta@cadence.com</u>), Cadence Design Systems, India Rameet Pal (<u>rameet@cadence.com</u>), Cadence Design Systems, India Presenter: Takuya Moriya, Cadence Design Systems, Japan

### cādence®

## Agenda

#### Introduction

#### Power aware IBIS 5.1 model simulation

Simulation with sinusoidal noise injected to power rail

Simulation with parasitic of Power and Ground

- Limitation with power aware IBIS 5.1 model

- Proposed solution

- Summary

### Introduction

- IBIS 5.1 model is power aware with usage of keywords composite current and ISSO\_PU/PD tables

- These keywords take into consideration pre-driver current and gate modulation i.e. driver strength variation due to simultaneously switching noise

- When power aware IBIS model is used in system level simulation power rail is subjected to noise

- IBIS should be sensitive enough to take these variations into account to achieve accurate results

- Quality checks that one should perform and possible solution to correlate with SPICE netlist results are presented

- 28nm-LPDDR4 has been used as a test case

## Power Aware IBIS 5.1 model simulation

#### cādence°

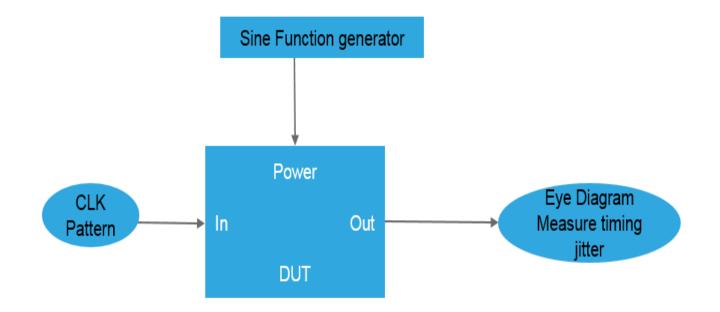

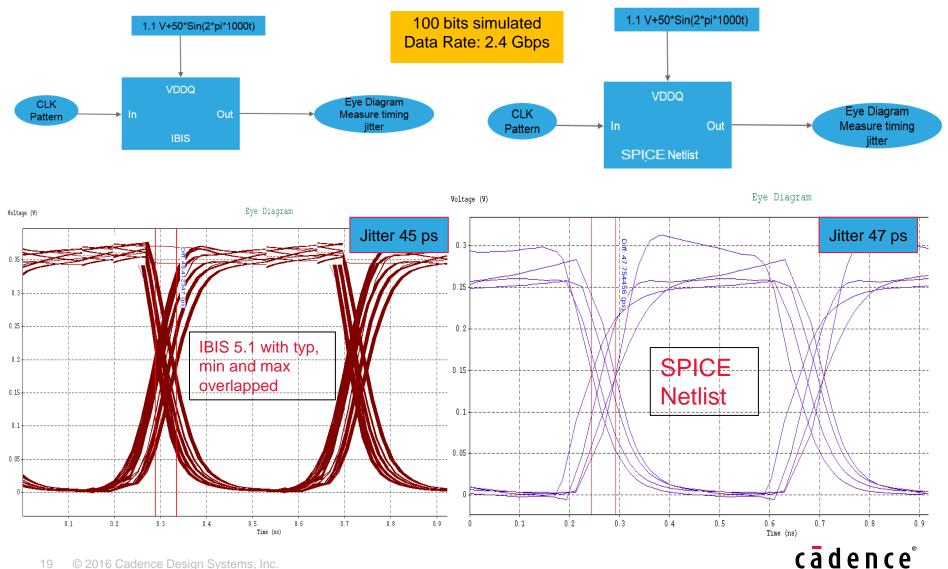

## 1<sup>st</sup> Quality Check: Simulation with sinusoidal noise injected to power rail

#### Setup to measure the jitter sensitivity

#### **Mismatch in timing jitter** Case1: 100 MHz 200mV p2p sinusoidal noise injected on power rail

© 2016 Cadence Design Systems, Inc.

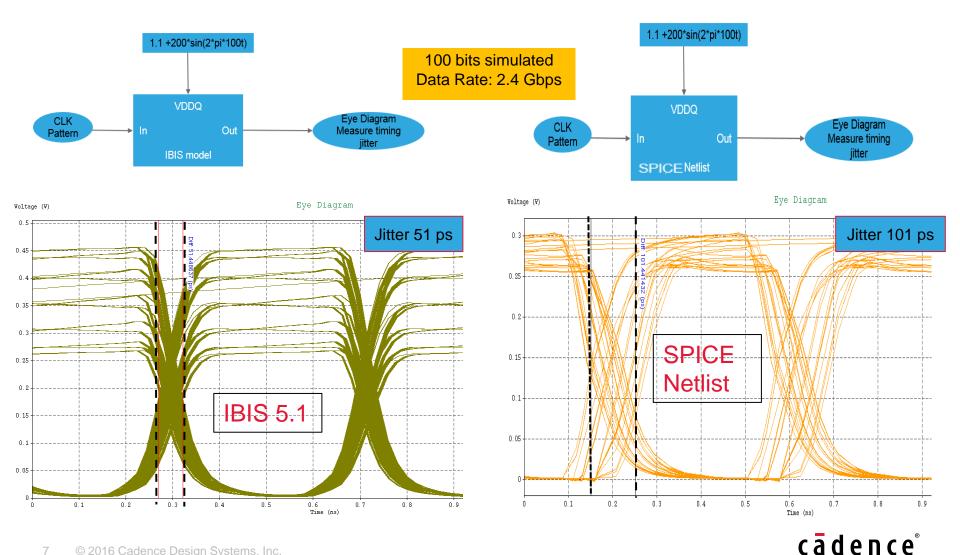

#### **Mismatch in timing jitter** Case2: 1 GHz 50mV p2p sinusoidal noise on power rail

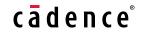

## 2<sup>nd</sup> Quality Check: Simulation with/without parasitic of power and ground

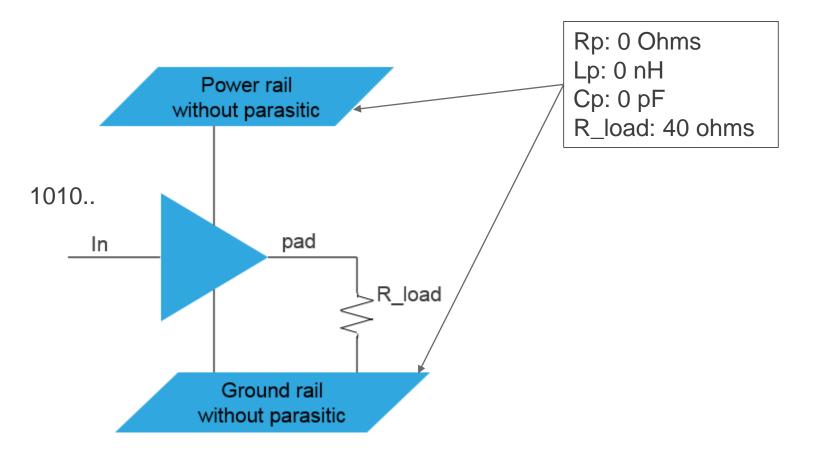

## Case1: Correlation setup of Power/Ground rail without parasitic

## PAD waveform when power without any parasitic is used to do correlation with IBIS 5.1

cādence°

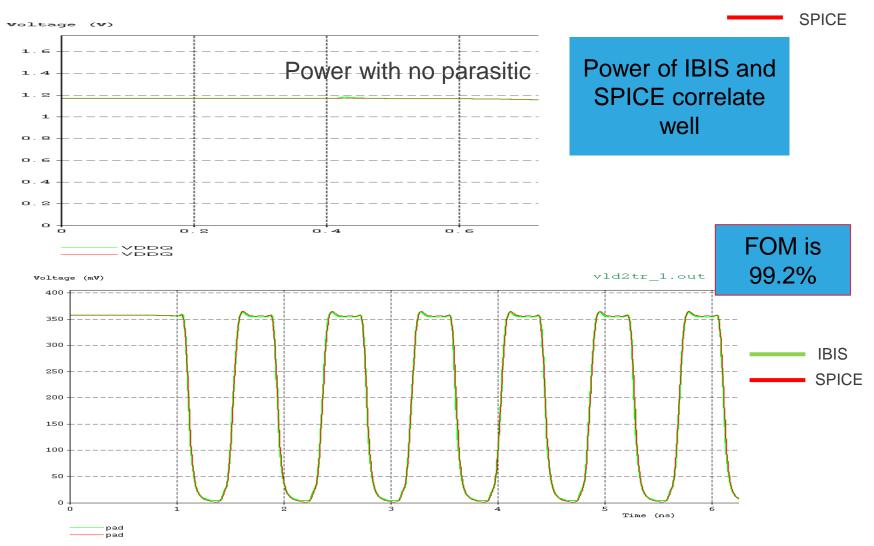

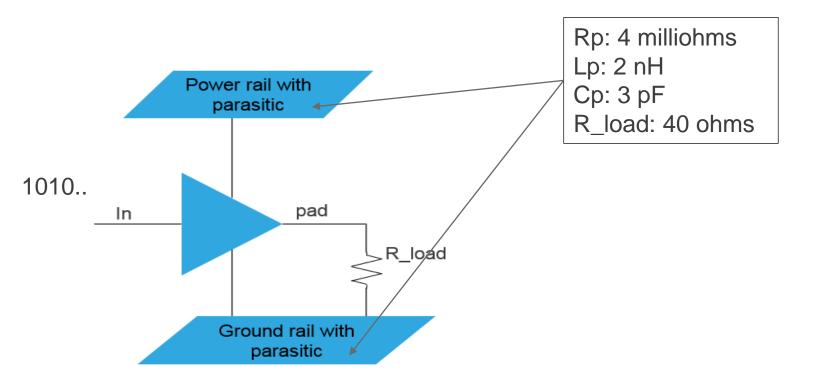

## Case2: Correlation setup of Power/Ground rail with parasitic

#### With IBIS 5.1 IBIS model

cādence<sup>®</sup>

## Limitation with power aware IBIS 5.1

### **IBIS 5.1 model limitation**

- IBIS 5.1 underestimates power supply variation into signal jitter

- IBIS 5.1 correlation with SPICE netlist fails when power/ground rail is subject to parasitic

## Proposed solution

16 © 2016 Cadence Design Systems, Inc.

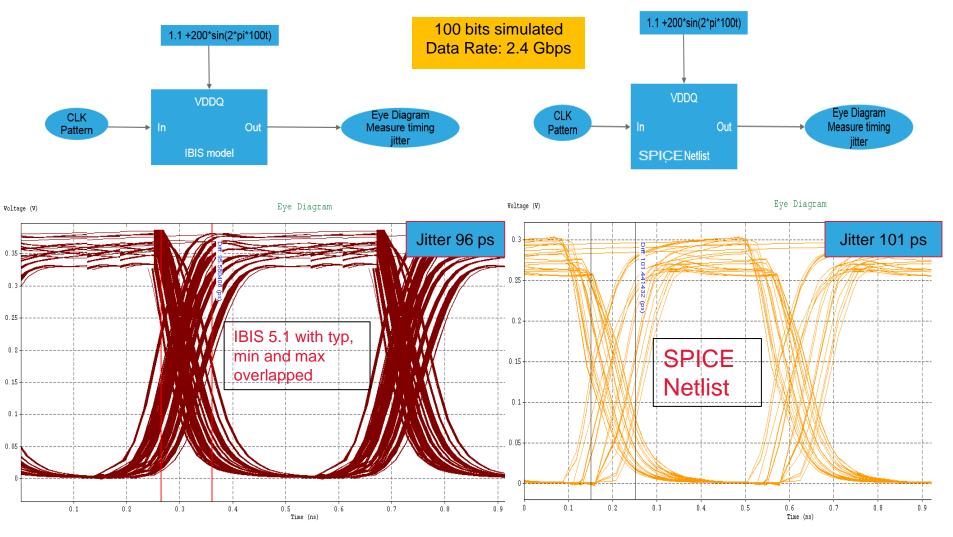

#### Proposed solution for Case1 IBIS 5.1 with power variation to account for Power Supply Noise Induced Jitter

- Jitter occurs due to change in IO buffer delay and buffer delay is a function of the supply voltage

- In order to model jitter due to power supply. We can use typical, min and max waveforms with only variation in terms of voltage whereas process, temperature remains same and overlap these 3 waveforms to account for PSNIJ

- Variation of +/-5% is accounted from typical voltage of 1.1 V (lpddr4 power supply) to fetch three waveforms and all of them over lapped to generate eye diagram

#### Improved matching in timing jitter Case1: 100 MHz 200mV p2p sinusoidal noise on power rail

c <mark>a</mark> d e n c e<sup>°</sup>

#### Improved matching in timing jitter Case2: 1 GHz 50mV p2p sinusoidal noise on power rail

#### Remarks

- Wherein with new proposed solution one can come close to jitter seen with spice netlist

- To further improve the accuracy more variation in power voltage may be included to account for PSNIJ

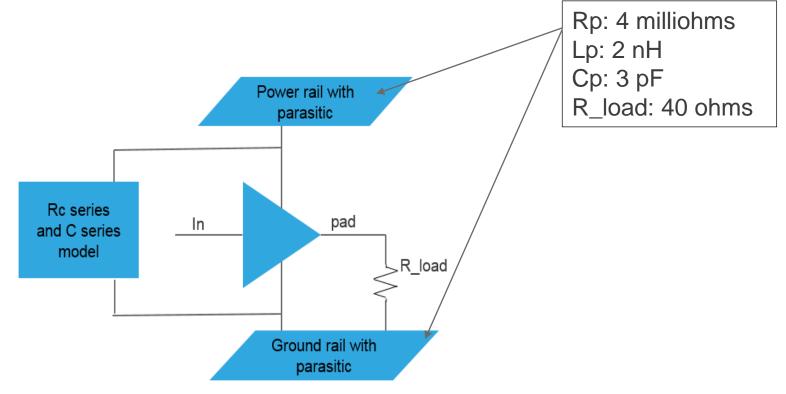

### **Proposed solution for Case2**

- R and C between power and ground have to be explored in order to match impedance between power and ground plane

- Setup with Rc series and C series model added to IBIS 5.1 model

#### cādence

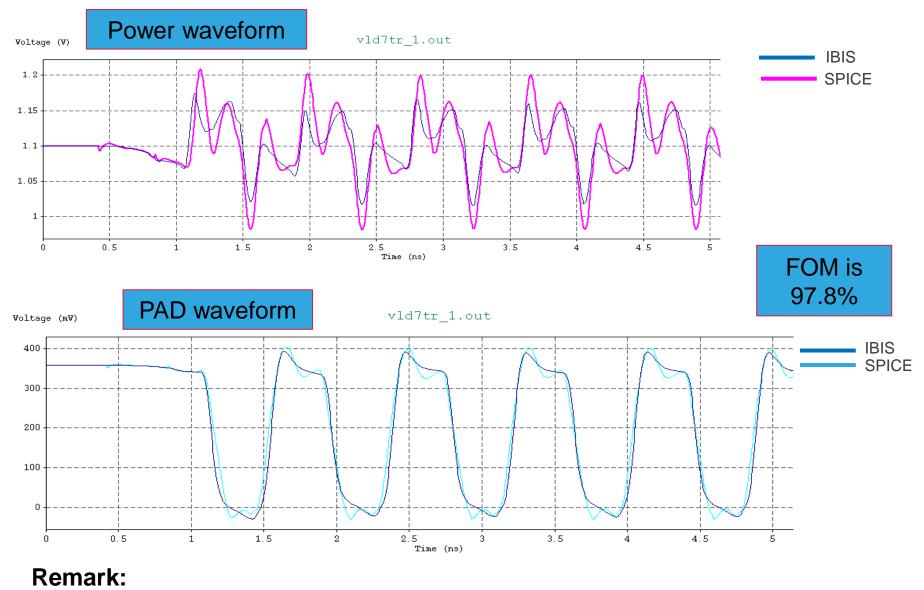

### IBIS 5.1 + Rc series and C series

[End]

cadence®

#### With IBIS 5.1 + [Rc and C series] model

More accurate RC model can be computed using computational algorithms

cādence

## Summary

## Summary

- Such storage of power voltage variation and storage of delay can be dumped into a file and this file can be used to show the variation of timing jitter by EDA tool

- Series model can be calculated by EDA tool to match the impedance of power and ground

# cādence®