# Achieving Full System Signal Integrity for High Speed Backplane System

Dr. Wenliang Dai Xpeedic Technology Co., Ltd.

> Asian IBIS Summit Taipei, Taiwan November 14, 2016

#### **Outline**

- Introduction of backplane system

- Challenge to backplane system simulation

- Components of EM simulation

- Analysis workflow

- Full backplane system SI simulation

- Summary

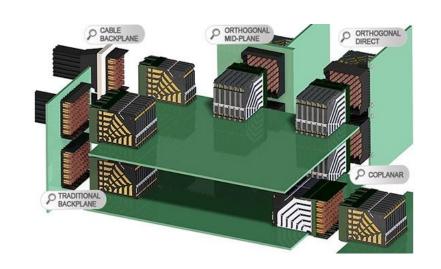

### **Backplane System**

- Backplane system is used as a backbone to connect several printed circuit boards together to make up a complete system

- There are various configurations

- Traditional backplane

- Orthogonal direct

- Orthogonal mid-plane

- Coplanar

- Cable backplane

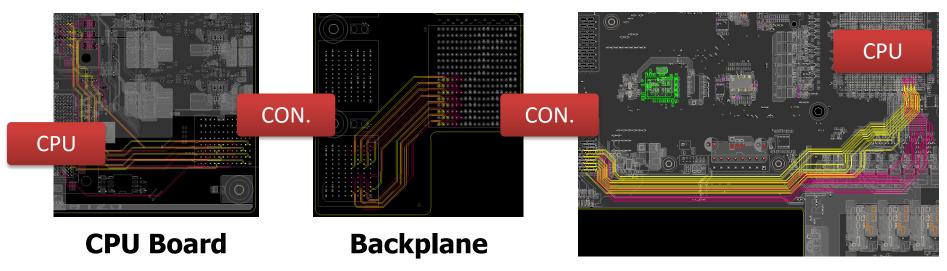

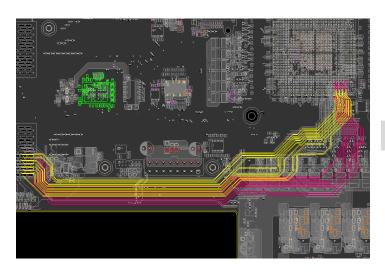

## **Backplane System Example -- Server Board**

- Complex PCB layout.

- Maybe system has capacitor or repeater,

Engineer need to check repeater gain based on channel's loss.

#### **Switch Board**

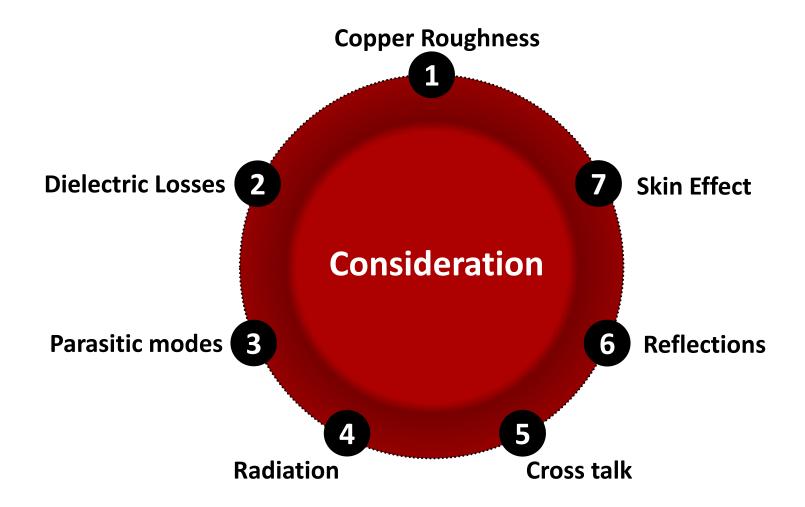

#### **Backplane Design Consideration**

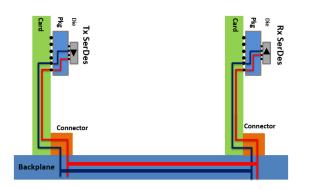

## **Challenges to Channel SI Simulation**

- Reflection noise due to impedance mismatch, via, connector and other discontinuities.

- Need to capture all physical parasitic effects

- Reflection, Coupling, Delay, Freq. dependent Losses,...

- Measurements become very difficult,

- Parasitic values are small but important at high speed.

- Large number of ports for interconnects.

- EM simulation of the discontinuities is a must. However, the current flow suffers the following problems:

- Manual process to extract the via, trace, and other discontinuities

- Manual process to build all the channels

#### **Components of EM Simulation**

✓ Transmitter

✓ Interconnect

• Thru Via

- Transistors

- Sources

- Algorithms

- Passives

- Memory

- BB Via

- Microstrip

- Stripline

- Capacitor

- Repeater

- Connector

- Backdrill

Receiver

- Sources

- Passives

- Memory

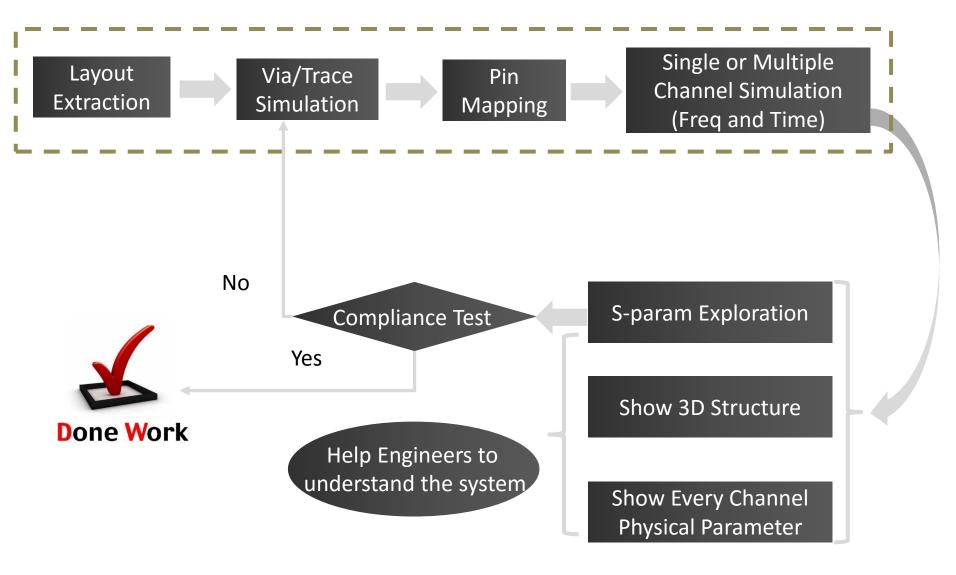

### **Analysis Workflow**

### **Analysis Workflow**

**Seamless Integration**

**Friendly User Interface**

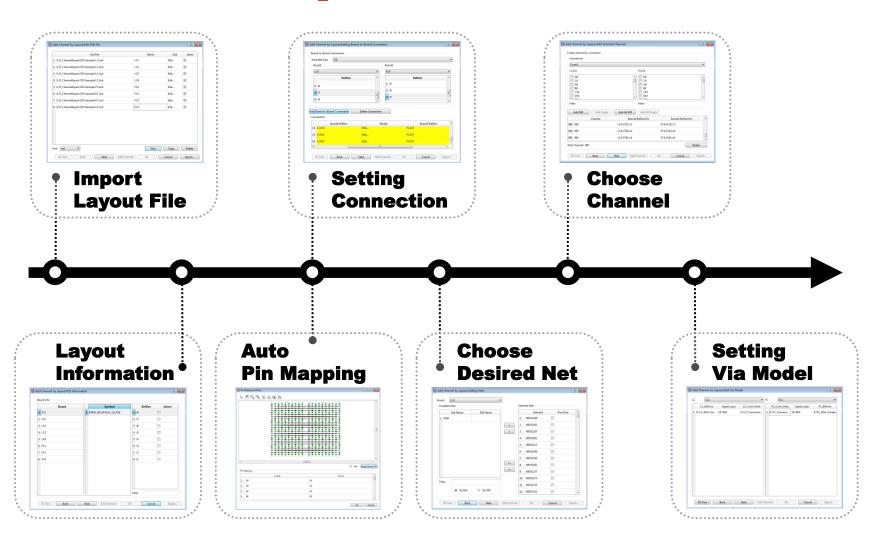

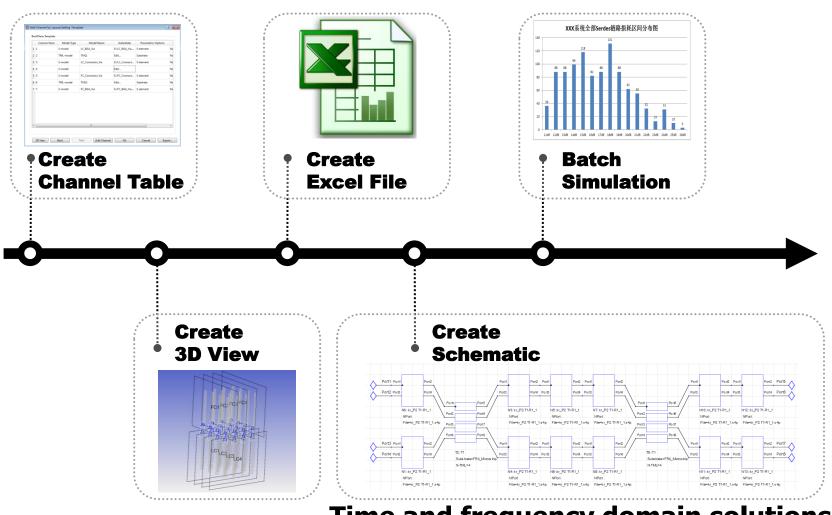

### **Analysis Workflow**

#### Time and frequency domain solutions

S-parameter, Crosstalk analysis, TDR, Eye diagrams

#### **Post-Layout Extraction**

- Import all the boards for the backplane system

- Extract vias and traces from layout

- Layout Files

- Model Template

- Self cleaning process

- Discrete components

- Area/Net selection

- Stackup definition

- Materials definition

- BB, Back drill definition

- Auto port definition

- Parameter/Optimization

- High flexibility

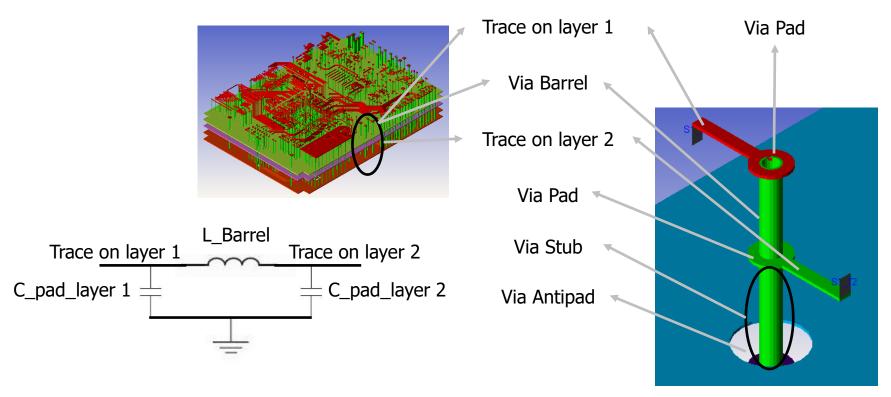

#### 3D Via Modeling

- Via and ground plane will lead to parasitic capacitance and parasitic inductance.

- How to deal with a lot of via models?

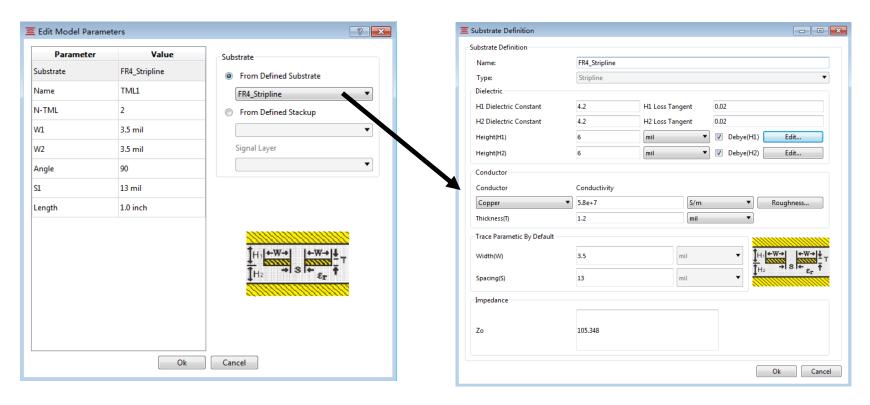

#### **Trace Modeling**

For trace, the common approach is to use 2D models for main high speed interconnect.

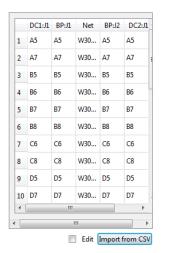

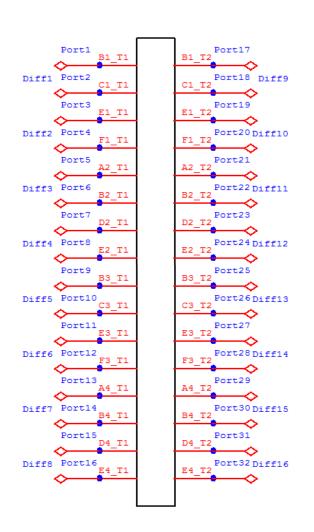

# Connection between Boards through Pin Mapping

- Import .csv file.

- Create connection manually

- Create connection base on slot ID.

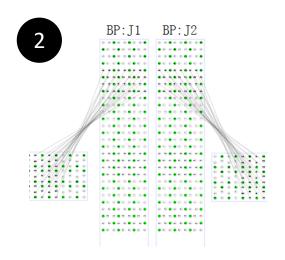

### Connector S-parameter from Vendor

Connector S-parameter file comes from vendor

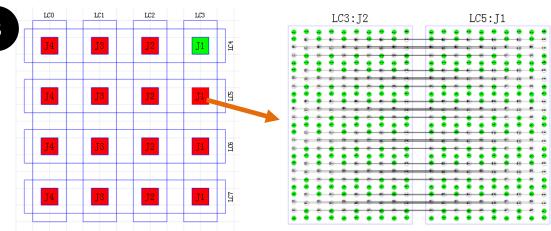

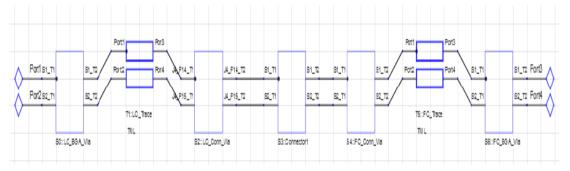

#### **Auto Cascading to Create Channel**

#### **Channelview**

#### Cascading

| LC_Design | LC_Diff         | LC_BGA_VIA        | LC_Stackup  | LC_layer | LC_Length: | )iffLineV | DiffLine | LC_CONN_VIA         | Connector           | FC_Design | r FC_CONN_VIA       | FC_Diff           | FC_Stackup  | FC_layer | C_Lengt | DiffLineW | DiffLine | FC_BGA_VIA        | Total Length |

|-----------|-----------------|-------------------|-------------|----------|------------|-----------|----------|---------------------|---------------------|-----------|---------------------|-------------------|-------------|----------|---------|-----------|----------|-------------------|--------------|

| LC0       | 0_Net1P/LC0_Net | E:\democase\antip | LCO_Stackup | L8       | 1000       | 5         | 4        | E:\democase\antipad | E:\democase\antipad | FC0       | E:\democase\antipad | CO_Net1P/FCO_Net1 | FC0_Stackup | L2       | 2000    | 6         | 5        | E:\democase\antij | 3000         |

| LC1       | 0_Net2P/LC0_Net | E:\democase\antip | LC1_Stackup | L8       | 1500       | 5         | 4        | E:\democase\antipad | E:\democase\antipad | FC1       | E:\democase\antipad | CO_Net2P/FCO_Net2 | FC1_Stackup | L6       | 3000    | 6         | 5        | E:\democase\antij | 4500         |

| LC2       | 0_Net3P/LC0_Net | E:\democase\antip | LC2_Stackup | L8       | 1500       | 5         | 4        | E:\democase\antipad | E:\democase\antipad | FC2       | E:\democase\antipad | CO_Net3P/FCO_Net3 | FC2_Stackup | L6       | 3000    | 6         | 5        | E:\democase\antij | 4500         |

| LC3       | 0_Net4P/LC0_Net | E:\democase\antip | LC3_Stackup | L8       | 1500       | 5         | 4        | E:\democase\antipad | E:\democase\antipad | FC3       | E:\democase\antipad | CO_Net4P/FCO_Net4 | FC3_Stackup | L6       | 3000    | 6         | 5        | E:\democase\antij | 4500         |

| LC4       | 0_Net5P/LC0_Net | E:\democase\antip | LC4_Stackup | L8       | 1500       | 5         | 4        | E:\democase\antipad | E:\democase\antipad | FC4       | E:\democase\antipad | CO_Net5P/FCO_Net5 | FC4_Stackup | L6       | 3000    | 6         | 5        | E:\democase\antij | 4500         |

| LC5       | 0_Net6P/LC0_Net | E:\democase\antip | LC5_Stackup | L8       | 1500       | 5         | 4        | E:\democase\antipad | E:\democase\antipad | FC5       | E:\democase\antipad | CO_Net6P/FCO_Net6 | FC5_Stackup | L6       | 3000    | 6         | 5        | E:\democase\antij | 4500         |

| LC6       | 0_Net7P/LC0_Net | E:\democase\antip | LC6_Stackup | L8       | 1500       | 5         | 4        | E:\democase\antipad | E:\democase\antipad | FC6       | E:\democase\antipad | CO_Net7P/FCO_Net7 | FC6_Stackup | L6       | 3000    | 6         | 5        | E:\democase\antij | 4500         |

| LC7       | 0_Net8P/LC0_Net | E:\democase\antip | LC7_Stackup | L8       | 1500       | 5         | 4        | E:\democase\antipad | E:\democase\antipad | FC7       | E:\democase\antipad | CO_Net8P/FCO_Net8 | FC7_Stackup | L6       | 3000    | 6         | 5        | E:\democase\antij | 4500         |

#### **Excel File**

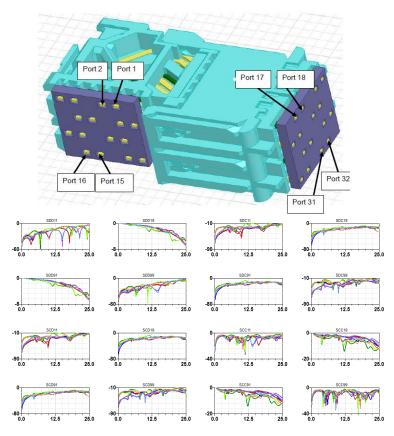

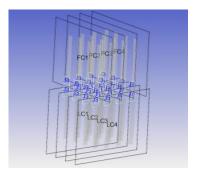

- 3D structure of BP system

- Hide/Show board or net in 3D

- Show entire channel path

- Single vs. multiple simulation and cascading

- Fast and memory efficient

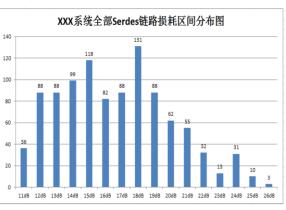

- Show channel's structure size in Excel file

- Easily find worst channel

- Easily generate Excel report

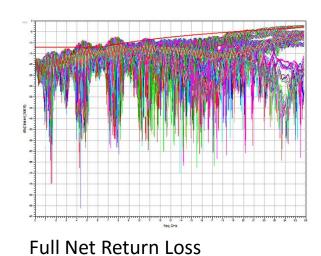

# Full Backplane SI Simulation - Frequency Domain

Full backplane SI simulation is achieved by sweeping all the channels

Full Net Insertion Loss

Net Distribution @ 13.67 GHz

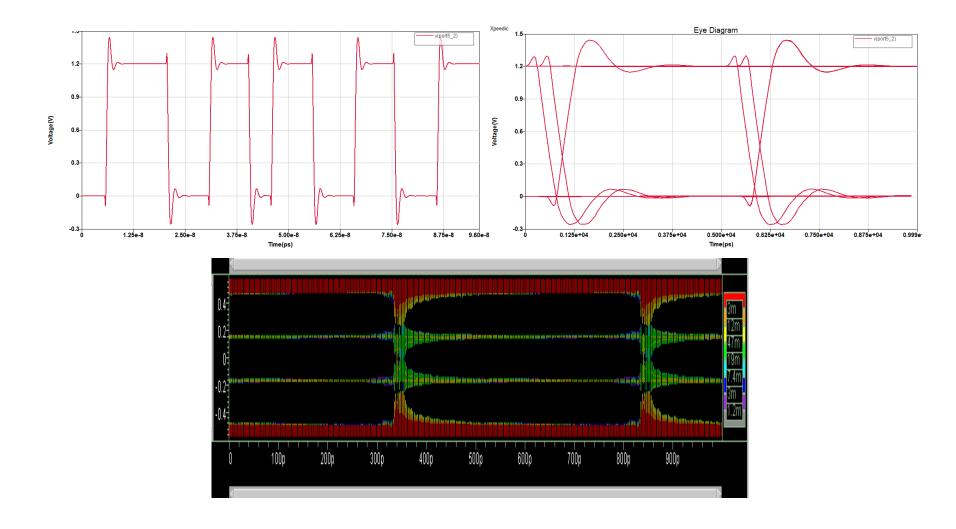

# Full Backplane SI Simulation - Time Domain

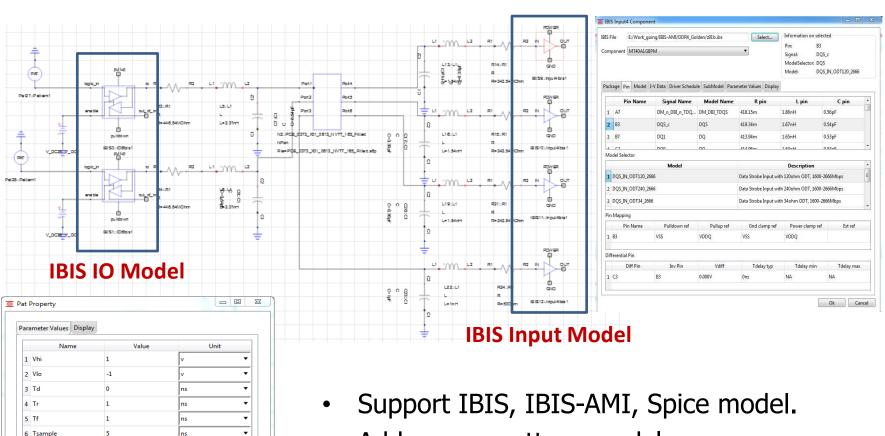

- Add proper pattern model.

- Fast modeling and high accuracy.

# Full Backplane SI Simulation - Time Domain

#### **Summary**

- Passive channel modeling and simulation is essential to high speed channel design.

- Optimal channel design requires user friendly EDA tool to do layout extraction, via optimization, trace simulation, S-parameter cascading, S-parameter exploration, etc.

- Full backplane system SI simulation is achieved by sweeping all the channels with correct models.