## IBIS-AMI Model Generation -With Quality

Skipper Liang Asian IBIS Summit, Shanghai, China November 11, 2016

cādence<sup>®</sup>

### Agenda

#### **Circuit Simulation**

Channel simulation LTI system Channel simulation

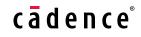

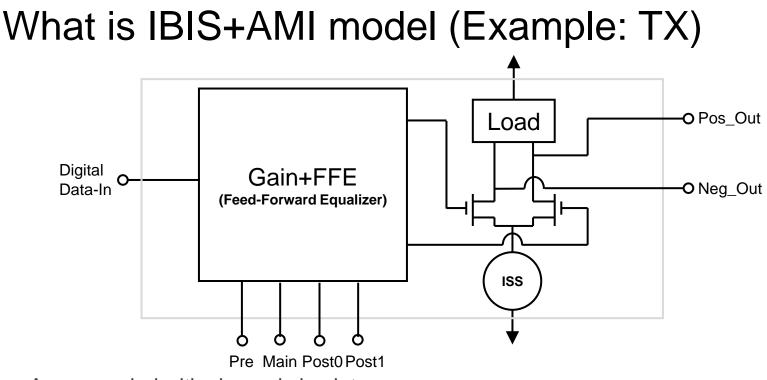

IBIS+AMI model What is IBIS+AMI model And your concerns?

IBIS+AMI model generation flow – Validation is the KEY!!

cadence

#### Successful Stories:

- 1. TX An Output Buffer + FFE

- 2. RX An Input Buffer + AGC + CTE

- 3. A System TX + Channel + RX

### Agenda

#### **Circuit Simulation**

Channel simulation LTI system

BIS+AMI model What is IBIS+AMI mode

#### IBIS+AMI model generation flow – Validation is the KEY!!

#### **Successful Stories:**

- 1. TX An Output Buffer + FFE

- 2. RX An Input Buffer + AGC + CTE

- A System TV & Channel & DV

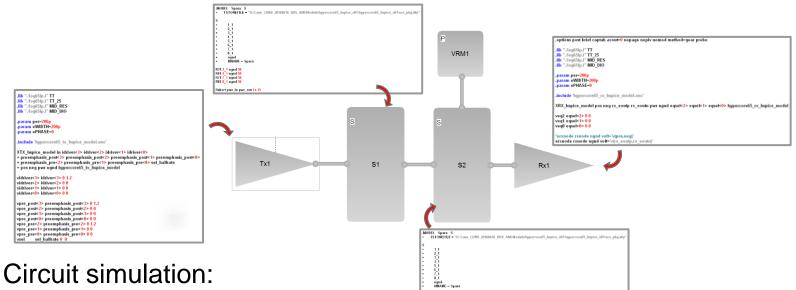

### **Circuit Simulation**-Using transistor **SPICE netlist** model

1 ngnd 5 1 ngnd 5 1 ngnd 5 1 ngnd 5 R31 R41 R71 R81

- Circuit simulation: •

- Kirchhoff's current law (KCL) 1.

At any node (junction) in an electrical circuit, the sum of current flowing into that node is equal to the sum of currents flowing out of that node

#### 2. Kirchhoff's voltage law (KVL)

The directed sum of the electrical potential differences (voltage) around any closed network is zero

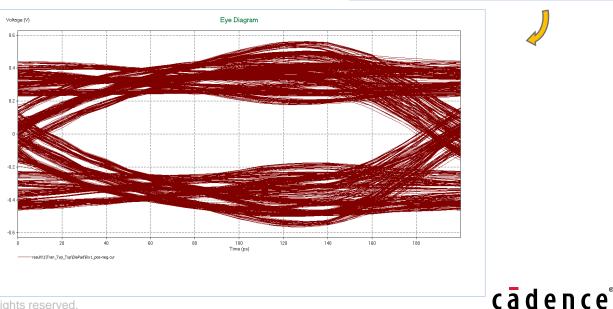

### Traditional signoff flow – Using transistor **SPICE netlist** model (con't)

#### Advantages:

- Accurate PI prediction under <u>limited</u> bits transmission

- Accurate jitter prediction under <u>limited</u> bits transmission

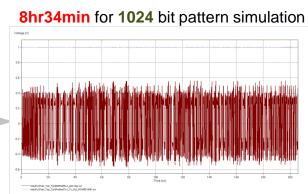

#### **Disadvantages:**

- Very slow for SPICE netlist model - Takes weeks/months to get bit error-rate (BER) prediction

- Can't model the adaptive mechanism in RX

### Agenda

#### **Circuit Simulation**

Channel simulation LTI system Channel simulation

BIS+AMI model What is IBIS+AMI mode And your concerns?

#### IBIS+AMI model generation flow – Validation is the KEY!!

#### **Successful Stories:**

- 1. TX An Output Buffer + FFE

- 2. RX An Input Buffer + AGC + CTE

- A System TY & Channel & DY

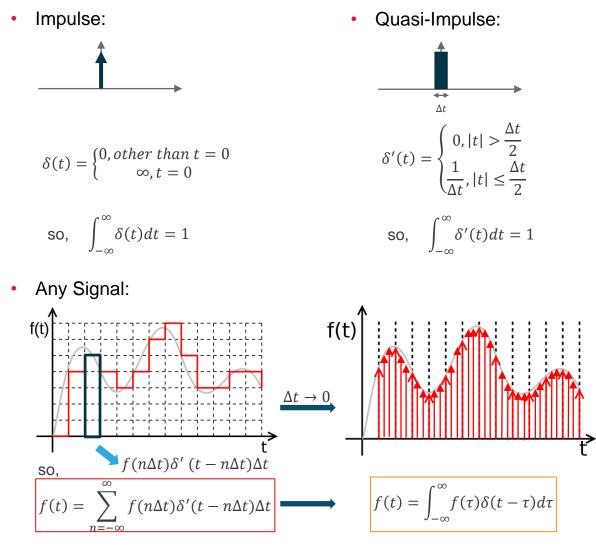

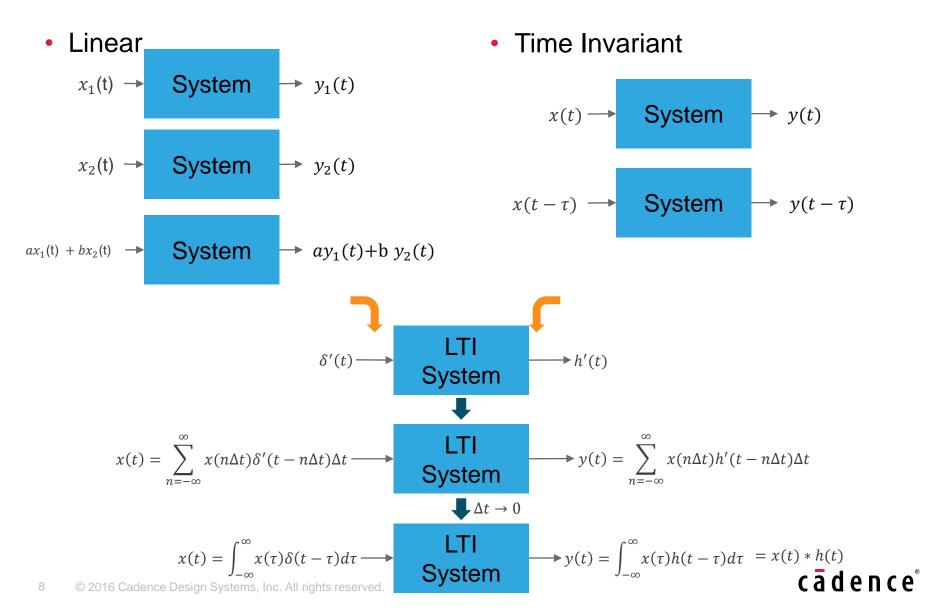

### LTI – Linear time invariant (con't.)

Signal expressed in an impulse-train format:

### LTI – Linear time invariant (Con't.)

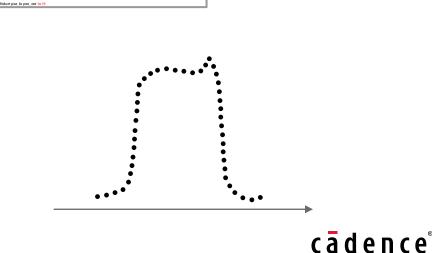

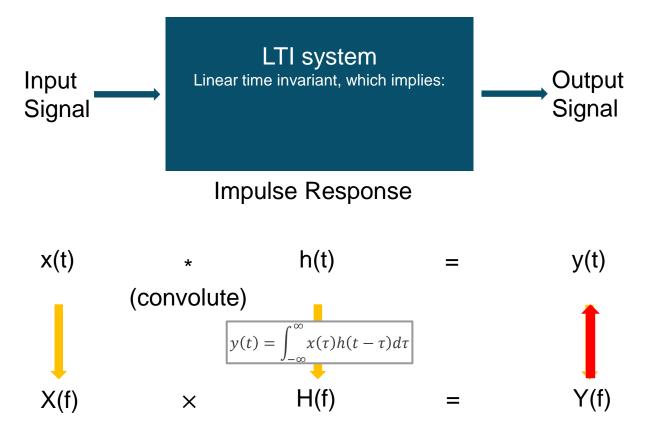

### **Channel-Simulation**

Channel simulation :

Multi-times faster than circuit simulation!!

### Agenda

#### **Circuit Simulation**

Channel simulation LTI system

IBIS+AMI model What is IBIS+AMI model And your concerns?

#### **IBIS+AMI** model generation flow – Validation is the KEY!!

#### **Successful Stories:**

- 1. TX An Output Buffer + FFE

- 2. RX An Input Buffer + AGC + CTE

- A System TV & Channel & DV

Accompanied with channel simulator:

- PI prediction with good accuracy without limits on transmission bits

- Jitter prediction with good accuracy without limits on transmission bits

- Very fast for IBIS+AMI netlist model -Takes minutes to get BER prediction

- Can model the adaptive mechanism in RX

#### cādence°

- PI prediction with good accuracy without ٠ limits on transmission bits

- Jitter prediction with good accuracy ٠ without limits on transmission bits

- Very fast for IBIS+AMI netlist model -٠ Takes minutes to get BER prediction

- Can model the adaptive mechanism in • RX

But you might be concerned:

### Agenda

#### **Circuit Simulation**

Channel simulation LTI system

BIS+AMI model What is IBIS+AMI mode And your concerns?

#### IBIS+AMI model generation flow – Validation is the KEY!!

#### **Successful Stories:**

- 1. TX An Output Buffer + FFE

- 2. RX An Input Buffer + AGC + CTE

- A System TY & Chennel & DY

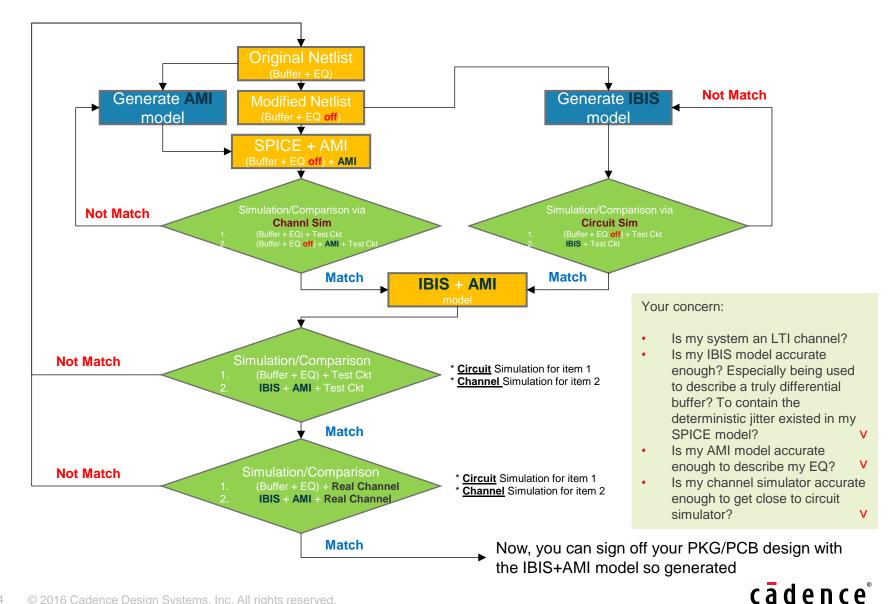

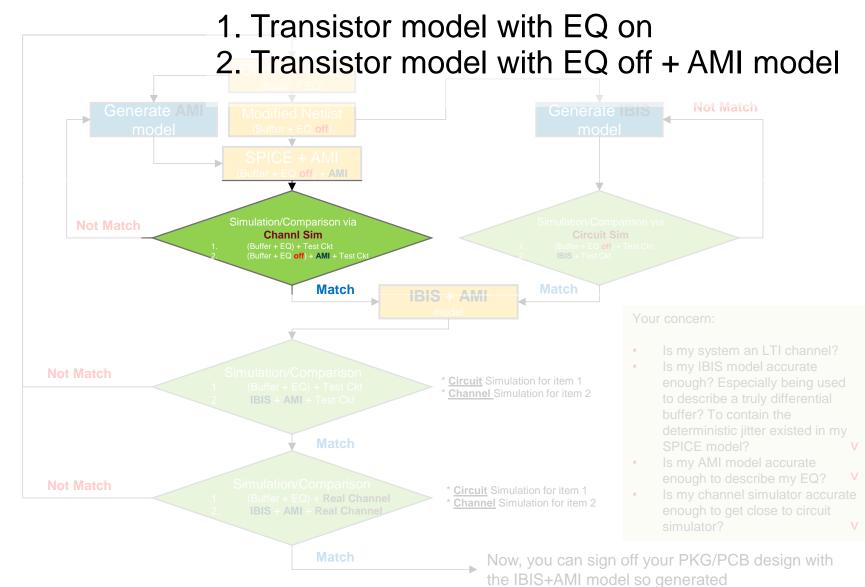

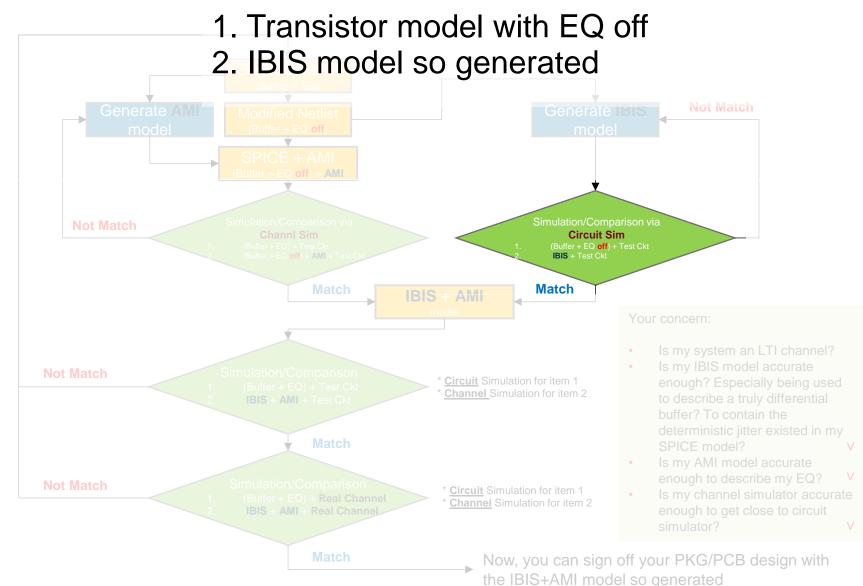

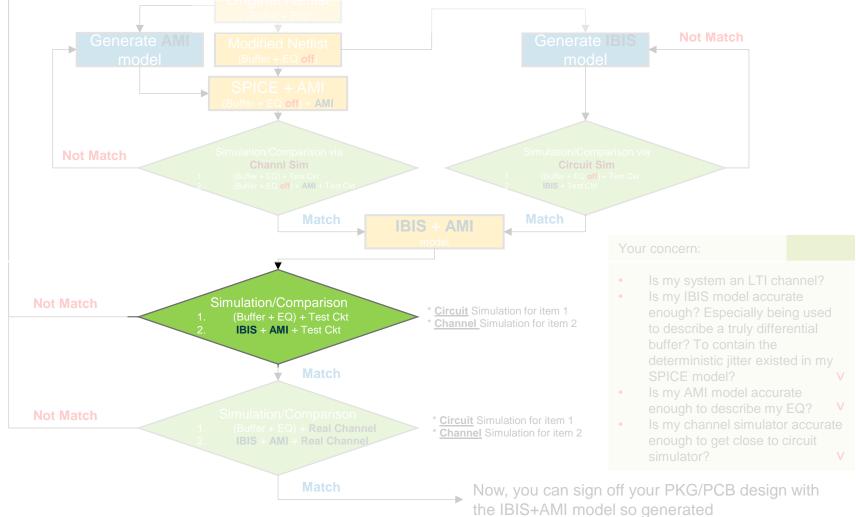

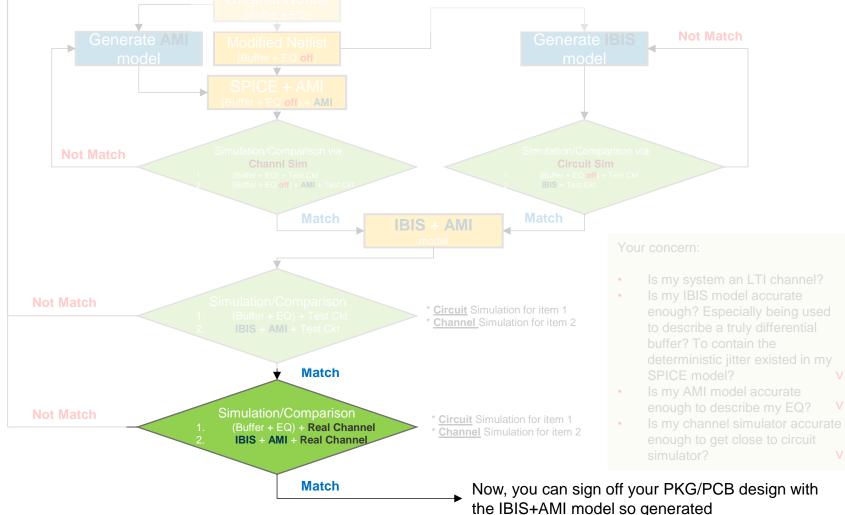

### **IBIS+AMI** model generation flow

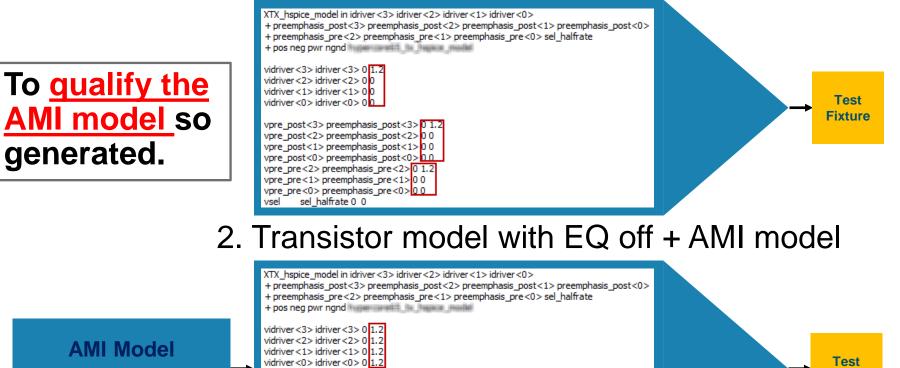

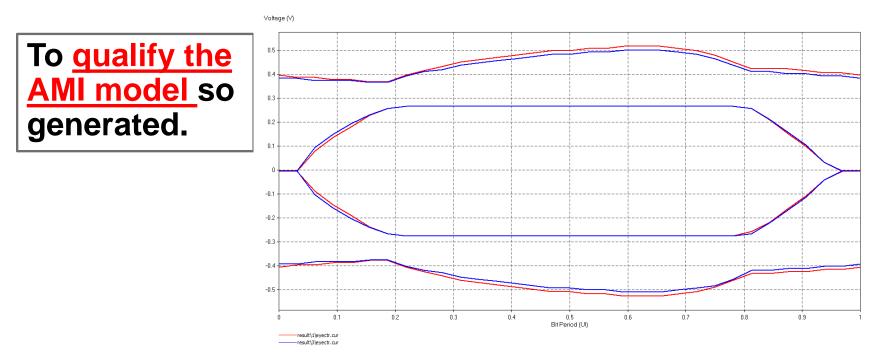

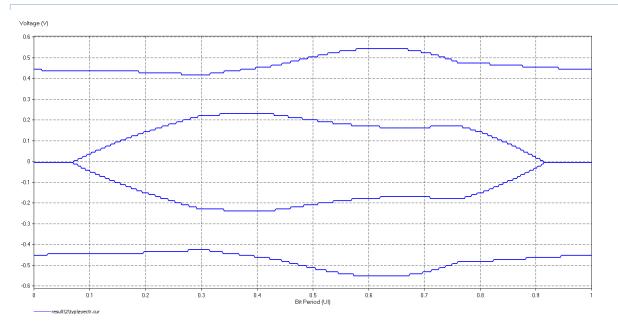

### Validation 1: Channel Simulation for

#### cādence<sup>®</sup>

### Validation 1: Channel Simulation for

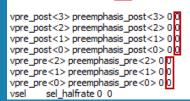

#### 1. Transistor model with EQ on

**Fixture**

### Validation 1: Channel Simulation for

Transistor model with EQ on

Transistor model with EQ off + AMI model

Why Channel Simulation?:

- 1. AMI model can only be used in **Channel Simulation**

- 2. Put transistor models under **Channel Simulation** will narrow down the possible cause for any difference happened here to the AMI model so generated.

#### cādence<sup>®</sup>

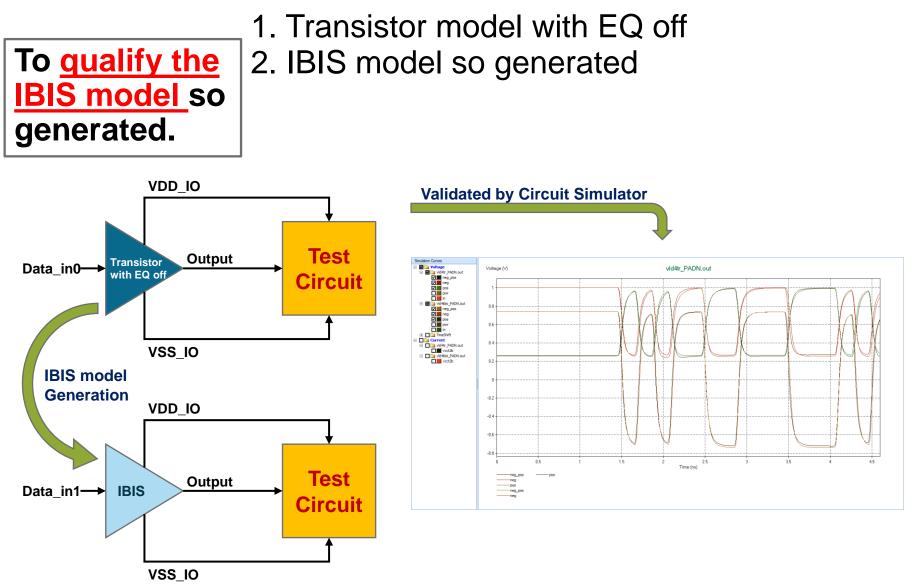

### Validation 2: Circuit Simulation for

cadence

### Validation 2: Circuit Simulation for

cadence

### Validation 2: Circuit Simulation for

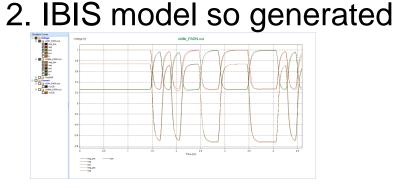

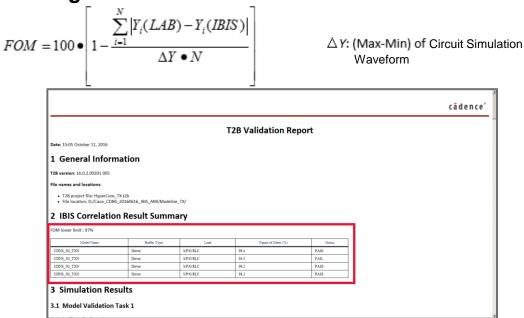

Define a "mark" and a "target" to tell the quality of the IBIS model so generated

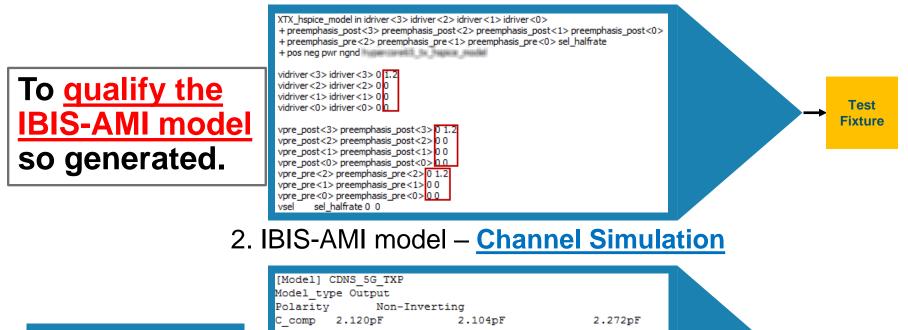

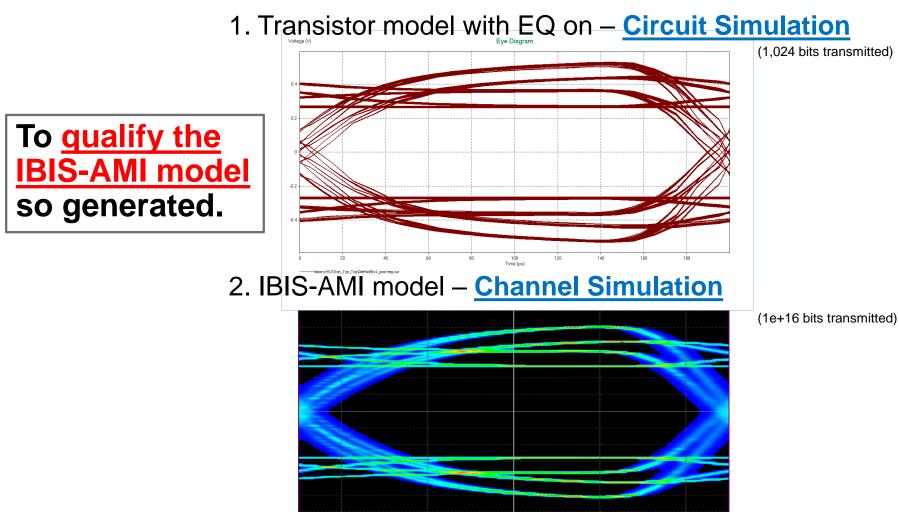

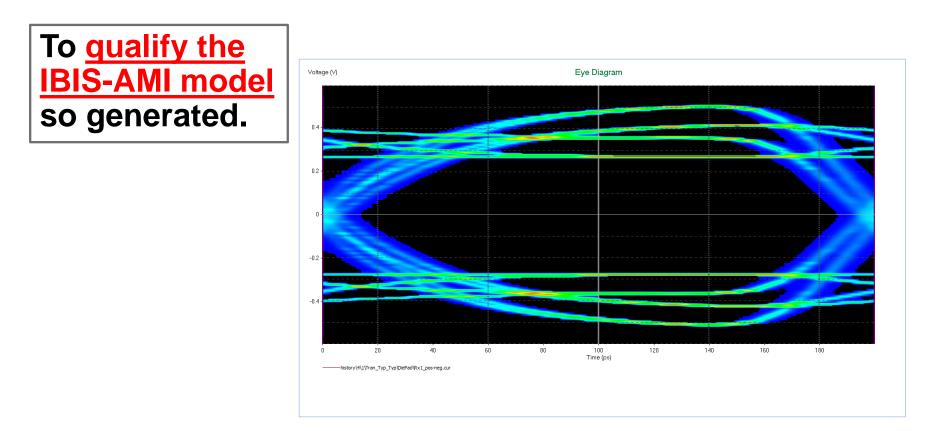

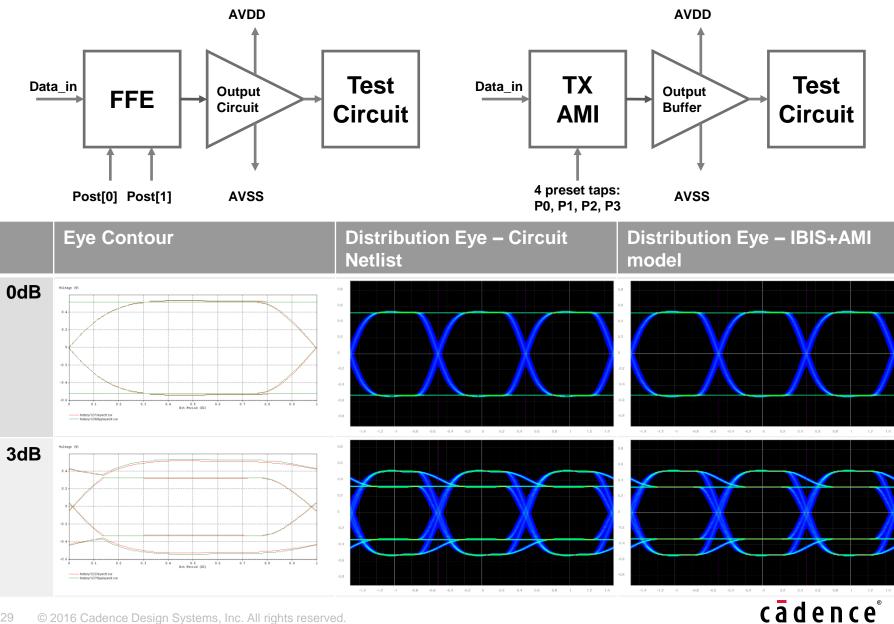

# Transistor model with EQ on – Circuit Simulation IBIS-AMI model – Channel Simulation

cadence

#### 1. Transistor model with EQ on – Circuit Simulation

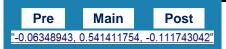

### AMI Model

| C_comp_pullup 0.35      | 4pF    | 0.347pF | 0.36     |  |

|-------------------------|--------|---------|----------|--|

| C_comp_pulldown 0.      | 749pF  | 0.738pF | 0.       |  |

| I                       |        |         |          |  |

| <br>[Temperature Range] | 27.000 | 100.000 |          |  |

| [Voltage Range]         | 1.200V | 1.080V  |          |  |

| [Pulldown]              |        |         |          |  |

| Voltage I(typ)          |        | I(min)  | I(max)   |  |

| 1                       |        |         |          |  |

| -1.200V -1.2082A        | -1     | .4705A  | -1.1135A |  |

| -1.163V -1.0791A        | -1     | .3481A  | -0.9816A |  |

| -1.126V -0.9501A        | -1     | .2258A  | -0.8511A |  |

Test Fixture

Transistor model with EQ on – Circuit Simulation

IBIS-AMI model – Channel Simulation

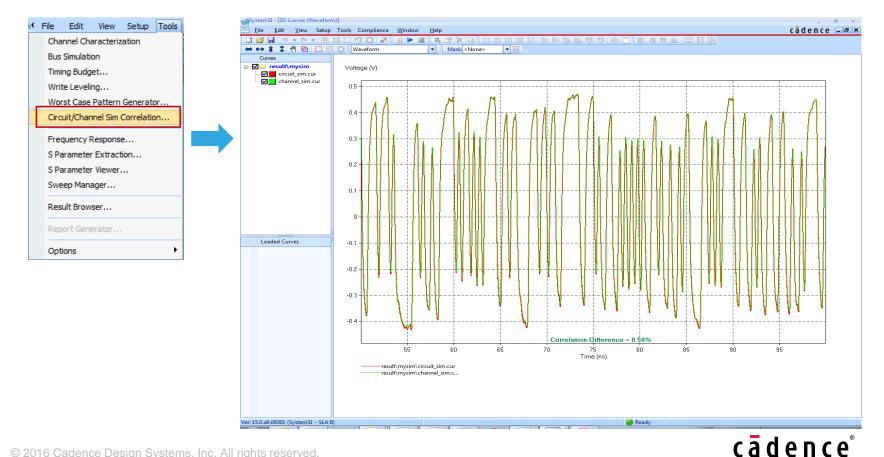

Also, to qualify the Channel Simulator – if the Channel Simulator behavior close enough to the Circuit Simulator.

#### cādence®

### Validation 4: Real Channel follows

# Transistor model with EQ on – Circuit Simulation IBIS-AMI model – Channel Simulation

cadence

### Validation 4: Real Channel follows

1. Transistor model with EQ on – Circuit Simulation 2. IBIS-AMI model – Channel Simulation

First of all, check if your system/channel to be analyzed can be treated as LTI or not:

### Validation 4: Real Channel follows

Transistor model with EQ on – Circuit Simulation

IBIS-AMI model – Channel Simulation

Now, you can sign off your PKG/PCB design with the IBIS+AMI model so generated

### Agenda

#### **Circuit Simulation**

Channel simulation LTI system

BIS+AMI model What is IBIS+AMI mode

#### IBIS+AMI model generation flow – Validation is the KEY!!

#### Successful Stories:

- 1. USB 3.0 TX An Output Buffer + FFE

- 2. USB 3.0 RX An Input Buffer + AGC + CTE

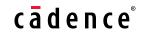

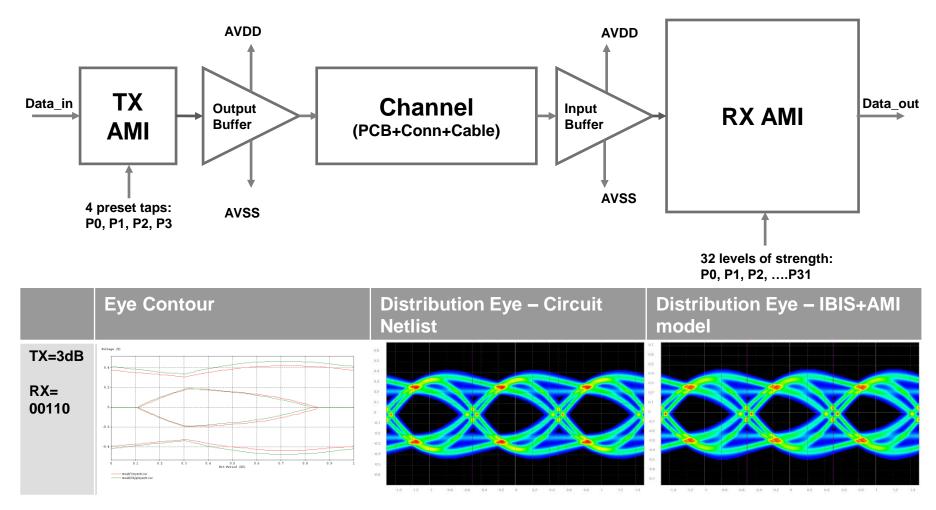

- 3. A System USB 3.0 TX + Channel (PCB+Conn+3m Cable) + USB 3.0 RX

cadence

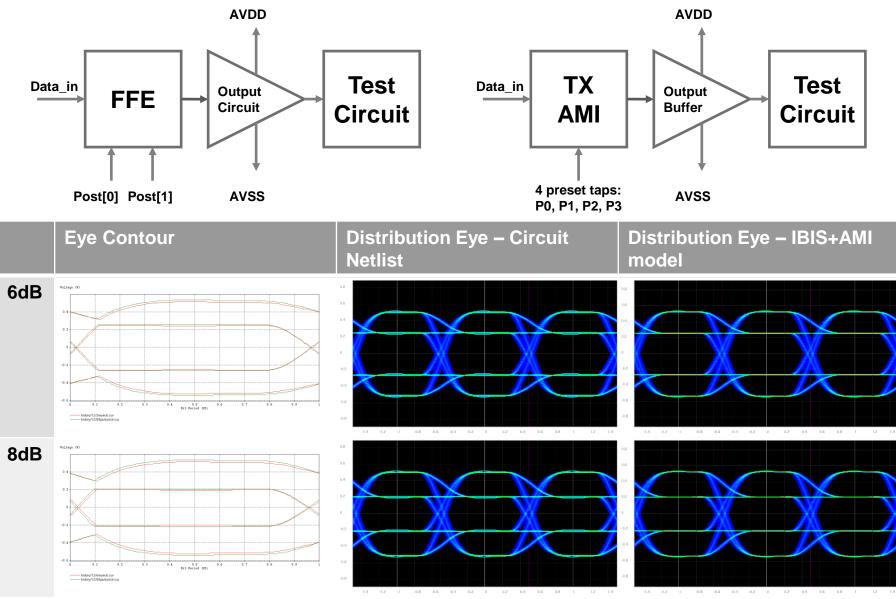

### **USB 3.0 TX**

### **USB 3.0 TX**

30 © 2016 Cadence Design Systems, Inc. All rights reserved.

#### cādence°

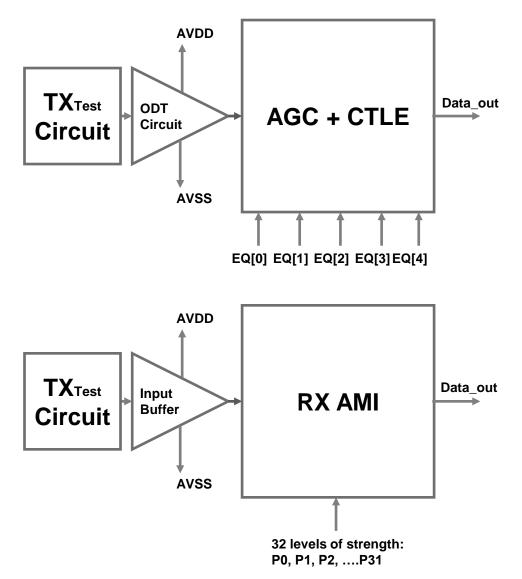

### **USB 3.0 RX**

### **USB 3.0 RX**

© 2016 Cadence Design Systems, Inc. All rights reserved.

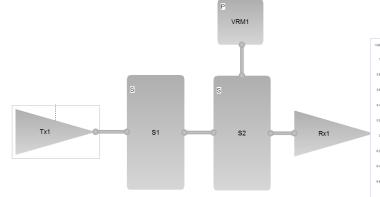

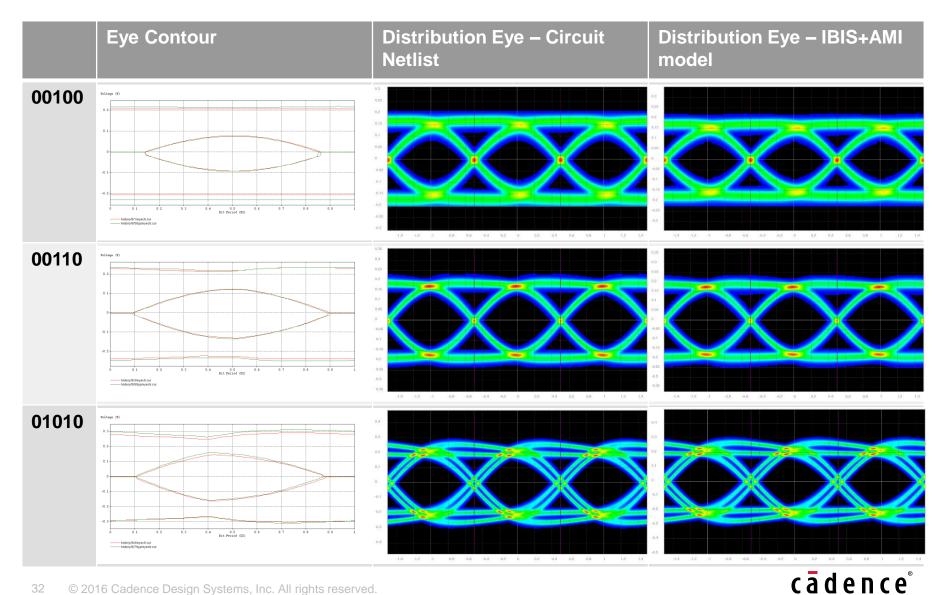

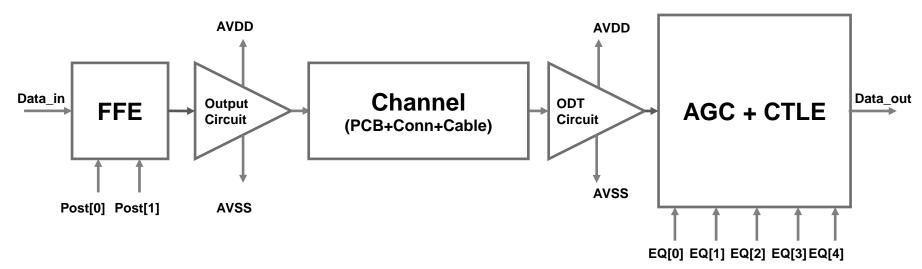

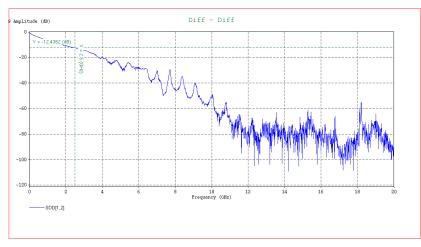

### A System – USB 3.0 TX + Channel + USB 3.0 RX

Channel Insertion Loss

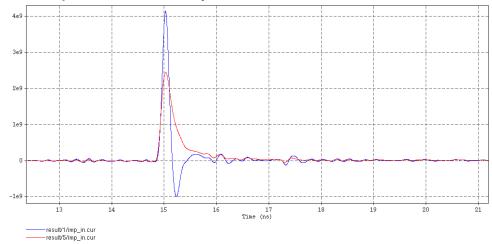

### A System – USB 3.0 TX + Channel + USB 3.0 RX

Impulse Response Improvement – By FFE + AGC + CTLE Circuit

### A System – USB 3.0 TX + Channel + USB 3.0 RX

cādence<sup>®</sup>

### Agenda

#### **Circuit Simulation**

Channel simulation

BIS+AMI model What is IBIS+AMI mode

#### IBIS+AMI model generation flow – Validation is the KEY!!

**Successful Stories:**

- 1. TX An Output Buffer + FFE

- 2. RX An Input Buffer + AGC + CTE

A System TY & Channel & DY

- An accurate IBIS+AMI model could be an alternative approach to validate your "system" design versus a transistor netlist model

- An accurate IBIS-AMI model consists of two parts an <u>accurate IBIS model</u> and <u>an</u> <u>accurate AMI model</u> – validation is the key

- An accurate IBIS should be generated by a tool which can well describe a <u>truly</u> <u>differential pair</u> in all V/I, V/T and I/T curves.

- An accurate AMI model should be generated by a tool with a rich library such that the generation tool can use all available means in the library to describe all your possible designs.

- A simulation environment which supports transistor netlist models is fundamental for IBIS+AMI model generation/validation.

# cādence<sup>®</sup>

© 2016 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo and Spectre are registered trademarks and Sigrity, SystemSI, and T2B are trademarks of Cadence Design Systems, Inc. in the United States and other countries. All rights reserved. All other trademarks are the property of their respective owners.