# Differential Modeling Flow with Series Model in Verilog-A

Asian IBIS Summit Shanghai, China November 11, 2016

Wei-hsing Huang, SPISim

<u>Wei-hsing.Huang@spisim.com</u>

Sanjeev Gupta, SigIntegrity-Solutions

<u>sanjeev@sigintegrity-solutions.com</u>

#### Agenda:

- Background & Motivation

- Verilog-A based modeling

- Differential current

- External model

- Flow & Validation

- Summary

- Q & A

#### Background: (1, IBIS CookBook V4)

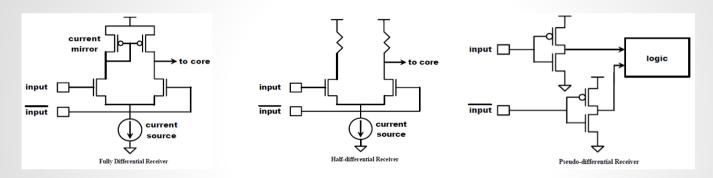

• Differential buffer: True/Half/Pseudo differential.

• [Diff Pin]: describe differential behavior between two pins.

```

[Diff Pin] inv_pin vdiff tdelay_typ tdelay_min tdelay_max

| 2 3 NA NA 0ns 5ns

6 5 NA NA 0ns 5ns

```

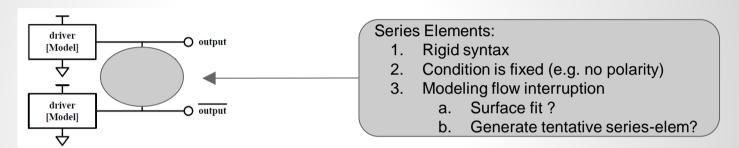

#### **Method 1 for Half/True differential:**

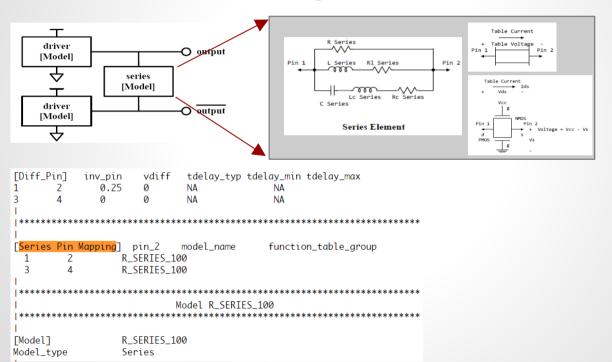

[Series pin mapping]/Series Model:(2)(3)

#### Method 2 for Half/True differential:

[External Model]: Spice/VHDL-AMS/Verilog-AMS/IBIS-ISS(4)

```

[Model]

VHDI AMS-DRV

Model_type

Output

Polarity

Non-Invertina

6.00pF

C comp

4.60pF

3.50pF

Vmeas = 1.15V

Cref = 1pF

Input diff

Rref = 50 ohms

These model types specify that the model defines a true

Output diff

Vref = 0V

differential model available directly through the

I/O diff

[External Model] keyword documented in Section 6.3.

3-state diff

[External Model]

Language VHDL-AMS

I Corner corner_name file_name

circuit_name entity(architecture)

Typ

ideal driver.vhd

driver_ideal(linear)

Corner

ideal_driver.vhd

driver_ideal(linear)

Corner

Min

Max

ideal driver.vhd

driver_ideal(linear)

Corner

I Ports List of port names (in same order as in VHDL-AMS)

Ports D_drive A_puref A_pdref A_signal

```

Method 1 & 2 can be used together!

[End External Model]

# **Background:**

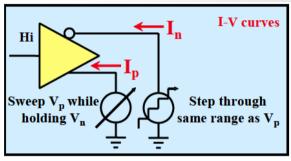

#### Data extraction:

- Common-mode current

- Differential current

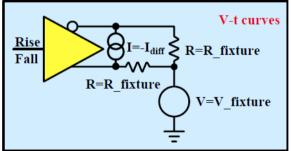

Figure 4.13 - I-V Table Extraction Fixture for a Differential Buffer

Figure 4.18 – V-T Table Extraction Fixture for a Differential Buffer

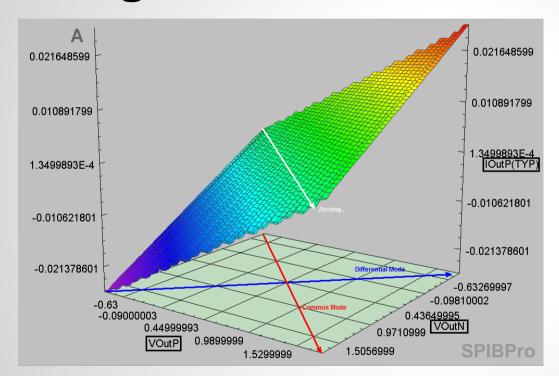

### Design 1:

I Comm. Mode as PU/PD, PC/GC

A simple "Series R" can describe this particular design

Shifted surface as differential series elem.

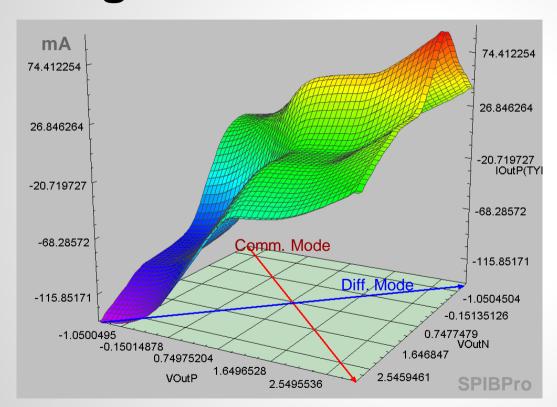

### Design 2:

Need to describe this surface data in design 2 for V-T extraction Affect DC steady states (e.g. mismatch)

#### Options:

- Surface fit in MSE sense:

- Need to check residue

- Translate to EFGH elements

- Series MOSFET

- Or Series current

- Behavioral model?

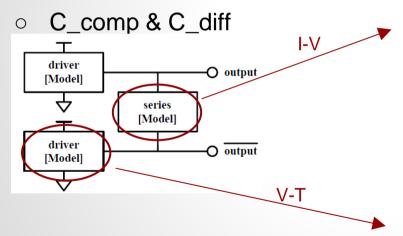

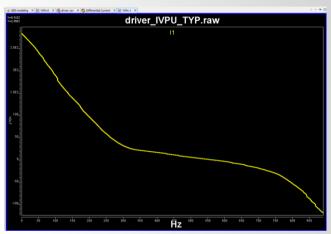

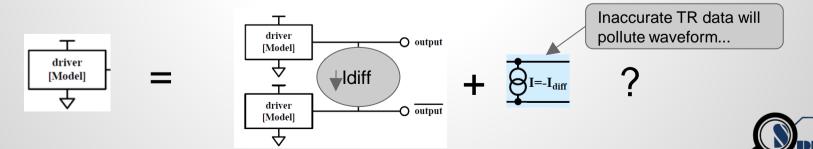

# Design 2 C\_diff:

#### **Motivations:**

Limitation of "Generic" series model:

Accuracy of transient data for V-T extraction:

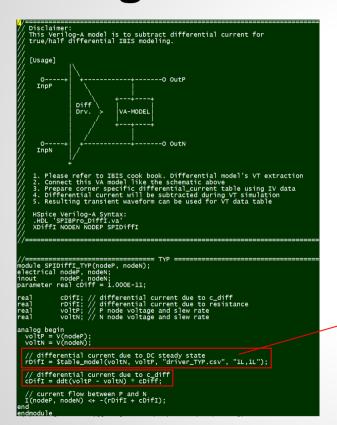

#### Verilog-A based Diff. current model:

A Verilog-A device can be used in differential V-T extraction.

- Behavioral device is very versatile

- Support operator like ddt, if .. else

- Supports 1/2D look-up table **(5)**, **(6)**

```

#Differential current in mA

#VOUTN VOUTP IDiff_Typ

-1.50E+00 -1.50E+00 0.00E+00

-1.50E+00 -1.46E+00 -7.83E+00

-1.50E+00 -1.41E+00 -1.59E+01

-1.50E+00 -1.37E+00 -2.41E+01

-1.50E+00 -1.32E+00 -3.25E+01

-1.50E+00 -1.28E+00 -4.13E+01

-1.50E+00 -1.28E+00 -5.03E+01

-1.50E+00 -1.19E+00 -5.95E+01

-1.50E+00 -1.19E+00 -6.91E+01

-1.50E+00 -1.10E+00 -7.89E+01

-1.50E+00 -1.05E+00 -8.90E+01

-1.50E+00 -1.01E+00 -9.94E+01

-1.50E+00 -1.01E+00 -9.94E+01

```

# **Verilog-A for V-T extraction:**

Voltage & freq. Dependent C\_Diff (or use cross() to find freq. dynamically)

Simulator only supports 1D table? 2D bi-linear look-up can still be done

```

module SPIDiffI_TYP(nodeP. nodeN):

electrical nodeP. nodeN:

nodeP. nodeN:

parameter real freq = 1.0E9; // current working frequency

parameter real freq1 = 5.0E8; // cdiff at frequency 1

parameter real freq2 = 2.0E9; // cdiff at frequency 2

cDifI; // differential current due to c_diff

rDifI; // differential current due to resistance

rea1

voltP; // P node voltage and slew rate

voltN; // N node voltage and slew rate

cDif1, cDif2, cDiff; // differential capacitance

real

real

analog begin

voltP = V(nodeP);

voltN = V(nodeN);

// differential current due to DC steady state

rDifI = $table_model(voltN - voltP, "driver_TYP.csv", "1L,1L");

// differential current due to c_diff

cbiff1 = Stable_model(volth, "driver_CDIF1.csv", "1L,1L"); // at freq1 = 500M

cDiff2 = Stable_model(volth, "driver_CDIF2.csv", "1L,1L"); // at freq2 = 2G

cDiff = (cDiff2 - cDiff1) / (freq2 - freq1) * (freq - freq1) + cDiff1;

cDifI = ddt(voltP - voltN) * cDiff;

```

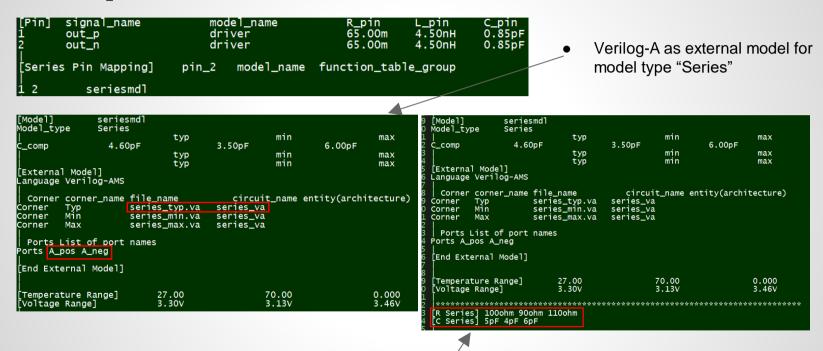

# **Completed Series model:**

Verilog-A can work with existing (generic) series model to provide extra accuracy if needed.

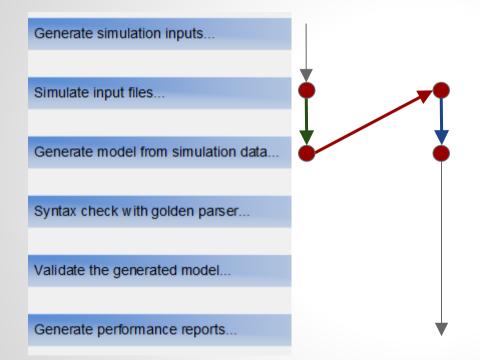

### Differential modeling flow:

- DC sweep for I-V PU/PD/PC/GC

- AC sweep for C\_Comp/C\_Diff

- Post-processing to calc DC I\_Diff

- Post-processing to calc C\_Diff

- Generate table .csv and .va file

Simulate remaining V-T with diff. I subtracted

### **Modeling flow validation:**

- Use an existing single-ended driver for P and N

- Insert approximate non-linear behavioral R/L/C elements between P and N outputs

- Flow should recreate same PU/PD/PC/GC as driver

- I-V surface plot should reveal inserted resistance

- C\_Diff/C\_Comp surface should reveal inserted cap

- Correlations of V-T table depends on I\_Diff accuracies.

### **Summary:**

- Verilog-A for differential V-T extraction

- Versatile, supports many operators

- E.g. ddt(Vx), \$table\_model for 1D/2D lookup

- Streamlines modeling flow

- Extract transient differential current

- Improve V-T extraction accuracies

- Use Verilog-A to remove rigid series syntax

- External model for "Series":

- [External model] supports "Series" type model

- Can work with generic series model

#### References:

1. IBIS Cookbook V4

https://ibis.org/cookbook/cookbook-v4.pdf

2. IBIS summit Jan/Mar 2001 by Hazem Hegazy (Mentor)

https://ibis.org/summits/jan01/hegazy.zip https://ibis.org/summits/mar01/hegazy.zip

3. IBIS summit 2002 ~ 2004 by Arpad Muranyi (Intel)

https://ibis.org/summits/oct02/muranyi.pdf

https://ibis.org/summits/oct03/muranyi.pdf

https://ibis.org/summits/feb04a/muranyi2.pdf

4. IBIS summit 2014 ~ 2015 by Shivani Shama et. al. (Cadence)

https://ibis.org/summits/nov14b/sharma.pdf https://ibis.org/summits/nov15b/liang.pdf

5. Verilog A Language Reference Manual (LRM, Vendor Specific) <a href="http://accellera.org/images/downloads/standards/v-ams/VAMS-LRM-2-3-1.pdf">http://accellera.org/images/downloads/standards/v-ams/VAMS-LRM-2-3-1.pdf</a>

6. HSpice User's Manual

# **Q & A**