for better quality of experience

# DDR4 SI/PI Analysis Using IBIS5.0

Socionext Inc. Yumiko Sugaya

Asian IBIS Summit, Tokyo, Japan November 16, 2015

- Overview

- DDR4 SI/PI Analysis Issue

- Over Clocking issue

- DDR4 SI/PI Analysis Using IBIS5.0

- Summary

- Expectation for future IBIS

DDR4 SI/PI Analysis Issue

Over Clocking issue

DDR4 SI/PI Analysis Using IBIS5.0

Summary

Expectation for future IBIS

- Because of the Over Clocking issue, we could not use IBIS5.0 for high speed analysis, such as for DDR4.

- Modification of the EDA software has removed the Over Clocking issue.

- Therefore, the accuracy of IBIS5.0 at high speed has improved.

### IBIS5.0 can analyze DDR4 SI/PI with high accuracy in a short time!

#### socionext

# DDR4 SI/PI Analysis Issue

# Over Clocking issue

# DDR4 SI/PI Analysis Using IBIS5.0

Summary

# Expectation for future IBIS

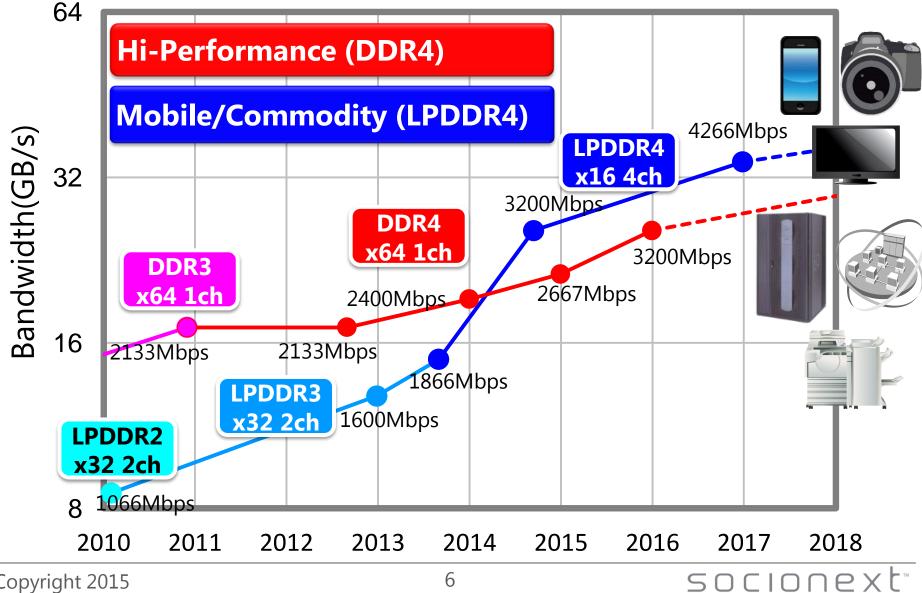

### Memory Trend

#### DDR3 is replaced by DDR4.

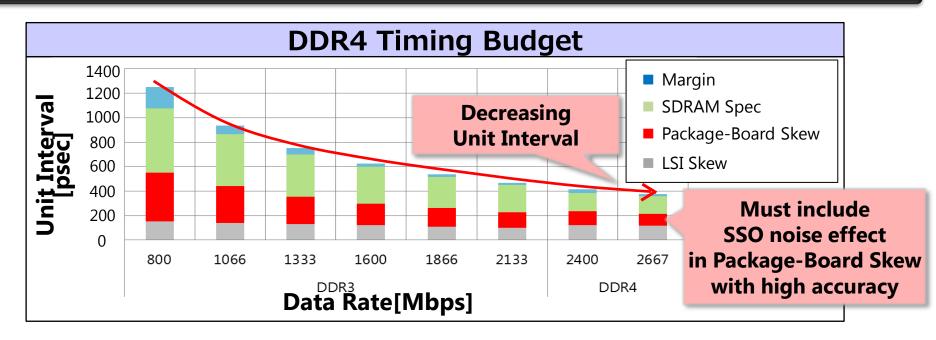

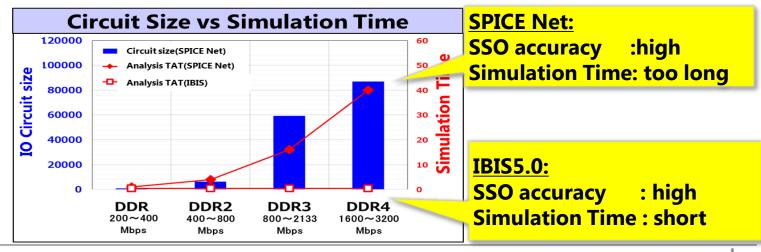

### Necessity of IBIS5.0 for DDR4 simulation

#### IBIS5.0 can analyze SSO noise with high accuracy in a short time.

SOCION

### IBIS5.0 issue

# We solved the Over Clocking issue in cooperate with EDA developer.

Comparison of the simulation models.

|                         | SPICE Net | IBIS4.2 | IBIS5.0 |

|-------------------------|-----------|---------|---------|

| Simulation Time         | Longer    | Shorter | Shorter |

| SSO accuracy            | High      | Low     | High    |

| SI accuracy (~1600Mbps) | High      | High    | High    |

| SI accuracy (1866Mbps~) | High      | High    | Low     |

# DDR4 SI/PI Analysis Issue

# Over Clocking issue

# DDR4 SI/PI Analysis Using IBIS5.0

### Summary

# Expectation for future IBIS

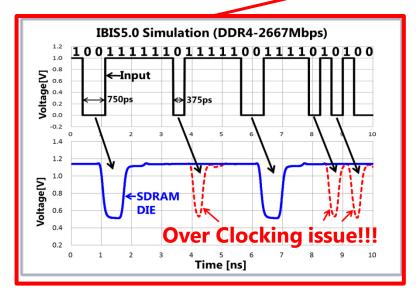

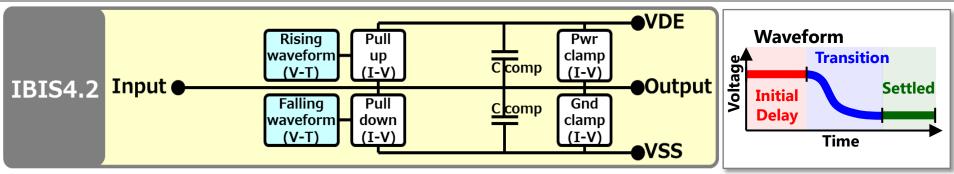

### What is the Over Clocking?

### Old and new issue (Over Clocking)

SOCIONEX

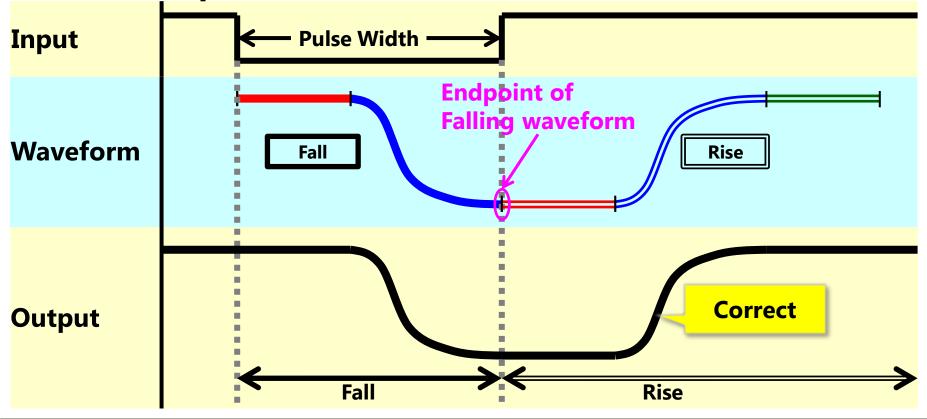

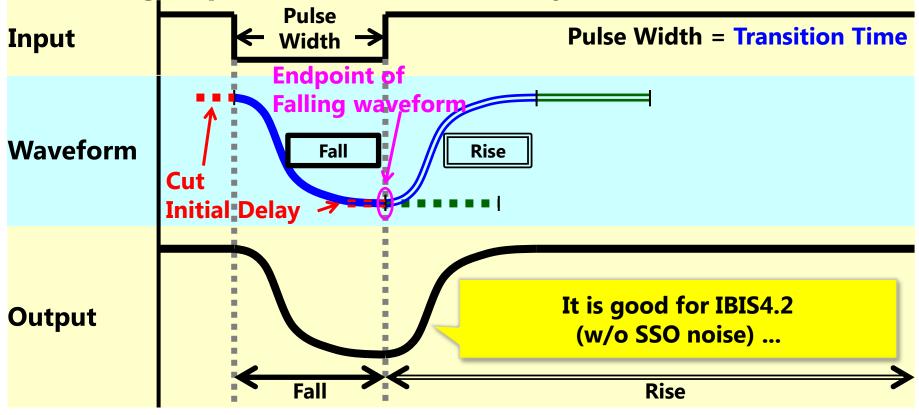

### IBIS Over Clocking mechanism(1/4)

#### ■ IBIS Low Speed Mode Pulse Width ≥ Initial Delay+ Transition Time

Copyright 2015

11

SOCIONEX

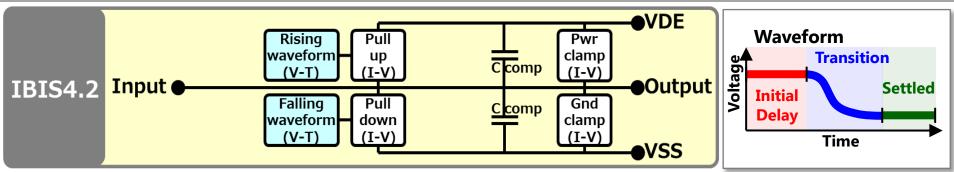

### IBIS Over Clocking mechanism(2/4)

#### IBIS High Speed Mode(Over Clocking)

Copyright 2015

12

SOCIONEX

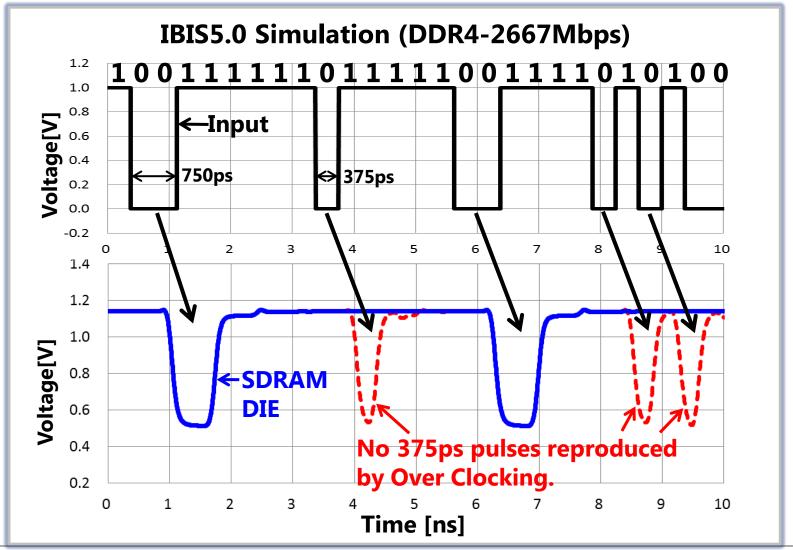

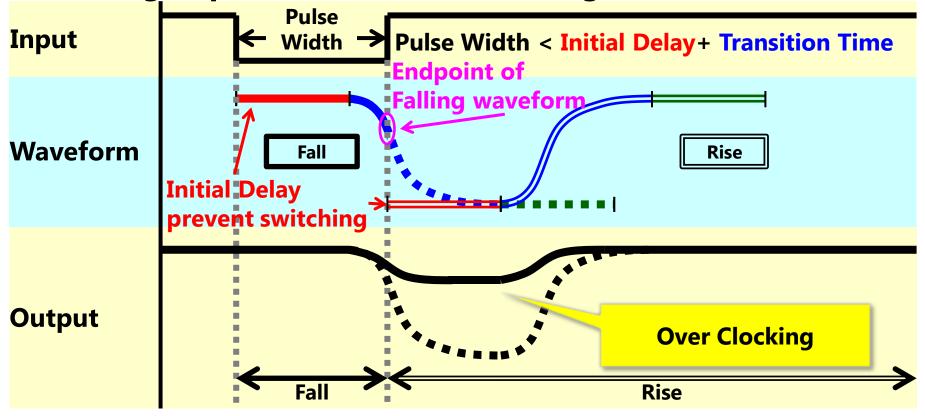

### IBIS Over Clocking mechanism(3/4)

#### ■ IBIS High Speed Mode(Initial Delay Cut)

Copyright 2015

SOCION

Copyright 2015

14

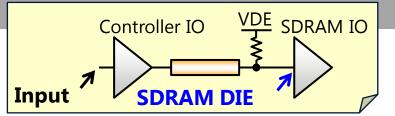

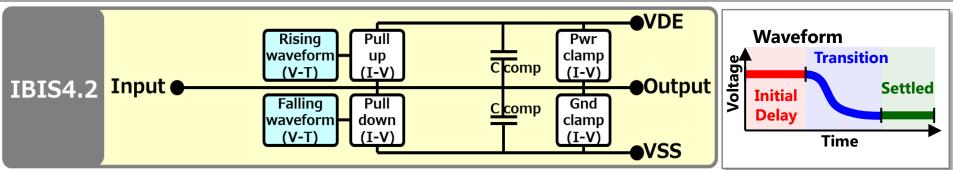

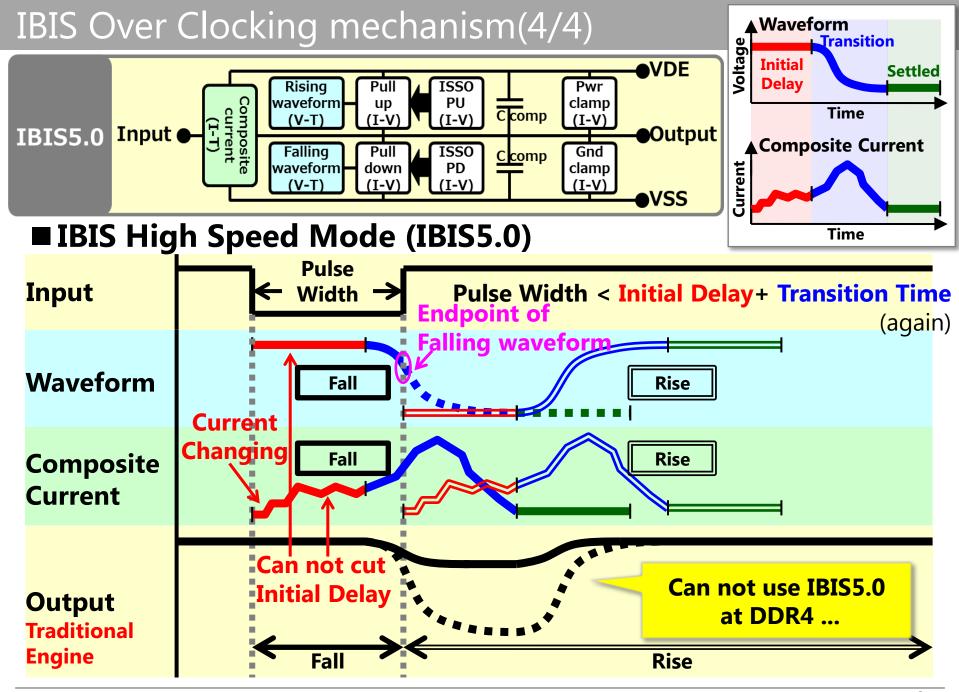

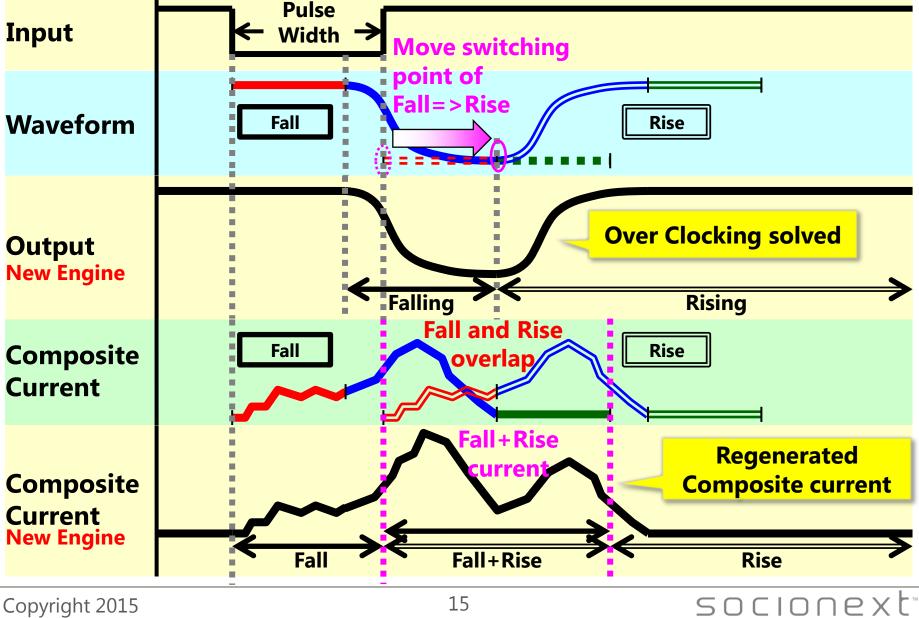

### Over Clocking modified in the EDA Software

#### ■ IBIS High Speed Mode (IBIS5.0)

Pulse Width = Transition Time

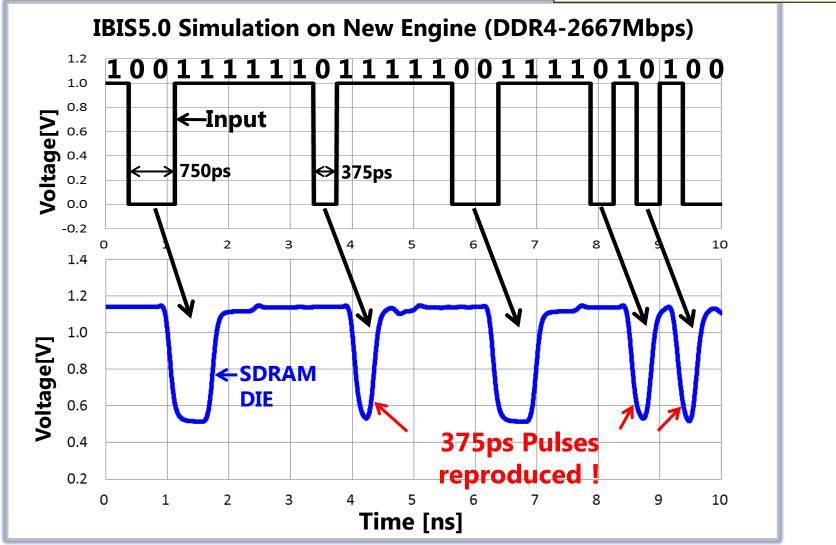

### New Engine Simulation Result (Over Clocking solved)

### Over Clocking issue of IBIS5.0 is solved!!

SOCIONEX

# DDR4 SI/PI Analysis Issue

# Over Clocking issue

# DDR4 SI/PI Analysis Using IBIS5.0

### Summary

### Expectation for future IBIS

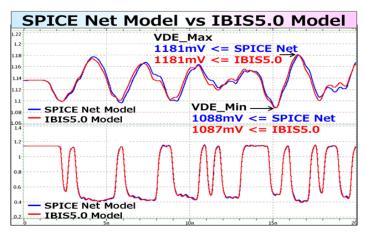

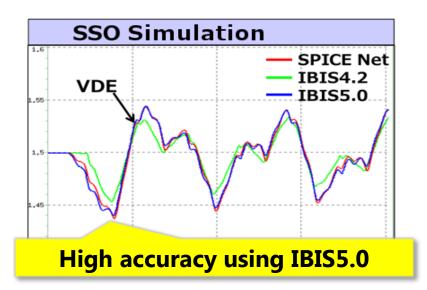

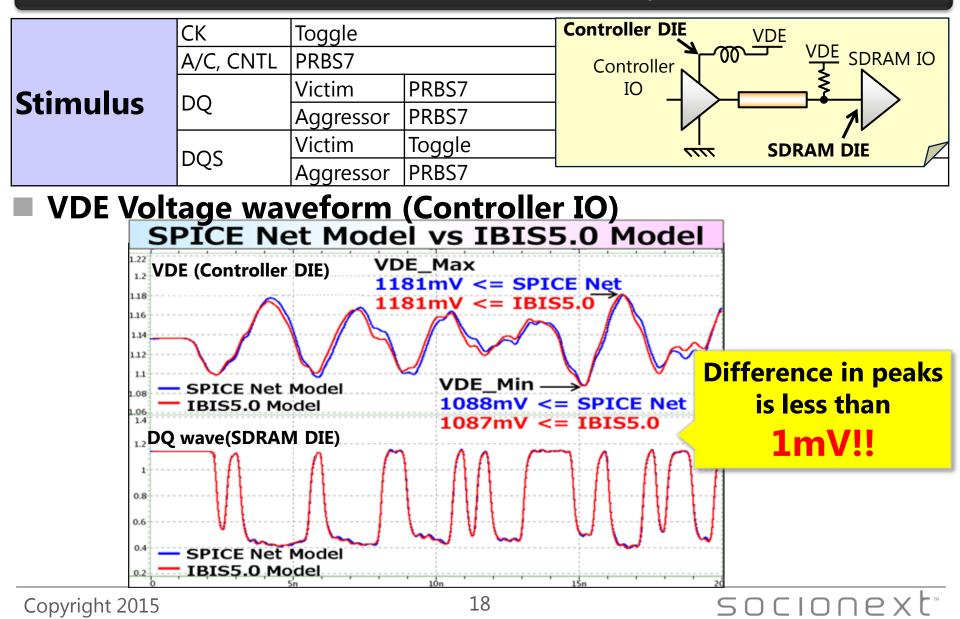

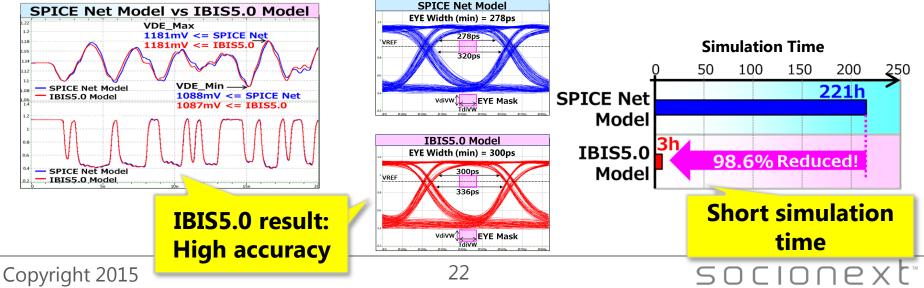

### DDR4 SI/PI Analysis Using IBIS5.0(1/3)

#### Waveform of the SSO noise : Very Good !!

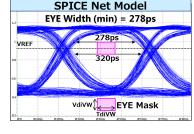

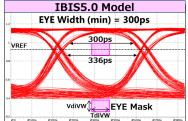

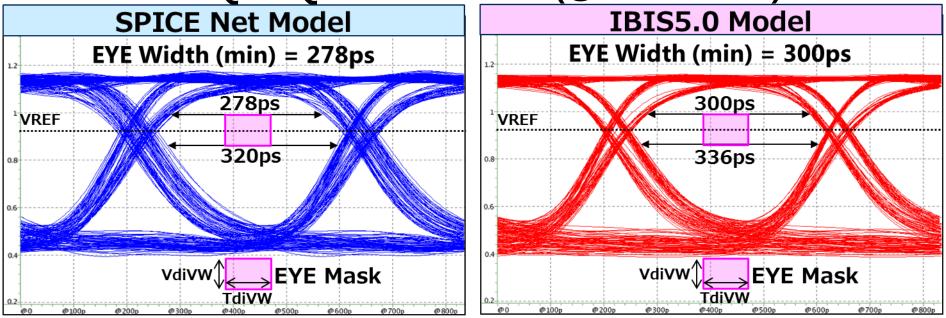

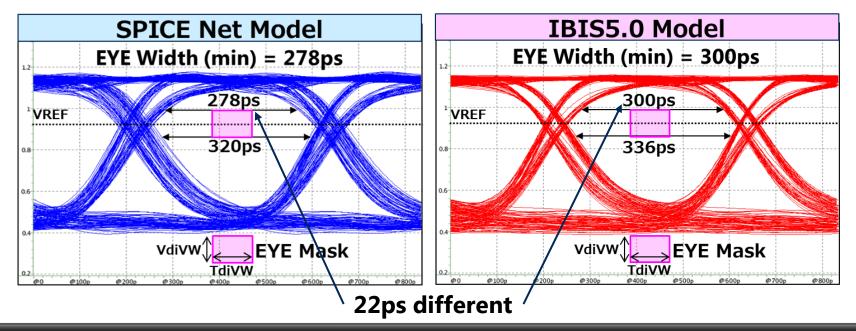

### DDR4 SI/PI Analysis Using IBIS5.0(2/3)

# Width of the EYE : Seems Good (see "Expectation for future IBIS")

| Stimulus | СК        | Toggle        |                           |

|----------|-----------|---------------|---------------------------|

|          | A/C, CNTL | PRBS7         |                           |

|          |           | Victim        | PRBS7                     |

|          | DQ        | Aggressor     | PRBS7 (Even/Odd 2pattern) |

|          | DOS       | Victim        | Toggle                    |

|          | DQS       | DQS Aggressor | Toggle                    |

#### DDR4 TX DQS-DQ EYE Waveform (@SDRAM DIE)

Copyright 2015

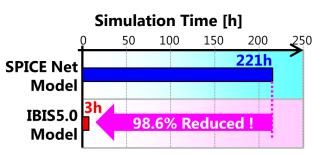

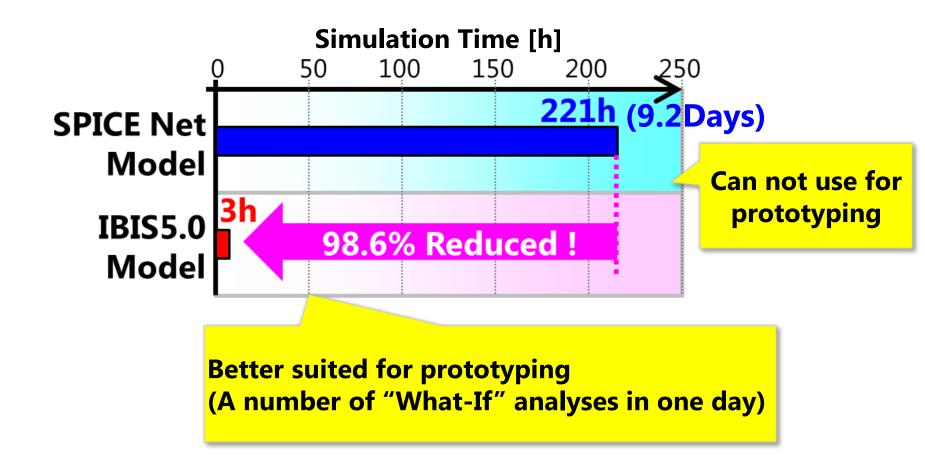

### DDR4 SI/PI Analysis Using IBIS5.0(3/3)

Simulation Time : Excellent !!!

• Transition Analysis Time:60ns(one cycle of PRBS7)

socione

# DDR4 SI/PI Analysis Issue

# Over Clocking issue

# DDR4 SI/PI Analysis Using IBIS5.0

# Summary

# Expectation for future IBIS

#### Summary

- Because of the Over Clocking issue, we could not use IBIS5.0 for high speed analysis, such as for DDR4.

- Modification of the EDA software has removed the Over Clocking issue.

- Therefore, the accuracy of IBIS5.0 at high speed has improved.

### IBIS5.0 can analyze DDR4 SI/PI with high accuracy in a short time!

# DDR4 SI/PI Analysis Issue

# Over Clocking issue

# DDR4 SI/PI Analysis Using IBIS5.0

### Summary

# Expectation for future IBIS

### **Remaining issue on IBIS5.0**

IBIS5.0 does not show IO Delay Penalty accurately

✓ IBIS5.0 modeling only final-buffer, pre-buffer Delay Penalty can not be considered.

For further simulation accuracy and capability, support of the pre-buffer delay penalty is strongly desired.

SOCIONE

# SOCIONEXt<sup>m</sup> for better quality of experience