#### Enabling Full Power-aware Bus Simulation with Non-IBIS Device Model - A Kit using IBIS [External Model]

Skipper Liang Cadence Design Systems Asian IBIS Summit, Taipei, Taiwan November 13, 2015

cādence<sup>®</sup>

Introduction

Approach 1: Using IBIS [External Model]

Approach 2: Using an IBIS model to drive the SPICE netlist

Solution: A dummy IBIS model using [External Model] and additional circuit

Summary

2 © 2015 Cadence Design Systems, Inc. All rights reserved.

# Introduction

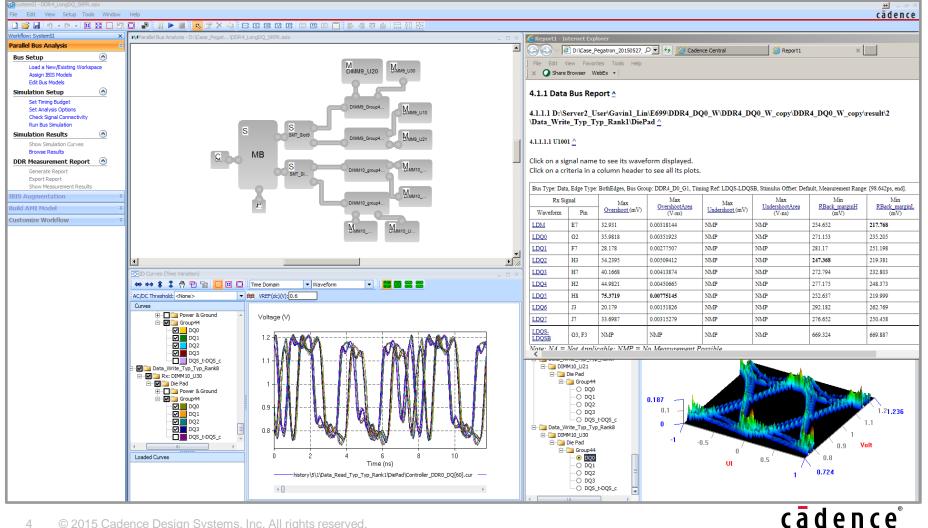

#### **Bus simulation**

#### It refers to an automatic process

- which includes simulation, measurement and report generation against a Bus, especially the memory interface in an EDA tool

#### **IBIS** model

- Intrinsic format the description of [Pin], [Diff Pin] and [Model Selector]

- IBIS makes Bus simulation possible in an EDA tool

- easy to assign data groups with individual timing reference

- Easy to change models and settings in batch mode

| oup/Signal                                                                                                                  | Stimulus Pattern | Stimulus Offset (ns) | Transmit IO Model | Receive IO Model | Status        |                                   |

|-----------------------------------------------------------------------------------------------------------------------------|------------------|----------------------|-------------------|------------------|---------------|-----------------------------------|

| Group44-low                                                                                                                 | 1000110101110001 | Default              |                   |                  |               |                                   |

| DDR0_DQ<56>                                                                                                                 | 1000110101110001 | 0.5T                 | pod12_34_60odt    | pod12_34_60odt   | Signal        |                                   |

| DDR0_DQ<57>                                                                                                                 | 1000110101110001 | 0.5T                 | pod12_34_60odt    | pod12_34_60odt   | Signal        |                                   |

| DDR0_DQ<58>                                                                                                                 | 1000110101110001 | 0.5T                 | pod12_34_60odt    | pod12_34_60odt   | Signal        |                                   |

| DDR0_DQ<57>           DDR0_DQ<58>           DDR0_DQ<58>           DDR0_DQ<59>           DDR0_DQS_7_P           DDR0_DQS_7_N | 1000110101110001 | 0.5T                 | pod12_34_60odt    | pod12_34_60odt   | Signal        |                                   |

| DDR0_DQS_7_P                                                                                                                | 10               | 0.75T                | pod12_34_60odt    | pod12_34_60odt   | Timing Ref    | Voltage (V)                       |

| DDR0_DQS_7_N                                                                                                                | 01               | 0.75T                | pod12_34_60odt    | pod12_34_60odt   | Timing Ref    | voliage (v)                       |

| DDR0_CK_0_P                                                                                                                 |                  |                      | pod12_34_cmd      |                  | Not Connected | ReadSkew: 69,7933 (ps)            |

| DDR0_CK_0_N                                                                                                                 |                  |                      | pod12_34_cmd      |                  | Not Connected |                                   |

| Group44-Upper                                                                                                               | 1000110101110001 | Default              |                   |                  |               | 1 VIH(ec) min = 0.868 (V) +       |

| DDR0_DQ<60>                                                                                                                 | 1000110101110001 | 0.5T                 | pod12_34_60odt    | pod12_34_60odt   | Signal        | VRÈF(dc) = 0.768 (V) <sup>2</sup> |

| DDR0_DQ<60><br>DDR0_DQ<61>                                                                                                  | 1000110101110001 | 0.5T                 | pod12_34_60odt    | pod12_34_60odt   | Signal        |                                   |

| DDR0 DO<62>                                                                                                                 | 1000110101110001 | 0.5T                 | pod12 34 60odt    | pod12 34 60odt   | Signal        | 0.5++                             |

| l Filter:                                                                                                                   |                  |                      |                   |                  |               | $VIHdiff(ac) min = 0.2 (M_a)$     |

|                                                                                                                             |                  |                      |                   |                  |               |                                   |

|                                                                                                                             |                  |                      |                   |                  |               |                                   |

|                                                                                                                             |                  |                      |                   |                  |               | ViLdiff(ac) max = -0.2 (V)/       |

|                                                                                                                             |                  |                      |                   |                  |               |                                   |

|                                                                                                                             |                  |                      |                   |                  |               | -0.5                              |

|                                                                                                                             |                  |                      |                   |                  |               |                                   |

|                                                                                                                             |                  |                      |                   |                  |               |                                   |

|                                                                                                                             |                  |                      |                   |                  |               |                                   |

#### SPICE netlist

- Maximum freedom in the circuit format but hard for Bus simulation to be implemented

- Has detailed characteristics of circuits which can't be fully described by IBIS model

- Some IC designers prefer using SPICE netlist model than IBIS model

|   | 36 ***********termination load and voltage ********                                                                              |

|---|----------------------------------------------------------------------------------------------------------------------------------|

|   | 7 'VRTT VTT GROUND '0.5 'vdd15'                                                                                                  |

|   | 98 'R1 VTT PAD 25                                                                                                                |

|   | ee *C1 PAD GROUND 4p                                                                                                             |

| 1 | 20 C2 C GROUND 0.1p                                                                                                              |

|   |                                                                                                                                  |

| 1 | 22 ***********************************                                                                                           |

|   |                                                                                                                                  |

| 1 | 24 VODTEN ODTEN GROUND 0 'high-active for termination impedance control enable, or termination=none                              |

|   | <sup>25</sup> VODT0 ODT0 GROUND vdd12 VODT[2:0] termination impedance bits control, ex:3'b000=none (detail table as bellow)      |

|   | V VODT I ODT I GROUND 0                                                                                                          |

|   | 27 VODT2 OFT2 GROUND 0                                                                                                           |

|   |                                                                                                                                  |

|   | 99 *******termination impedance table ****                                                                                       |

|   |                                                                                                                                  |

| 1 |                                                                                                                                  |

|   | 1 'mode=1'b0 (DDR2 mode)                                                                                                         |

|   | ** Indue - Do (DORZ Indue)<br>13 '3'DOOD = none                                                                                  |

|   | 4 '3b00'-Infe                                                                                                                    |

|   |                                                                                                                                  |

|   | 15 ^310010=750hm                                                                                                                 |

|   | 18 '3'b011=50ohm                                                                                                                 |

| 1 |                                                                                                                                  |

|   | 18 'mode=1'b1 (DDR3 mode)                                                                                                        |

|   | 19 '37b00-none                                                                                                                   |

|   | 2º '3'b001=120ohm                                                                                                                |

|   | 21 *3'b010=60ohm                                                                                                                 |

|   | 22 <sup>+</sup> 3'b011=40ohm                                                                                                     |

|   | 23 '3'b100=30ohm                                                                                                                 |

|   | 24 *3'b101=20ohm                                                                                                                 |

|   | 26                                                                                                                               |

|   |                                                                                                                                  |

|   | 27                                                                                                                               |

|   | 28                                                                                                                               |

|   | 29 ***funencrypted********                                                                                                       |

|   | 20 <sup>4</sup> .inc ins with the first and its of the insert of the antihering with the first and the insert of the insert      |

|   | 31                                                                                                                               |

|   | 32 ····e                                                                                                                         |

|   | 33 inc ing after lands an its in the ann inc i fan indiana, and lands after land an its indiana and an and an a                  |

|   | 34                                                                                                                               |

|   | 36                                                                                                                               |

|   | 36                                                                                                                               |

|   | 3 XDUT C CN1 CN2 CN3 CP1 CP2 CP3 DSEL DVDD DVSS I MODE ODT0 ODT1 ODT2 ODTEN OE PAD PD POC RXEN VDD VREF VSS SLP_BI_SDS_18V_D_PDO |

|   | 38                                                                                                                               |

|   | se                                                                                                                               |

|   |                                                                                                                                  |

|   | 24 · TEMP 60                                                                                                                     |

|   |                                                                                                                                  |

|   | 43 ^param fixed_cor_sw=1 _ vdd33='3.3 'vratio' vdd15='1.5 'vratio' vdd18='1.8 'vratio' vdd12='1.2 'vratio'<br>M known write-d    |

| 1 | 44 ^param vratio=1                                                                                                               |

| - |                                                                                                                                  |

caden

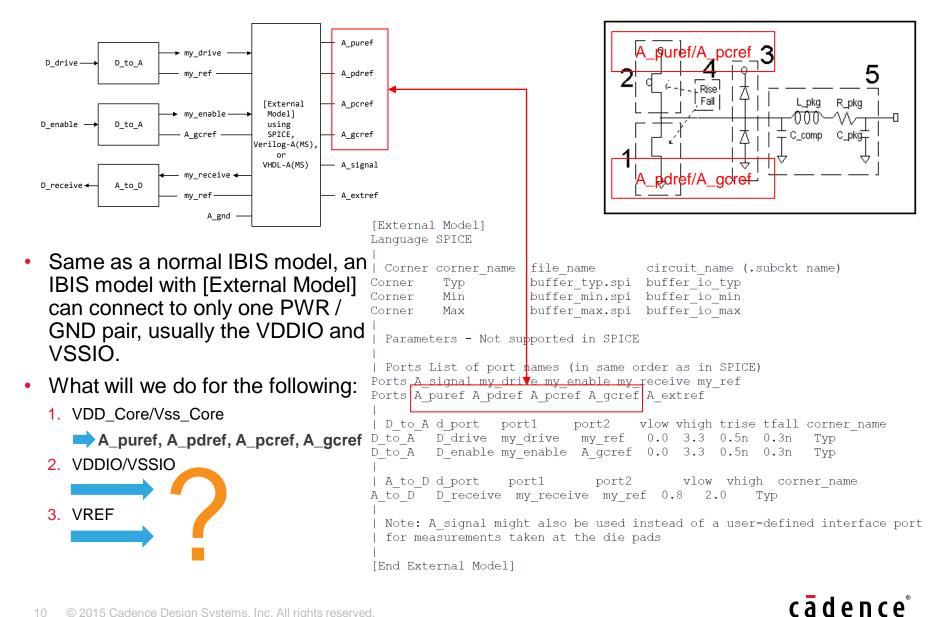

#### **IBIS External Model**

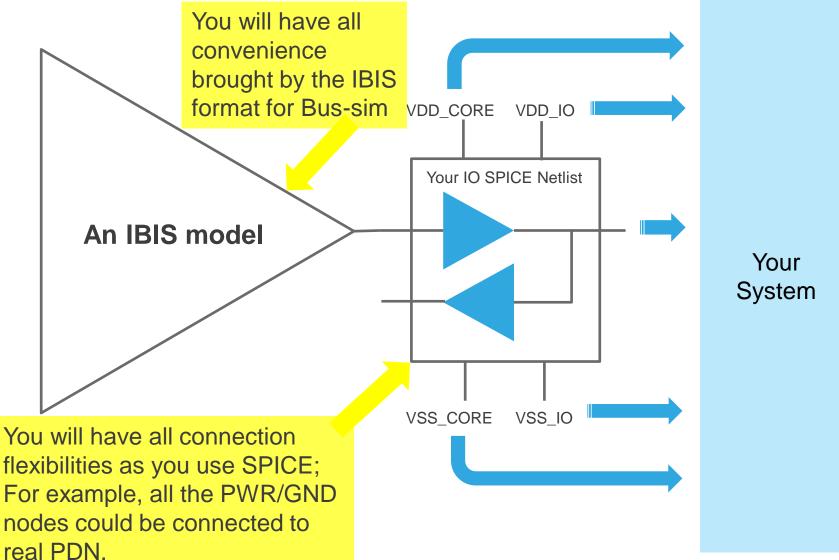

• Allow a spice netlist to be called by an IBIS model, which means:

- With IBIS format, easy for Bus-Sim to be implemented

- Include detailed characteristics of circuit

[External Model] Language SPICE | Corner corner name file name circuit name (.subckt name) buffer typ.spi buffer io typ Corner Тур Corner Min buffer min.spi buffer io min buffer max.spi buffer io max Corner Max | Parameters - Not supported in SPICE | Ports List of port names (in same order as in SPICE) Ports A signal my drive my enable my receive my ref Ports A puref A pdref A pcref A gcref A extref | D to A d port port1 port2 vlow vhigh trise tfall corner name D to A D drive my drive my ref 0.0 3.3 0.5n 0.3n Тур D to A D enable my enable A gcref 0.0 3.3 0.5n 0.3n Тур | A to D d port port1 port2 vlow vhigh corner name A to D D receive my receive my ref 0.8 2.0 Typ Note: A signal might also be used instead of a user-defined interface port for measurements taken at the die pads [End External Model]

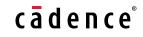

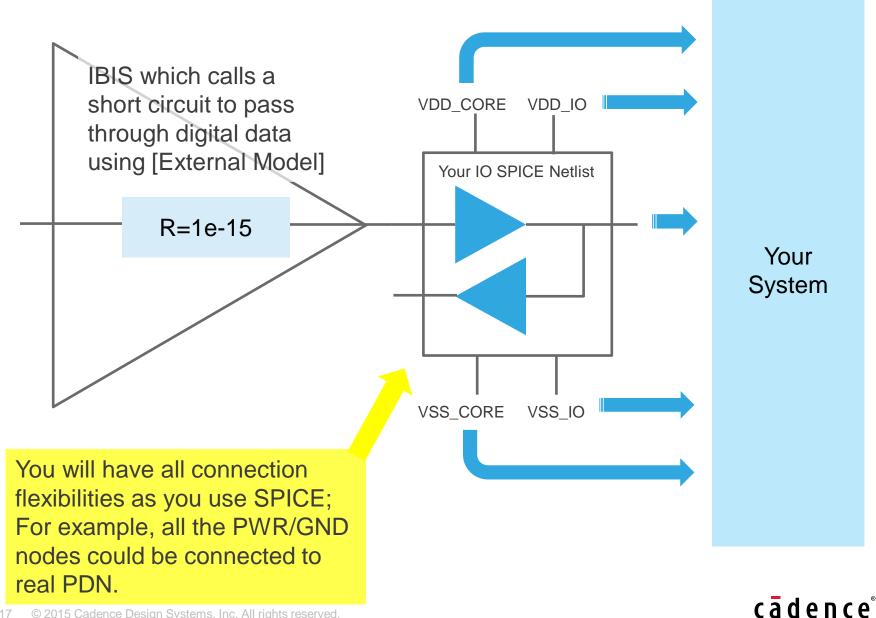

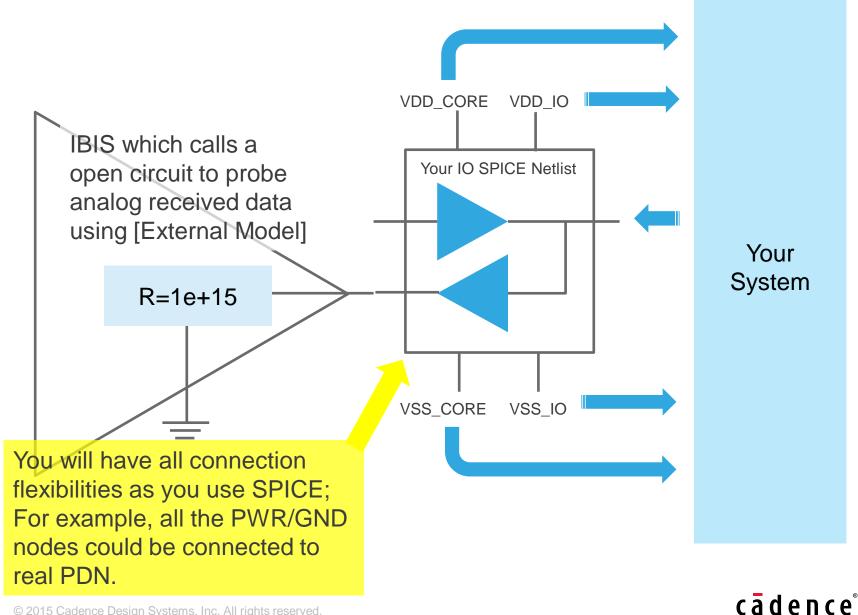

# SPICE netlist of transistor based device

- An example of SPICE netlist for a transistor based device model

- For power supply, there are:

- VDD\_Core/Vss\_Core

- VDDIO/VSSIO

- VREF

Question: if we can use IBIS [External Model] to call this netlist to execute a fully power-aware Bus-Simulation?

# Approach 1: using IBIS [External Model]

9 © 2015 Cadence Design Systems, Inc. All rights reserved.

#### Multi-power nets in [External Model] Section?

# Multi-power nets in [External Model] Section?

|                                                                                                                                                                                                                      | 1                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 .subckt se_drv15_odtoff DVDD DVSS PAD I OE nd_out_of_in                                                                                                                                                            | Model se_drv15_odtoff                                                                                                                                 |

| <sup>2</sup> .param vdd15='1.5'                                                                                                                                                                                      | *************************************                                                                                                                 |

| 4.param vdd12='1.2'<br>6 VREF VREF GROUND '0.5 'vdd15' 'reference voltage for the SSTL receiver @padring                                                                                                             | Model_type I/O<br>Polarity Non-Inverting                                                                                                              |

| 7 protect                                                                                                                                                                                                            | Enable Active-High<br>[Voltage Range] 1.500V 1.425V 1.575V                                                                                            |

| <sup>8</sup> .inc ./lib/design_io_pad.inc<br><sup>9</sup> .unprotect                                                                                                                                                 | [Ramp] -<br> variable typ min max                                                                                                                     |

| 10<br>11 *VDVDD DVDD GROUND vdd15 i power supply voltage                                                                                                                                                             | dV/dt_r 0.720/0.006n 0.720/0.006n 0.720/0.006n<br>dV/dt_f 0.720/0.006n 0.720/0.006n 0.720/0.006n                                                      |

| 12 VDVSS DVSS GROUND 0<br>13 VDDA12 VDD GROUND vdd12 · 'core power supply voltage                                                                                                                                    | R_load = 50.000                                                                                                                                       |

| 14/VSSA12 VSS GROUND 0<br>15                                                                                                                                                                                         | [External Model]<br>Language SPICE                                                                                                                    |

| 18 VMODE MODE GROUND vdd12 'mode select signal<br>17 '1'b0 selects DDR2 mode                                                                                                                                         | Corner corner_name file_name circuit_name (.subckt name)                                                                                              |

| 18 '1'b1 selects DDR3 mode<br>19 VPOC POC GROUND 0 'power on control @padring                                                                                                                                        | Corner Typ spice_io.ckt se_druf5_odtoff<br>Corner Min spice_io_min.ckt se_druf5_odtoff_min<br>Corner Max spice_io_max.ckt se_druf5_odtoff_max         |

| 20 21 .connect OE RXEN                                                                                                                                                                                               | Parts List of port names (in same order as in SPICE)                                                                                                  |

| 22<br>23                                                                                                                                                                                                             | Ports A_puref A_pdref A_signal my_drive my_enable my_receive                                                                                          |

| 24 VPD PD GROUND vdd12 'active-high for receiver power down signal 25                                                                                                                                                | j D_to_A d_port port1 port2 vlow vhigh trise tfall corner_name<br>D_to_A D_drive my_drive A_pdref 0.0 1.2 10p 10p Typ                                 |

| 26 VDSEL DSEL GROUND vdd12                                                                                                                                                                                           | D_to_A D_drive my_drive A_pdref 0.0 1.2 10p 10p Min<br>D_to_A D_drive my_drive A_pdref 0.0 1.2 10p 10p Max                                            |

| 28 *1'b1 full drive (classII)<br>29                                                                                                                                                                                  | D_to_A D_enable my_enable A_pdref 0.0 1.2 10p 10p Typ<br>D_to_A D_enable my_enable A_pdref 0.0 1.2 10p 10p Min                                        |

| 30 ************************************                                                                                                                                                                              | D_to_A D_enable my_enable A_pdref 0.0 1.2 10p 10p Max<br>  A_to_D_d_port_port1 port2 vlow vhigh corner_name                                           |

| 22 VODTEN ODTEN GROUND 0 'high-active for termination impedance control enable, or termination=none 33 VODT0 ODT0 GROUND vdd12 'ODT[2:0] termination impedance bits control, ex;3'b000=none (detail table as bellow) | A_to_D D_receive my_receive A_pdref 0.0 1.0 Typ<br>A_to_D D_receive my_receive A_pdref 0.0 1.0 Min<br>) A to D receive my receive A pdref 0.0 1.0 Max |

| 4 VODT1 ODT1 GROUND 0<br>35 VODT2 ODT2 GROUND 0                                                                                                                                                                      | <br> <br> End External Model]                                                                                                                         |

|                                                                                                                                                                                                                      | Fina currentar inacri                                                                                                                                 |

• Except the VDDIO and VSSIO, which will be connected to real power delivery network routing, the other PWR and GND will be connected to a "IDEAL" voltage source.

# Approach 2: Using an IBIS model to drive the SPICE netlist

#### cādence°

12 © 2015 Cadence Design Systems, Inc. All rights reserved.

#### **IBIS-drive** SPICE netlist

#### **IBIS-drive SPICE netlist (Cont')**

14 © 2015 Cadence Design Systems, Inc. All rights reserved.

#### cādence°

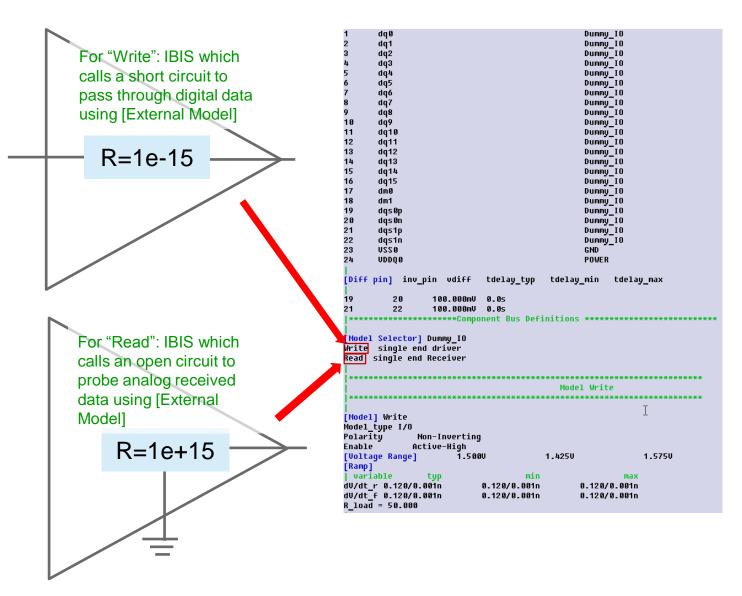

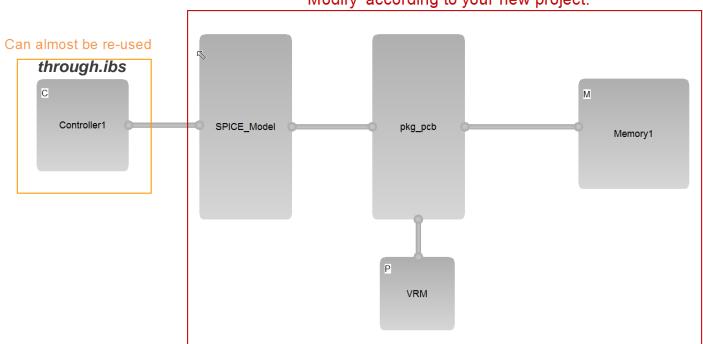

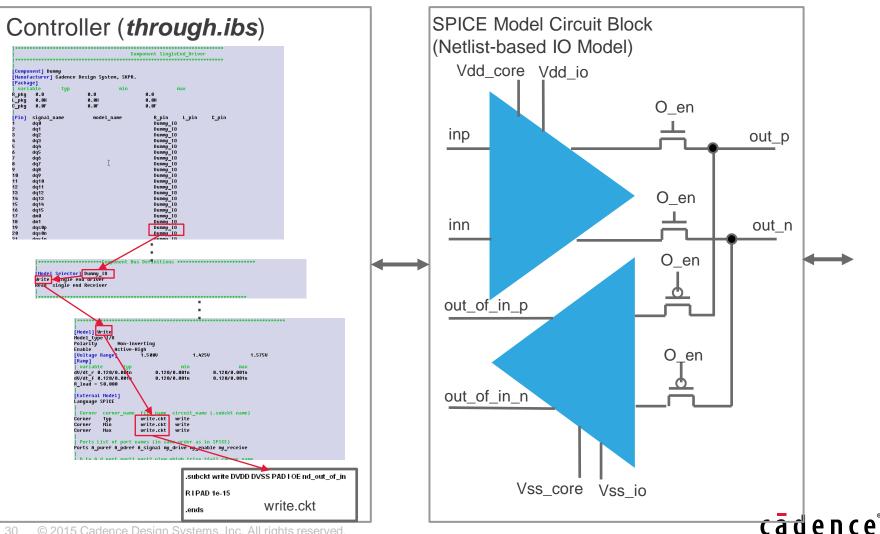

### Solution: A dummy IBIS model using [External Model] and additional circuits

#### A simple kit

#### Write Operation

© 2015 Cadence Design Systems, Inc. All rights reserved. 17

#### cādence<sup>®</sup>

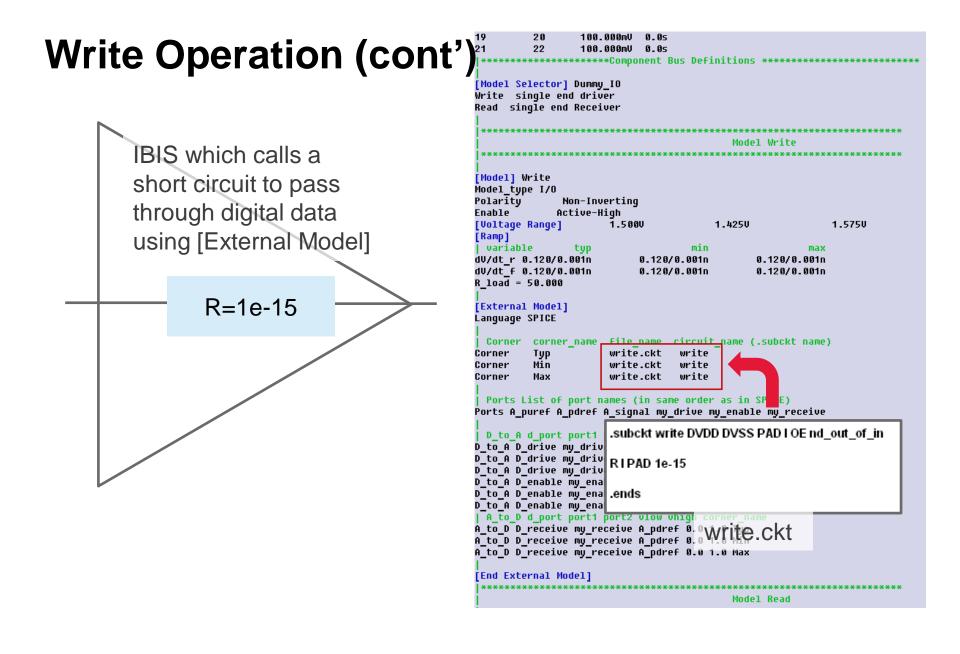

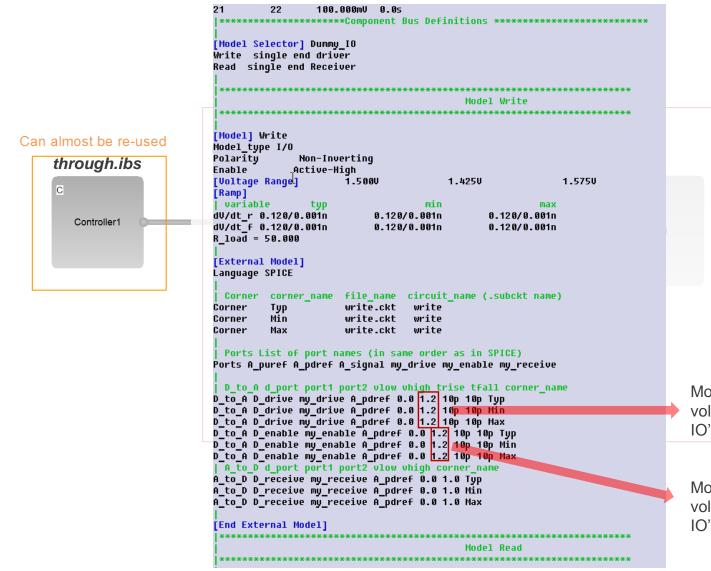

#### Write Operation (cont')

In a bus simulation, user can easily switch the model of the Controller's buffer to "Write"

| Controller    | Memory |                  |                      |                   |               |

|---------------|--------|------------------|----------------------|-------------------|---------------|

| Bus Group/Sig | gnal   | Stimulus Pattern | Stimulus Offset (ns) | Transmit IO Model | Status        |

| 🖃 🗹 🛛 DA      | TA0    | 1000110101110    | Default              |                   |               |

|               | dm0    |                  |                      | Write             | Not Connected |

|               | dq0    | 1000110101110    | 0.5T                 | Write             | Signal        |

|               | dq1    | 1000110101110    | 0.5T                 | Write             | Signal        |

|               | dq2    | 1000110101110    | 0.5T                 | Write             | Signal        |

|               | dq3    |                  |                      | Write             | Not Connected |

|               | dq4    |                  |                      | Write             | Not Connected |

|               | dq5    |                  |                      | Write             | Not Connected |

|               | dq6    |                  |                      | Write             | Not Connected |

|               | dq7    |                  |                      | Write             | Not Connected |

| ✓             | dqs0p  | 10               | 0.75T                | Write             | Timing Ref    |

|               | dqs0n  | 01               | 0.75T                | Write             | Timing Ref    |

| 🕀 📃 DA        | TA1    |                  |                      |                   |               |

#### Write Operation (cont')

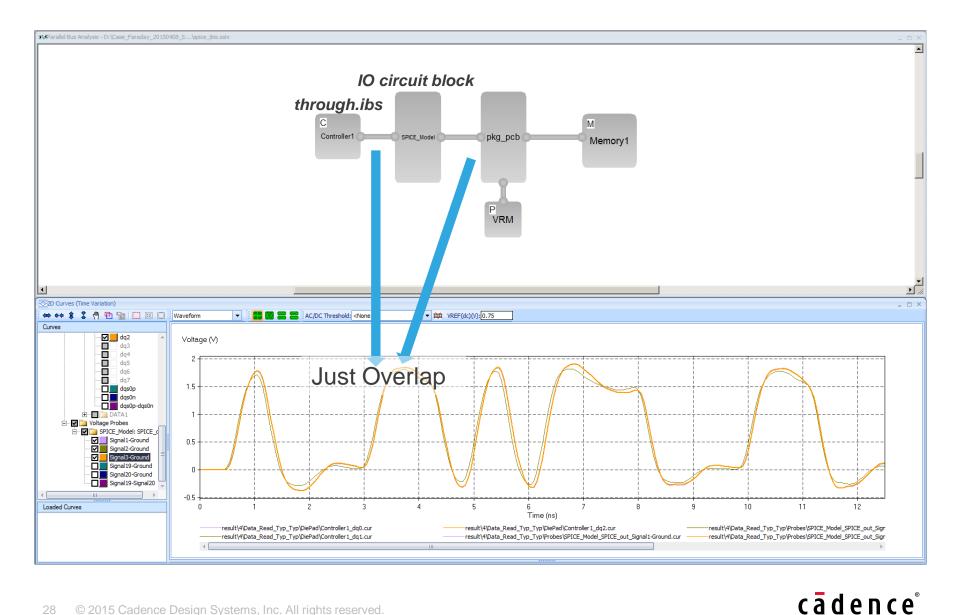

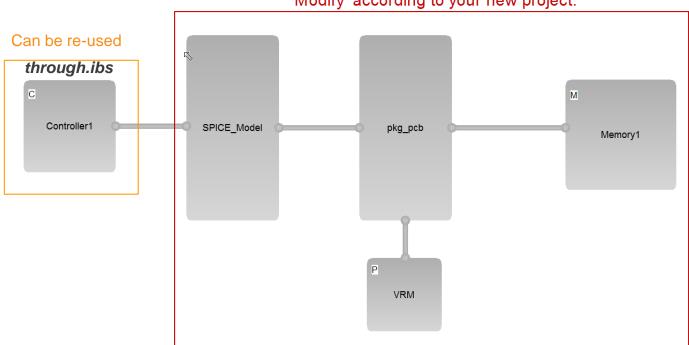

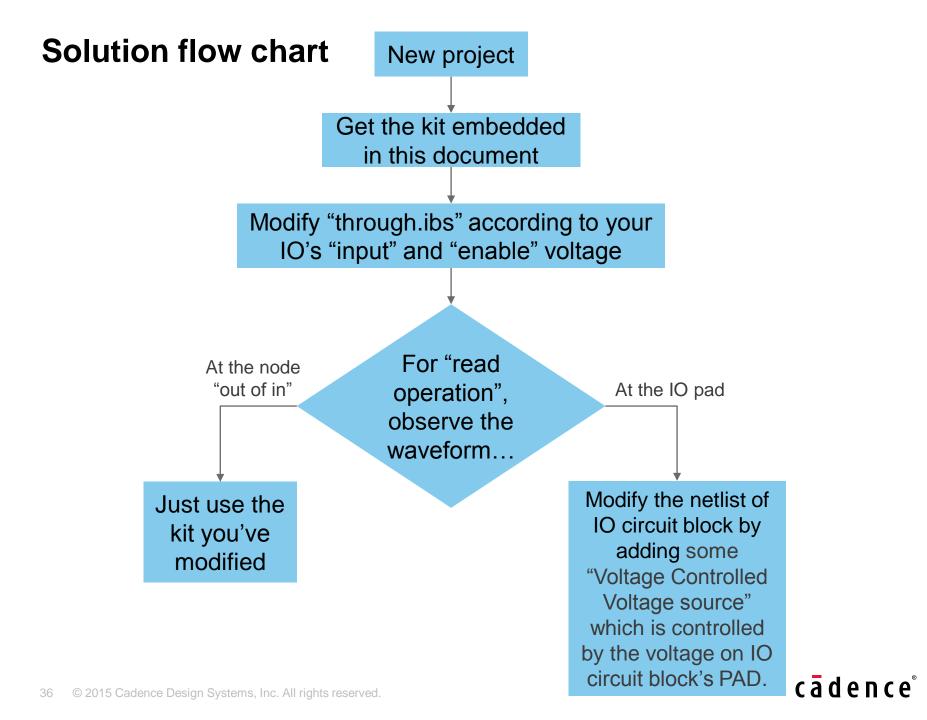

# Write Operation (cont') For a new project, the kit is re-usable with little modification

Modify according to your new project:

# Write Operation (cont') For a new project, the kit is re-usable with little modification

Modify to the correct voltage level of your IO's Input node

Modify to the correct voltage level of your IO's Enable node

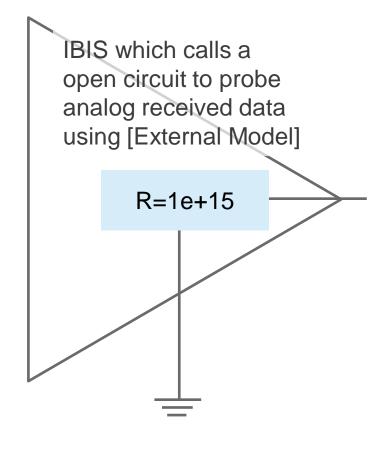

#### **Read Operation**

© 2015 Cadence Design Systems, Inc. All rights reserved. 23

| A_to_D D_receive my_r                                                | eceive A_pdref                                                      | F 0.0 1.0 Typ                  |            |  |  |  |  |

|----------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------|------------|--|--|--|--|

| A_to_D D_receive my_r                                                |                                                                     |                                |            |  |  |  |  |

| A_to_D D_receive my_r                                                | eceive A_pdre4                                                      | F 0.0 1.0 Max                  |            |  |  |  |  |

|                                                                      |                                                                     |                                |            |  |  |  |  |

| [End External Model]                                                 | [End External Model]                                                |                                |            |  |  |  |  |

| *************                                                        | ***********                                                         | ******                         | *****      |  |  |  |  |

|                                                                      |                                                                     | Model Re                       | ad         |  |  |  |  |

| ************                                                         | ***************************************                             |                                |            |  |  |  |  |

| 1                                                                    |                                                                     |                                |            |  |  |  |  |

| [Model] Read                                                         |                                                                     |                                |            |  |  |  |  |

| Model_type I/O                                                       |                                                                     |                                |            |  |  |  |  |

|                                                                      |                                                                     |                                |            |  |  |  |  |

| Enable Active-                                                       | High -                                                              |                                |            |  |  |  |  |

| [Voltage Range]                                                      | <b>1.500V</b>                                                       | 1.4250                         | 1.5750     |  |  |  |  |

| [Ramp]                                                               |                                                                     |                                |            |  |  |  |  |

| jvariable typ                                                        |                                                                     | min                            | max        |  |  |  |  |

| dV/dt_r 0.120/0.001n                                                 | 0.120/0                                                             | 9.001n 0.12                    | 0/0.001n   |  |  |  |  |

| dV/dt_f 0.120/0.001n                                                 | 0.120/0                                                             | 9.001n 0.12                    | 0/0.001n   |  |  |  |  |

| R_load = 50.000                                                      |                                                                     |                                |            |  |  |  |  |

| - F                                                                  |                                                                     |                                |            |  |  |  |  |

| [External Model]                                                     |                                                                     |                                |            |  |  |  |  |

| Language SPICE                                                       |                                                                     |                                |            |  |  |  |  |

| 1                                                                    |                                                                     |                                |            |  |  |  |  |

| Corner corner_name                                                   | file_name (                                                         | <del>sircui</del> t_name (.sub | ckt name)  |  |  |  |  |

| Corner Typ                                                           | read.ckt i                                                          | read                           |            |  |  |  |  |

| Corner Min                                                           | read.ckt i                                                          | read                           |            |  |  |  |  |

| Corner Max                                                           | read.ckt i                                                          | read                           |            |  |  |  |  |

|                                                                      |                                                                     |                                |            |  |  |  |  |

| Ports List of port                                                   |                                                                     |                                | E)         |  |  |  |  |

| Ports A_puref A_pdref                                                | A_signal my_o                                                       | frive my_enable                | _receive   |  |  |  |  |

|                                                                      |                                                                     |                                |            |  |  |  |  |

| D_to_A d_port port1                                                  |                                                                     | nigh trise tfall               | orner_name |  |  |  |  |

| D_to_A D_drive my_driv                                               | v                                                                   |                                |            |  |  |  |  |

| D_to_A D_drive my_driv                                               | D_to_A D_drive my_driv .subckt read DVDD DVSS PAD I OE nd_out_of_in |                                |            |  |  |  |  |

| D_to_A D_drive my_driv                                               |                                                                     |                                |            |  |  |  |  |

| D_to_A D_enable my_ena<br>D_to_A D_enable my_ena<br>R PAD DVSS 1e+15 |                                                                     |                                |            |  |  |  |  |

|                                                                      |                                                                     |                                |            |  |  |  |  |

| D_to_A D_enable my_en                                                |                                                                     |                                |            |  |  |  |  |

| A_to_D d_port port1                                                  |                                                                     |                                |            |  |  |  |  |

| A_to_D D_receive my_r                                                |                                                                     |                                |            |  |  |  |  |

| A_to_D D_receive my_r                                                | eceive A_pdre4                                                      | 5 0.0 1.0 Min                  |            |  |  |  |  |

| A_to_D D_receive my_r                                                | eceive A_pdre4                                                      | read.ck                        | (t         |  |  |  |  |

|                                                                      |                                                                     |                                |            |  |  |  |  |

| [End External Model]                                                 |                                                                     |                                |            |  |  |  |  |

| L                                                                    |                                                                     |                                |            |  |  |  |  |

| [End]                                                                |                                                                     |                                |            |  |  |  |  |

|                                                                      |                                                                     |                                |            |  |  |  |  |

|                                                                      | ******Modified by Cadence Design Systems*****                       |                                |            |  |  |  |  |

| [[ibischk5 V5.0.3]                                                   |                                                                     |                                |            |  |  |  |  |

#### cādence<sup>°</sup>

#### c<mark>a</mark>dence<sup>®</sup>

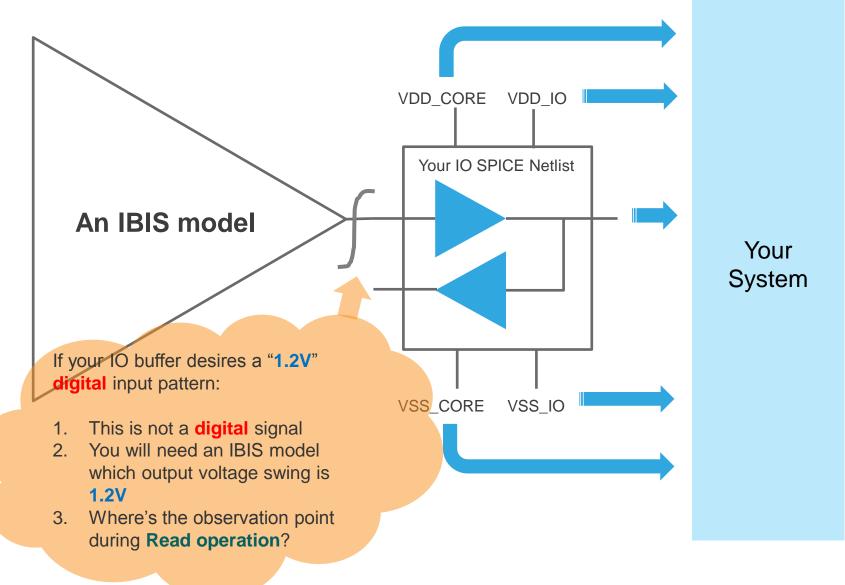

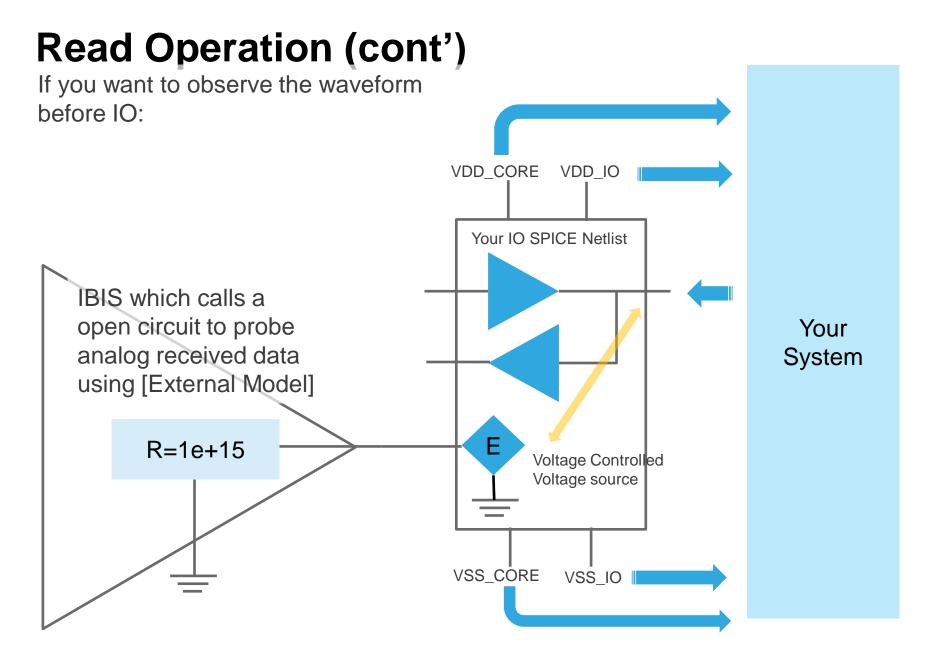

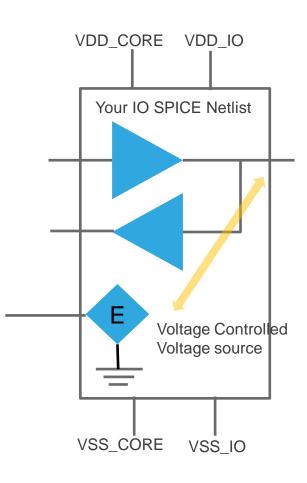

- You will need to modify the netlist of the IO circuit block by adding some "Voltage Controlled Voltage sources" which is controlled by the voltage on IO circuit block's PAD.

- Connect the dummy controller's output pad to these

"Voltage Controlled Voltage sources"

cādence<sup>®</sup>

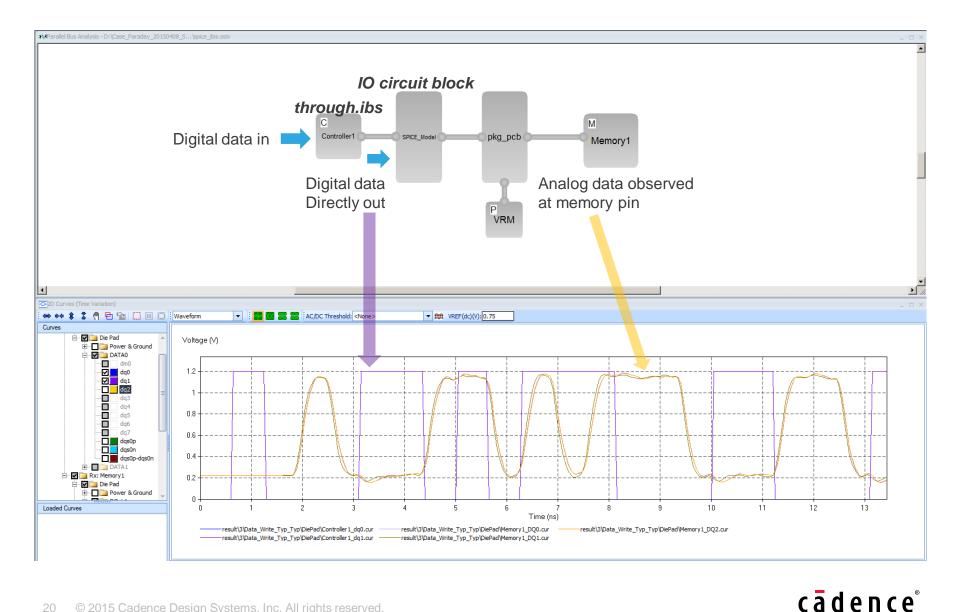

In a bus simulation, user can easily switch the model of the Controller's buffer to "Read"

| Controller Memory |                  |               |

|-------------------|------------------|---------------|

| Bus Group/Signal  | Receive IO Model | Status        |

| DATA0             |                  |               |

| dm0               | Read             | Not Connected |

| dq0               | Read             | Signal        |

| dq1               | Read             | Signal        |

| dq2               | Read             | Signal        |

| dq3               | Read             | Not Connected |

| dq4               | Read             | Not Connected |

| dq5               | Read             | Not Connected |

| dq6               | Read             | Not Connected |

| dq7               | Read             | Not Connected |

| dqs0p             | Read             | Timing Ref    |

| dqs0n             | Read             | Timing Ref    |

| DATA1             |                  |               |

#### cādence°

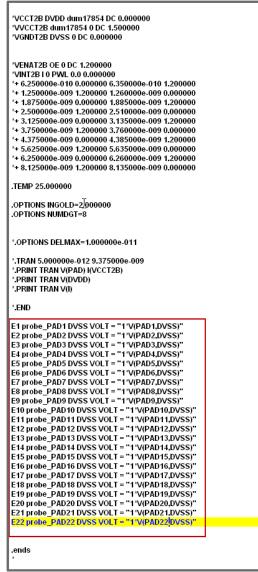

# Read Operation (cont') For a new project, the kit is re-usable with little modification

Modify according to your new project:

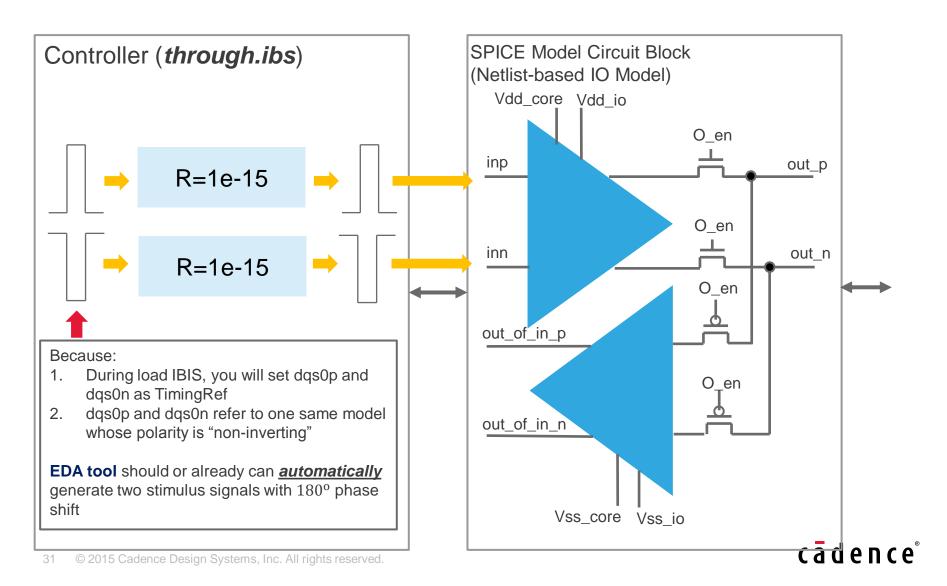

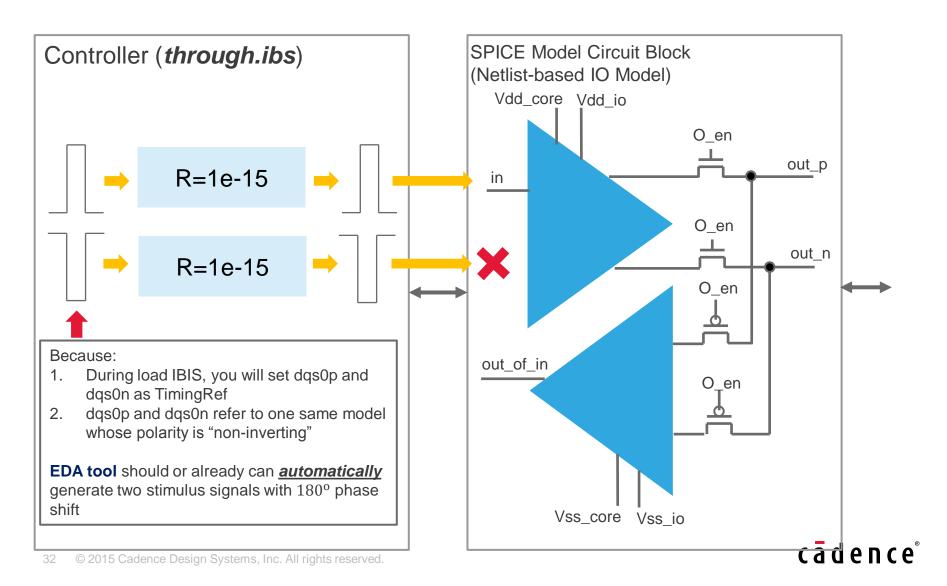

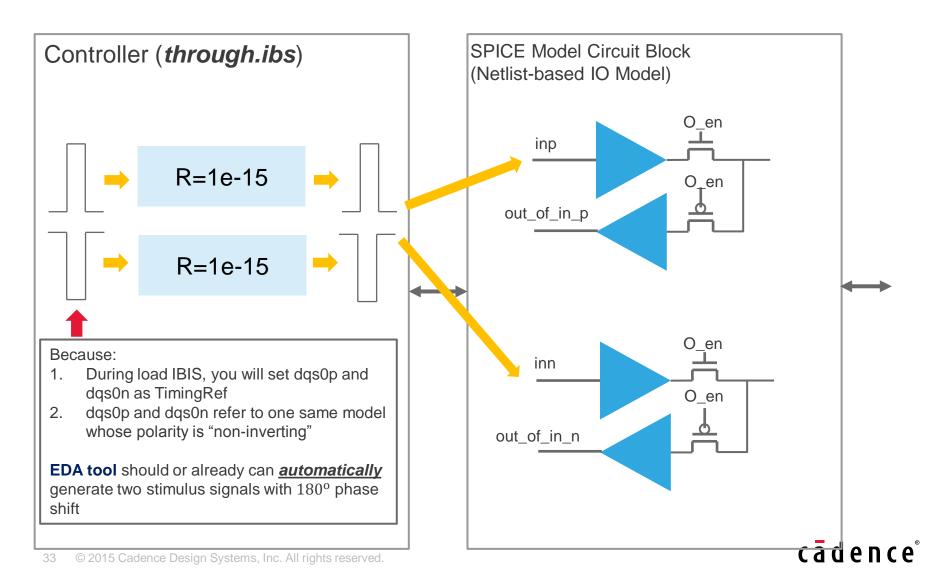

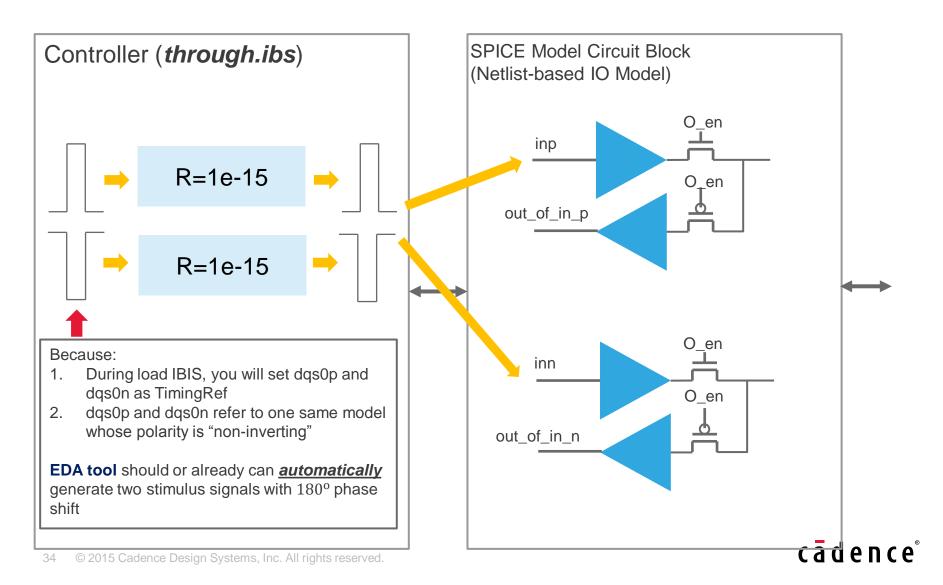

### **Differential Buffer**

No matter true or pseudo, you can use the same kit without any modification because:

(take "write operation" as an example)

© 2015 Cadence Design Systems, Inc. All rights reserved.

For Truly Differential Buffer type1:

For Truly Differential Buffer type2:

For Pseudo Differential Buffer:

For Pseudo Differential Buffer:

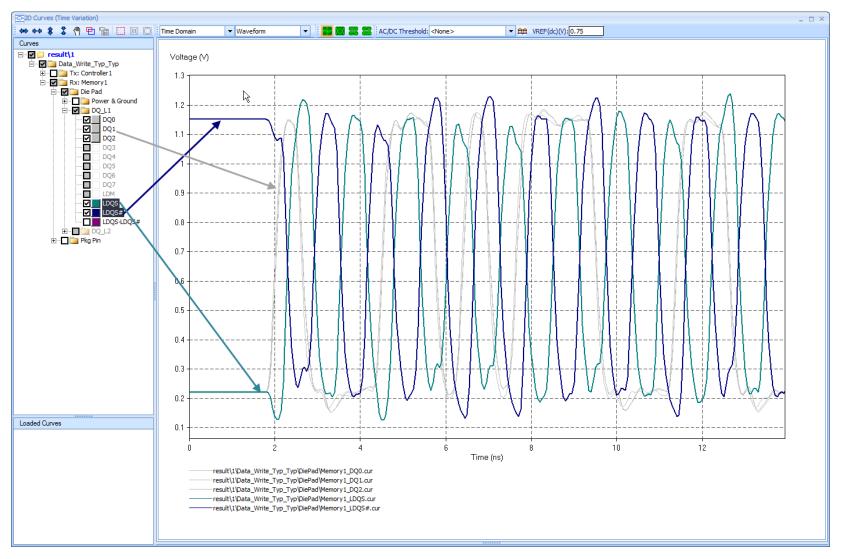

An example with method2: 3 DQ and 1 pair of DQS

#### cādence<sup>®</sup>

# Summary

37 © 2015 Cadence Design Systems, Inc. All rights reserved.

#### Notes

#### For analysis of SSN

- With the full flexibilities as using SPICE, this method allows user to do a poweraware SSN analysis between multiple signals and multiple PDNs, such as VDD\_Core/VSS\_Core, VDDIO/VSSIO, VTT and VREF together at the same time.

- Model modification and change of topology

- This method requires the change of topology inserting a Spice block but the wrapping .sp file according to the description in [External Model] is not necessary since it's ready for use in the kit - easy for re-using this kit in a new project of a new IO.

#### Read Operation

- As this method requires the change of topology when building topology, during the analysis of read operation, user will need to modify the netlist of the IO circuit block by adding some "Voltage Controlled Voltage source" which is controlled by the voltage on IO circuit block's PAD.

- Differential Buffer

- This method can use the same kit without additional modification for both singleend and differential buffer, no matter it's truly or pseudo.

#### References

IBIS specification (v6.1)

<u>http://www.ibis.org/ver6.1/ver6\_1.pdf</u>

# cādence®