## WELCOME FROM MIKE LABONTE, SIGNAL INTEGRITY SOFTWARE

Ladies and Gentlemen,

As chair of the IBIS Open Forum it is my pleasure to welcome you to the 2015 Asian IBIS Summit in Shanghai, and to thank you for your presentations and participation. We are grateful to our sponsors Huawei Technologies, Cadence Design Systems, IO Methodology, Keysight Technologies, Synopsys, Teledyne LeCroy, and ZTE Corporation for making this event possible.

Since 1993 IBIS has provided the digital electronics industry with specifications to make signal, timing, and power integrity analyses much easier and faster. The challenges keep changing and the IBIS community keeps responding with new enhancements to the IBIS family of specifications, which the IC vendors, EDA tool companies, and system designers adopt readily.

Support for IBIS in Asia has been strong, and the IBIS Open Forum looks forward to continued innovation and contributions from technology companies in this part of the world. Thank you!

Mike LaBonte

Signal Integrity Software (SiSoft)

Chair, IBIS Open Forum

Medral R Lasants

### WELCOME FROM MIKE LABONTE, SIGNAL INTEGRITY SOFTWARE

女士们,先生们,

作为 IBIS 开放论坛的主席我很高兴地欢迎大家来到 2015 年亚洲 IBIS 上海峰会,并感谢您的演讲和参与。我们特别要感谢我们的赞助商华为技术,Cadence Design Systems,IO Methodology Inc, Keysight Technologies,Synopsys,Teledyne LeCroy 和 ZTE 中兴通讯,是他们使本次活动成为可能。

从 1993 年至今,IBIS 为高速数字电路设计的信号,时序和功率完整性分析方面提供了更加容易和快捷电子模型行业规范。为适应不断变化的挑战,在 IC 供应商, EDA 工具公司和系统设计师的共同努力下, IBIS 正在继续不断加入新的功能和完善已有的 IBIS 系列规范。

在亚洲,IBIS 一直受到广泛的支持。 从世界的这一部分, IBIS 开放论坛期待着有更多的技术创新和贡献。

谢谢!

Mike LaBonte (迈克 拉邦地)

Mahal R Land

SiSoft 公司

主席, IBIS 开放论坛

## WELCOME FROM LI JINJUN, HUAWEI TECHNOLOGIES

Ladies and Gentlemen,

On behalf of Huawei Technologies, welcome to the 11th annual Asian IBIS Summit (China). I would like to express my appreciation to IBIS Open Forum and all the sponsors for coorganizing this event.

Since 2005, IBIS Asian Summit in China has been the top-level international conference in high speed digital design society in China. I am looking forward to work with IBIS members in China, and to expand our participations in the region.

Huawei has actively involved in all IBIS society's events. We hope to resolve high speed link issues with IBIS Open Forum, EDA vendors and IC vendors. Your comments and suggestions will be deeply appreciated!

Welcome all of you to Shanghai! Hope you will enjoy all the technical discussions and sharing throughout the meeting, and have a nice journey!

Thank you! Jinjun Li Huawei Technologies

各位专家,各位来宾:

我代表华为公司,欢迎大家来参加第 11 届亚洲 IBIS 技术研讨会,衷心地感谢 IBIS 协会组织本次会议。

自从 2005 年以来, IBIS 技术研讨会已经成为了中国高速设计领域的一次盛会。我很高兴有机会与 IBIS 协会一起促进和扩大在该领域的分享。

华为积极参与各项 IBIS 活动,希望与 IBIS 协会、EDA 软件、芯片公司一道来共同解决许 多高速链路设计上的挑战,欢迎大家会上讨论和建议。

欢迎 IBIS 专家来到上海,希望你们能够喜欢所有的技术讨论和会议分享,度过美好一天。

谢谢大家 华为公司 厉进军

## AGENDA AND ORDER OF THE PRESENTATIONS

# (The actual agenda might be modified)

|       | IBIS SUMMIT MEETING AGENDA                                                                                                                                                                                                 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8:15  | SIGN IN - Vendor Tables Open at 8:30                                                                                                                                                                                       |

| 8:45  | <pre>WELCOME - Li, JinJun   (Huawei Technologies, China) - LaBonte, Mike (Chair, IBIS Open Forum   (Signal Integrity Software (SiSoft), USA)</pre>                                                                         |

| 9:00  | IBIS Chair's Report                                                                                                                                                                                                        |

| 9:25  | <pre>Introducing IBIS Version 6.1</pre>                                                                                                                                                                                    |

| 9:45  | Enabling Full Power-aware Bus Simulation with Non-IBIS Device 21 Model - A Kit Using IBIS [External Model] Liang, Skipper (Cadence Design Systems, China)                                                                  |

| 10:35 | BREAK (Refreshments and Vendor Tables)                                                                                                                                                                                     |

| 11:25 | A Practical DOE Application in Statistical SI Analysis Using 41 IBIS & How Can We Make IBIS Work Beyond Best Case/Worst Case? Shi*, Feng; Ekholm**, Anders; Mahmod**, Zilwan and Zhang*, David (Ericson, *China, **Sweden) |

| 11:20 | IBIS Interconnect BIRD Update                                                                                                                                                                                              |

| 12:00 | FREE BUFFET LUNCH (Hosted by Sponsors) - Vendor Tables                                                                                                                                                                     |

# AGENDA AND ORDER OF THE PRESENTATIONS (Continued)

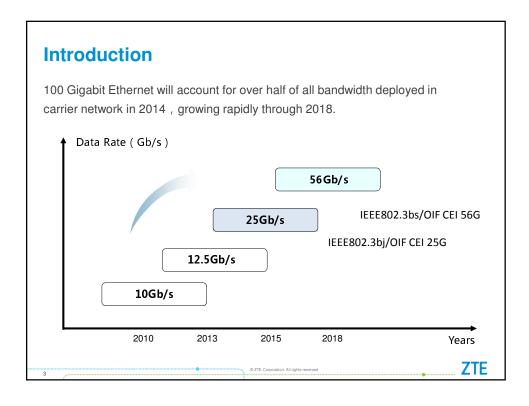

| 13:30 | FEC Applications for 25Gb/s Serial Link Systems                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 14:00 | PAM4 System Simulation Using AMI Models                                                                                                   |

| 14:30 | Some Results for General K-table Extraction Proposal Using SPICE 81 Ross*, Bob; Chen**, XueFeng (*Teraspeed Labs, USA, **Synopsys, China) |

| 15:00 | BREAK (Refreshments and Vendor Tables)                                                                                                    |

| 15:20 | <pre>IBIS Simulation Case Study: Unexpected Glitch and Using 92 C_fixture     Wang, Lance (IO Methodology, USA)</pre>                     |

| 15:55 | Laplace Transform Time Response Utility                                                                                                   |

| 16:30 | DISCUSSION                                                                                                                                |

| 17:20 | CONCLUDING ITEMS                                                                                                                          |

| 17:30 | END OF IBIS SUMMIT MEETING                                                                                                                |

# IBIS Chair's Report

http://ibis.org/

Mike LaBonte SiSoft Chair, IBIS Open Forum

Asian IBIS Summit Shanghai, China November 9, 2015

9 November 2015

IBIS Chair's Report

Specification Development

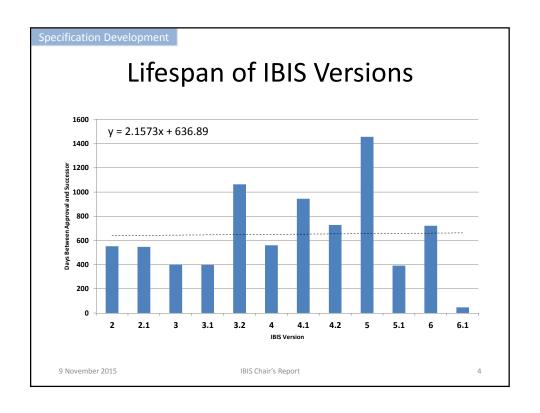

# **IBIS Milestones**

#### I/O Buffer Information Specification

- 1993-1994 IBIS 1.0-2.1:

- Behavioral buffer model (fast simulation)

- Component pin map (easy EDA import)

- 1997-1999 IBIS 3.0-3.2:

- Package models

- Electrical Board Description (EBD)

- Dynamic buffers

- 2002-2006 IBIS 4.0-4.2:

- Receiver models

- AMS languages

- 2007-2012 **IBIS 5.0-5.1**:

- IBIS-AMI SerDes models

- Power aware

- 2013-2015 IBIS 6.0-6.1:

- PAM4 multi-level signaling

- Power delivery package models

#### Other Work

- 1995: ANSI/EIA-656

- IBIS 2.1

- 1999: ANSI/EIA-656-A

- IBIS 3.2

- 2001: IEC 62014-1

- IBIS 3.2

- 2003: ICM 1.0

- Interconnect Model Specification

- 2006: ANSI/EIA-656-B

- IBIS 4.2

- 2009: Touchstone® 2.0\*

- 2011: IBIS-ISS 1.0

- Interconnect SPICE Subcircuit specification

\*Touchstone® is a registered trademark of Agilent Technologies, Inc.

9 November 2015

IBIS Chair's Report

# Progress: IBIS 6.1 Ratified • Ratified 11 September 2015 • Support for PAM4 • IBIS-AMI Parameters Simplified • Package Models for Power Integrity • and more ...

Specification Development

# In The Works

- IBIS 6.2 dedicated to reference node clarifications

- Potential SAE standard

- Advance Technology Modeling Task Group

- Optimization/Back-channel support

- External circuit enhancements

- Interconnect Task Group

- External Package/on-die models using IBIS-ISS

- IBIS Quality Task Group

- IBISCHK enhancements and documentation

9 November 2015

IBIS Chair's Report

5

#### **Specification Development**

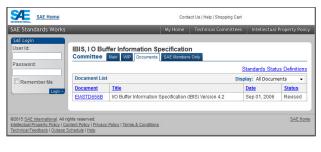

# Status of IBIS Standards

## IBIS 6.2 might be next ...

9 November 2015

IBIS Chair's Report

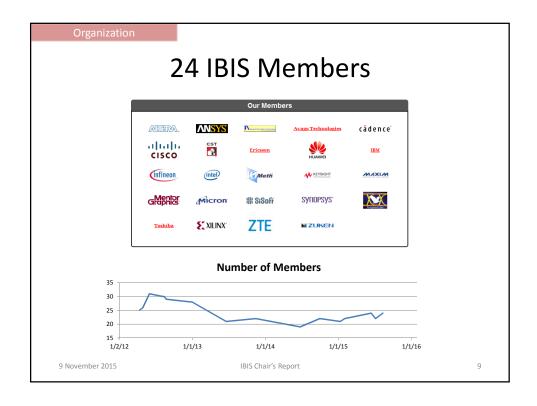

## **IBIS Officers 2015-2016** New Chair, Treasurer and Postmaster elected 15 June 2015 Many thanks to incumbent IBIS officers for their continued service A special thank you to outgoing chair Michael Mirmak (Total of 11 terms!) Chair: Mike LaBonte, Signal Integrity Software Lance Wang, IO Methodology Inc. Vice-Chair: Secretary: Randy Wolff, Micron Technology Treasurer: Bob Ross, Teraspeed Labs Librarian: Anders Ekholm, Ericsson Webmaster: Mike LaBonte, Signal Integrity Software Postmaster: Curtis Clark, ANSYS 9 November 2015 IBIS Chair's Report 10

#### Organization

# **Organizational Activities**

- So far in 2015:

- 15 Open Forum teleconferences

- 3 Summit meetings (including this one)

- 2015 first year for EPEPS IBIS summit

- 38 ATM Task Group teleconferences

- 10 Editorial Task Group teleconferences

- 10 Interconnect Task Group teleconferences

- 35 Quality Task Group teleconferences

9 November 2015 IBIS Chair's Report

#### Organization

# **Upcoming Summits**

- Asian IBIS Summit, Taipei, Taiwan

- November 13, 2015

- Asian IBIS Summit, Tokyo, Japan

- November 16, 2015

- DesignCon IBIS Summit, Santa Clara, CA

- January 22, 2016

- SPI IBIS Summit, Torino, Italy

- May 11, 2016

9 November 2015

IBIS Chair's Report

11

Infrastructure

# We Have Moved!

- Our gratitude to Accellera for eda.org web and email service from 1993 to 2015

- · Email lists have moved to freelists.org

- Website has moved to <a href="http://ibis.org">http://ibis.org</a>

9 November 2015 IBIS Chair's Report

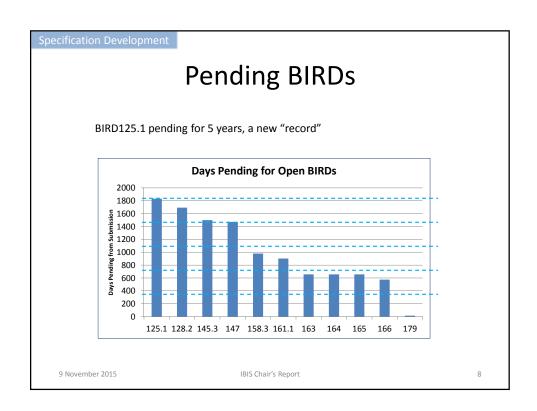

#### Open BIRDs Make IBIS-ISS Available for IBIS Package Arpad Muranyi, Mentor Graphics 21-Oct-10 Modeling Allow AMI\_parameters\_out to pass 128.2 AMI parameters in data on calls to Walter Katz, SiSoft 11-Mar-11 AMI GetWave Cascading IBIS I/O buffers with [External Circuit]s Taranjit Kukal, Ambrish Varma, Cadence Design using the [Model Call] keyword Systems, Inc. Arpad Muranyi, Mentor Graphics. 145.3 19-Sep-11 Marcus Van Ierssel, Snowbush IP; Kumar Keshavan, Sigrity, Inc.; Ken Willis, Sigrity, Inc.; 147 Back-channel support 18-Oct-11 158.3 AMI Touchstonefile (R) Analog Buffer Models Walter Katz, Signal Integriity Software, Inc. 20-Feb-13 Supporting Incomplete and Buffer-only Michael Mirmak, Intel Corp. 8-May-13 [Component] Descriptions Arpad Muranyi & John Angulo, Mentor Graphics; Instantiating and Connecting [External Circuit] Ambrish Varma & Brad Brim, Cadence Design 9-Jan-14 Package Models with [Circuit Call] Systems, Inc. Allowing Package Models to be defined in Ambrish Varma & Brad Brim, Cadence Design 164 9-Jan-14 [External Circuit] Systems, Inc.; Arpad Muranyi, Mentor Graphics Arpad Muranyi & John Angulo, Mentor Graphics;

9 November 2015 IBIS Chair's Report

Ambrish Varma & Brad Brim, Cadence Design

Walter Katz, Signal Integrity Software, Inc.

Darshan Shah, F5Networks, Inc.

Arpad Muranyi, Mentor Graphics

9-Jan-14

2-Apr-14

13-Oct-15

17

Parameter Passing Improvements for [External

Resolving problems with Redriver Init Flow

New IBIS-AMI Reserved Parameter

Special Param Names

165

# **Introducing IBIS Version 6.1**

Michael Mirmak Intel Corporation

http://www.ibis.org/

ASIAN IBIS Summit Shanghai, China November 9, 2015

# **Agenda**

IBIS 6.1 Overview and Development

Key Features

AMI Improvements

Traditional IBIS Improvements

Methods for Providing Feedback

References

\* Other names and brands may be claimed as the property of others

# **Specifications and Activities**

- IBIS Version 6.1 approved Sept. 11, 2015

- Nearly two years to the day after Ver. 6.0 approval

- Freely available at <a href="http://www.ibis.org/ver6.1/">http://www.ibis.org/ver6.1/</a>

- Waiting for IBIS 6.2 for possible SAE standardization

- A free syntax checker/parser under development

- Release tentatively expected in November

- Source code license is available for purchase

- Current ibischk6 licensees will receive a free update

\* Other names and brands may be claimed as the property of others

\_

# **Key Features of IBIS 6.1**

- AMI improvements

- Extending IBIS-AMI for PAM4 Analysis

- Model dependencies are supported through a new API

- Buffer directionality for AMI models

- "Traditional" IBIS improvements

- V-t table delay and overclocking

- Package RLC Matrix Diagonals

- Power Pin Package Modeling

- New keyword [Initial Delay] for Submodels and Driver Schedules

- Plus corrections, clarifications, and a recommendation

\* Other names and brands may be claimed as the property of other

## **AMI Improvements**

- PAM4 Signaling

- Expands IBIS's AMI support beyond 2 levels (NRZ) to 4 (PAM4)

- Adds "Modulation", "PAM4\_Mapping", offset and threshold Reserved Parameters

- Re-defines bit-time and clock-times concepts

- Model Dependencies

- Allows the final values of some .ami parameters to depend on the values of others, or of IBIS [Model]s

- New flow resolves dependencies before simulation

- Adds "AMI\_Resolve" and "AMI\_Resolve\_Close" functions

- Adds "Resolve Exists" and "Model Name" Reserved Parameters

- Adds "Dep" Usage Type

\* Other names and brands may be claimed as the property of others

# **AMI Improvements (2)**

- Buffer Directionality

- Paving the way for DDR4 and beyond under AMI

- Associates all Reserved Parameters and Model\_Types with directions (Tx, Rx)

- Most Serdes buffers are Tx-only or Rx-only

- DDR4 DQ buffers are I/O (bi-directional)

- Enables explicit information to be used by EDA tools about the direction for a given I/O buffer in a particular simulation

- Adds "Direction" descriptor to all Reserved Parameters

- Adds "Executable\_Tx" and "Executable\_Rx" subparameters to the [Algorithmic Model] keyword

\* Other names and brands may be claimed as the property of others

# **Traditional IBIS Improvements**

- Overclocking and delay

- [Initial Delay] defines the explicit amount of time, before transitions, embedded in the V-t and any I-t tables

- Supported for both single-Model and [Driver Schedule] structures

- Package and Power Pin Modeling

- Diagonal package matrix values are enforced positive-only, and more mathematical assumptions are documented

- More rigorous rules are defined for EDA tool interpretation of partial Package Models which do not cover the entire [Pin] list

- Added support for [Merged Pins] where a single pin covers the parasitics of multiple physical pins

\* Other names and brands may be claimed as the property of others

٠,

## Feedback is Welcome

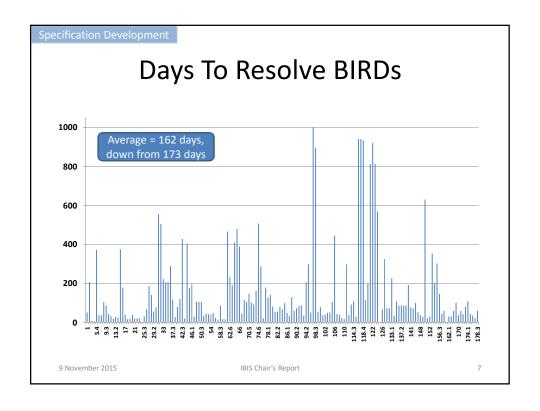

- Anyone may submit IBIS specification change proposals (BIRDs – Buffer Issue Resolution Documents)

- This is the primary mechanism for making IBIS changes

- http://ibis.org/birds/

- Bugs and enhancement requests may also be proposed

- The BUG report covers both

- http://ibis.org/bugs/ibischk

- The IBIS Open Forum and Task Group teleconferences welcome public participation

Your feedback is vital for keeping IBIS relevant and useful to the industry!

\* Other names and brands may be claimed as the property of others

## References

- IBIS Web site: www.ibis.org

- Links to Task Groups available there

- Specifications

- IBIS 6.1: www.ibis.org/ver6.1/

- IBISCHK6 parser (6.1 in progress): www.ibis.org/ibischk6/

- Touchstone: www.ibis.org/touchstone\_ver2.0/

- Summit Presentations

- www.ibis.org/summits/

- IBIS 4.0 Cookbook

- www.ibis.org/cookbook/

- Training

- www.ibis.org/training/

\* Other names and brands may be claimed as the property of others

Page 21 of 111

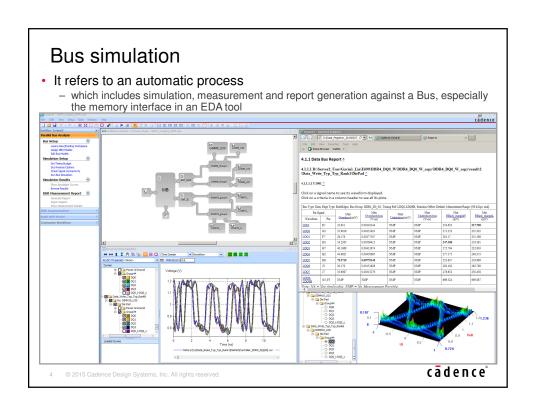

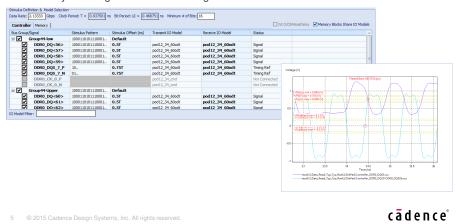

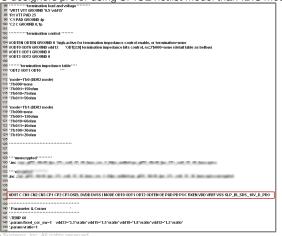

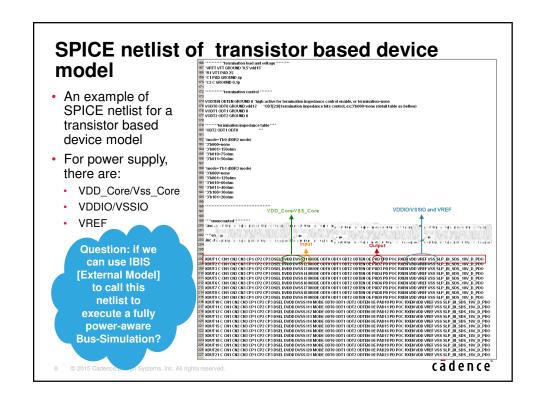

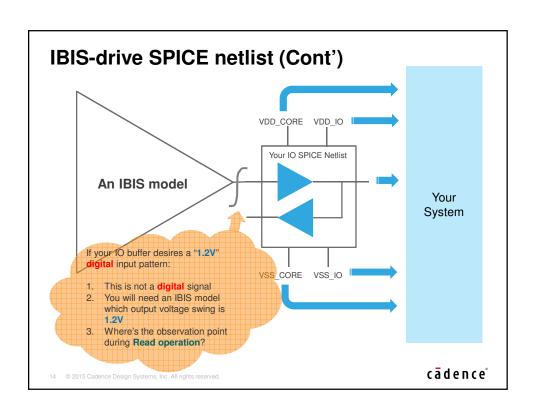

## IBIS model

- Intrinsic format the description of [Pin], [Diff Pin] and [Model Selector]

- IBIS makes Bus simulation possible in an EDA tool

- easy to assign data groups with individual timing reference

- Easy to change models and settings in batch mode

## SPICE netlist

- Maximum freedom in the circuit format but hard for Bus simulation to be implemented

- Has detailed characteristics of circuits which can't be fully described by IBIS model

- Some IC designers prefer using SPICE netlist model than IBIS model

Page 23 of 111

cādence°

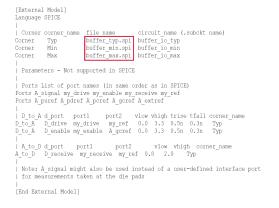

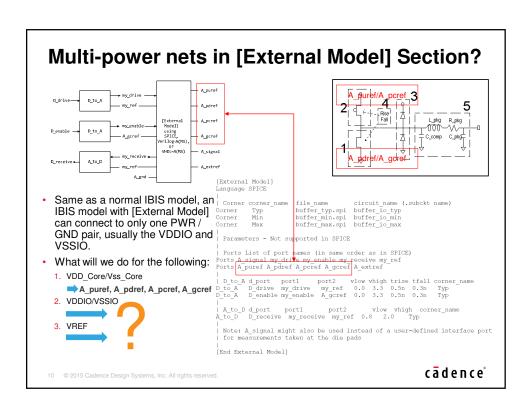

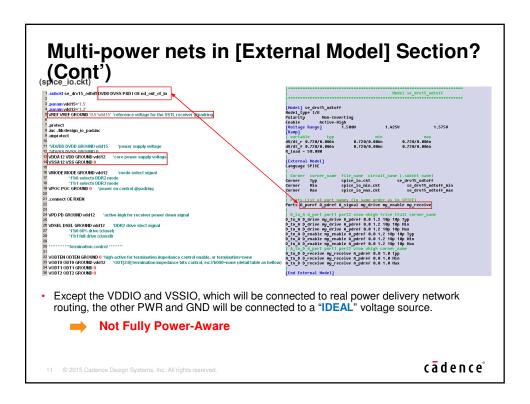

## **IBIS External Model**

Allow a spice netlist to be called by an IBIS model, which means:

- With IBIS format, easy for Bus-Sim to be implemented

- Include detailed characteristics of circuit

7 © 2015 Cadence Design Systems, Inc. All rights reserve

cādence°

Page 24 of 111

Page 25 of 111

Page 26 of 111

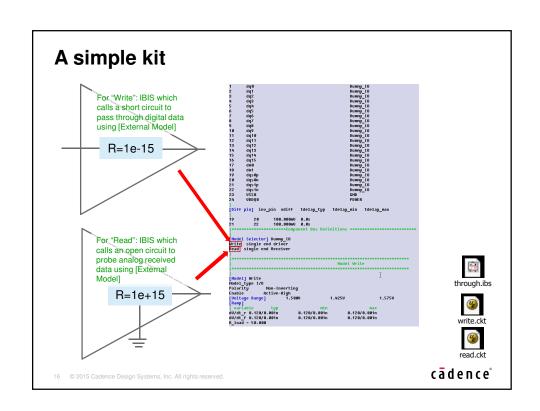

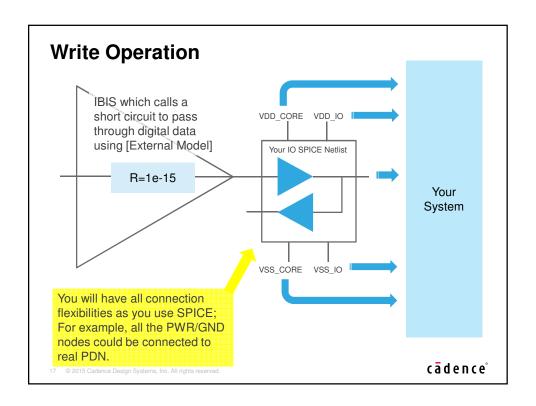

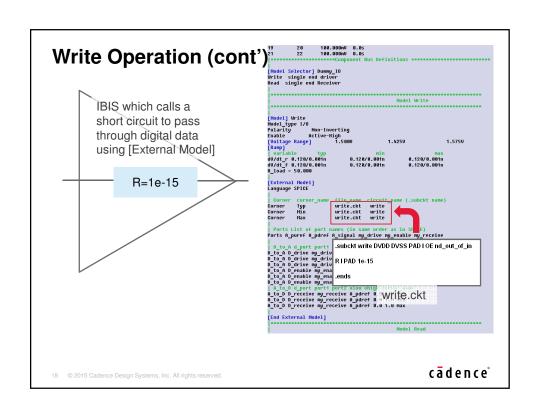

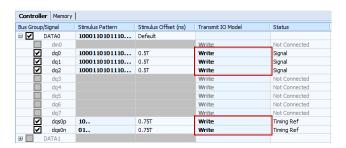

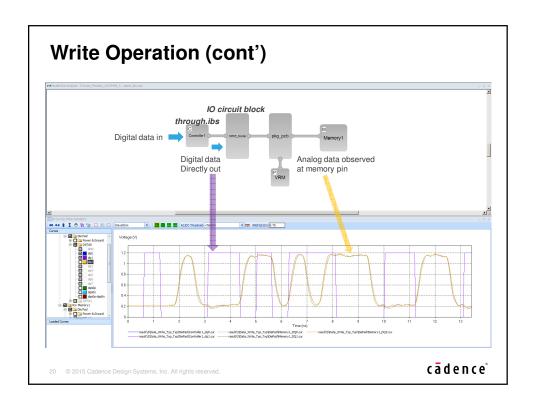

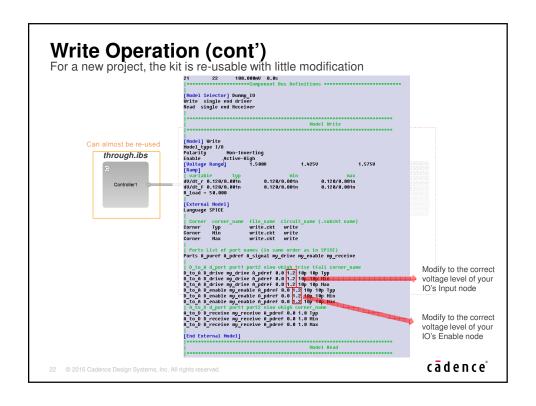

# Write Operation (cont')

In a bus simulation, user can easily switch the model of the Controller's buffer to "Write"

19 © 2015 Cadence Design Systems, Inc. All rights reserved

cādence°

Page 30 of 111

Page 32 of 111

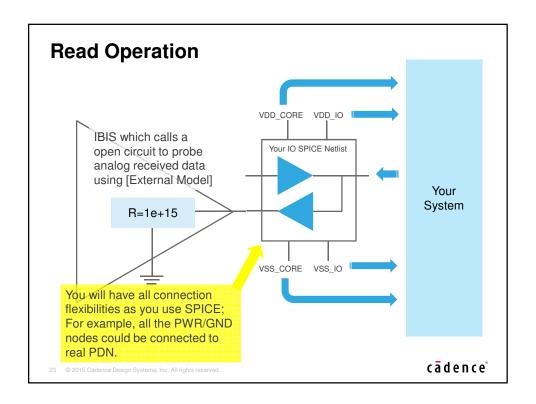

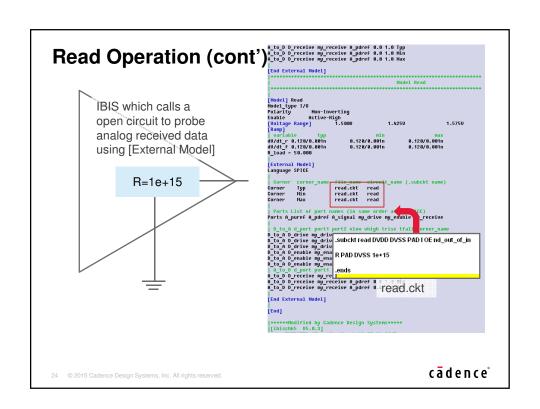

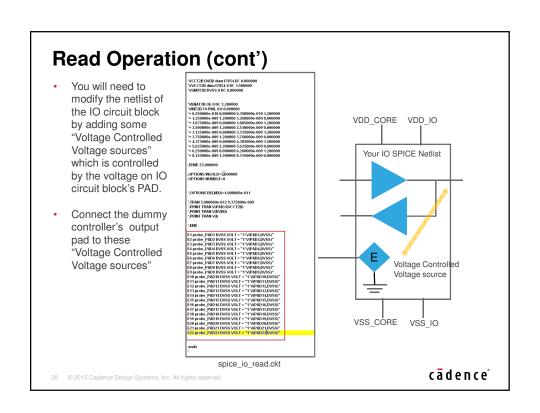

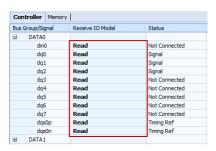

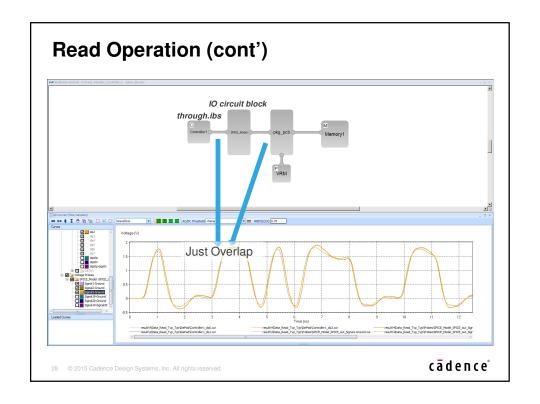

# Read Operation (cont')

In a bus simulation, user can easily switch the model of the Controller's buffer to "Read"

27 © 2015 Cadence Design Systems, Inc. All rights reserved

cādence°

Page 34 of 111

Page 37 of 111

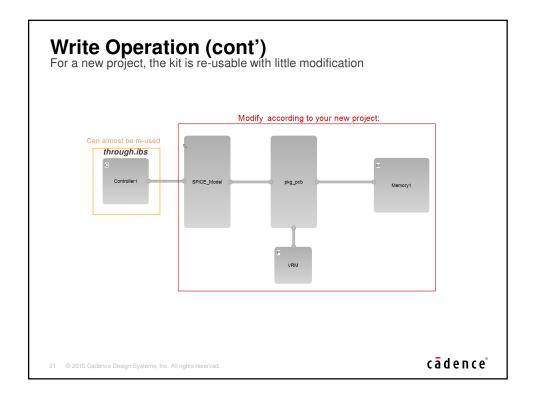

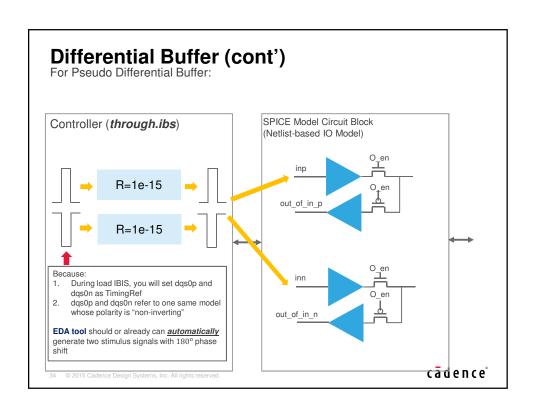

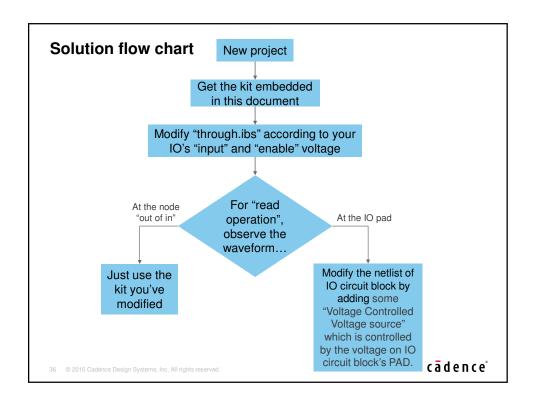

#### **Notes**

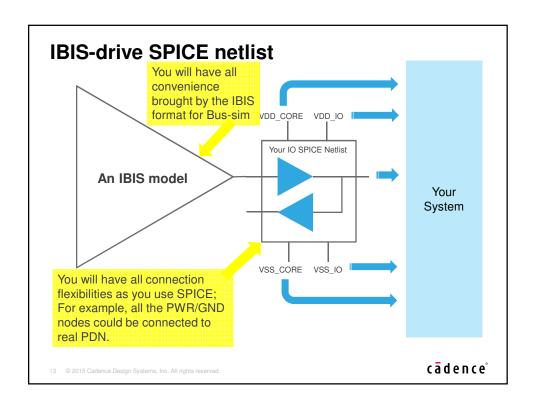

- For analysis of SSN

- With the full flexibilities as using SPICE, this method allows user to do a power-aware SSN analysis between multiple signals and multiple PDNs, such as VDD\_Core/VSS\_Core, VDDIO/VSSIO, VTT and VREF together at the same time.

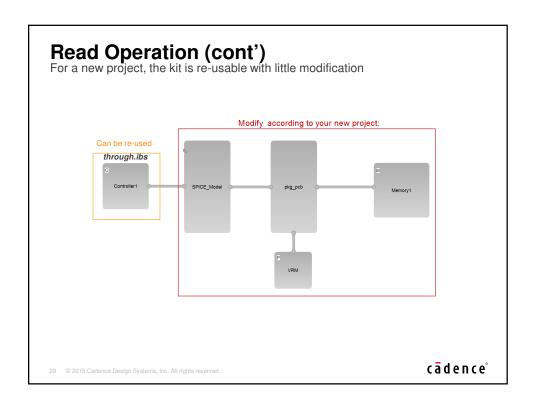

- Model modification and change of topology

- This method requires the change of topology inserting a Spice block but the

wrapping .sp file according to the description in [External Model] is not necessary

since it's ready for use in the kit easy for re-using this kit in a new project of a

new IO.

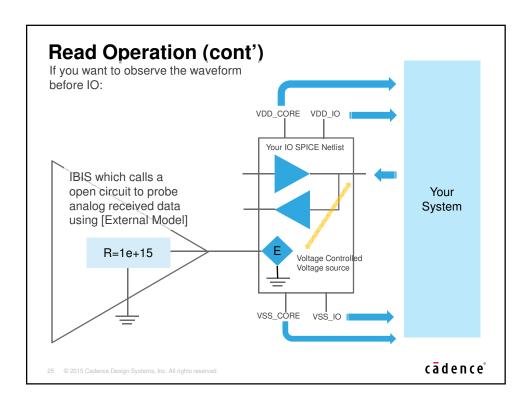

- Read Operation

- As this method requires the change of topology when building topology, during the

analysis of read operation, user will need to modify the netlist of the IO circuit

block by adding some "Voltage Controlled Voltage source" which is controlled by

the voltage on IO circuit block's PAD.

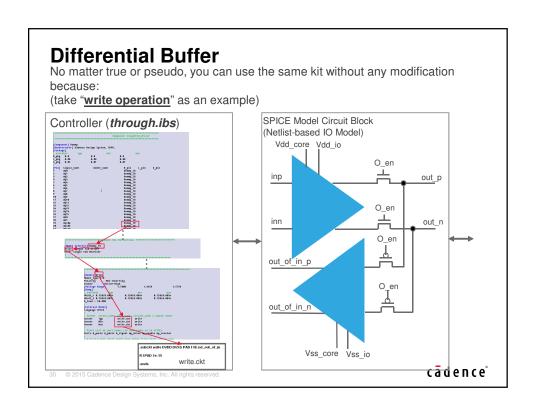

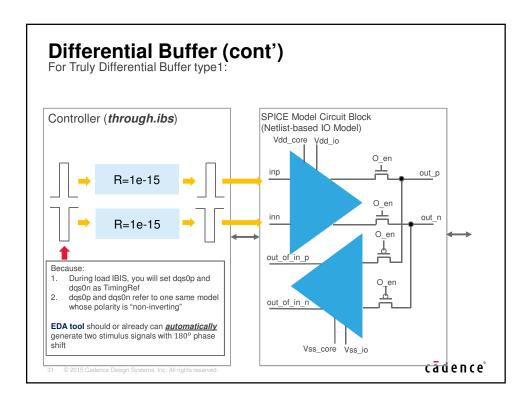

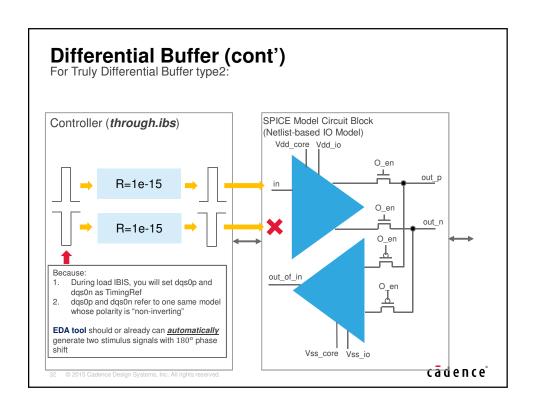

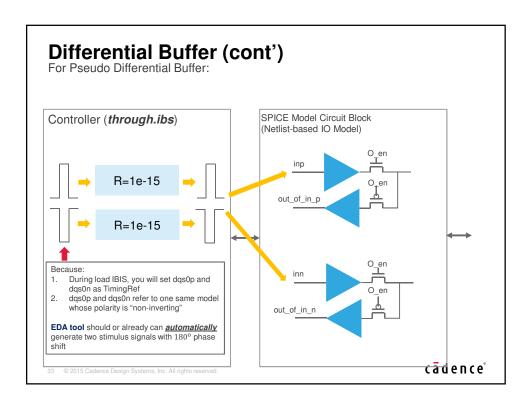

- Differential Buffer

- This method can use the same kit without additional modification for both singleend and differential buffer, no matter it's truly or pseudo.

38 © 2015 Cadence Design Systems, Inc. All rights reserved.

cādence°

# References

IBIS specification (v6.1) http://www.ibis.org/ver6.1/ver6 1.pdf

© 2015 Cadence Design Systems, Inc. All rights reserved.

cādence°

cādence®

A PRACTICAL DOE APPLICATION

IN STATISTICAL SI ANALYSIS

USING IBIS & HOW CAN WE

MAKE IBIS WORK BEYOND

BEST CASE/WORST CASE?

ASIAN IBIS SUMMIT NOVEMBER 9, 2015 SHANGHAI, CHINA

Authors:

Feng Shi, Anders Ekholm, Zilwan Mahmod & David Zhang.

### **AGENDA**

- > IBIS & Statistical analysis

- > DOE as a statistical methodology

- > Practical DDR3/DDR4 Topology problem solved by DOE

- How can we extend IBIS to support confidence interval analysis.

- > Suggestion to enhance IBIS typ, min, max corners with distribution data.

- > Conclusion

DOE&IBIS | Ericsson Presentation | Asian IBIS Summits | October 2015 | Page 2 (14

# IBIS & STATISTICAL ANALYSIS

- > IBIS based SI analysis uses:

- Behavioral buffer models. typ, min, max (BC/WC)

- Trace modeling of topology BC/WC

- Via modeling BC/WC

- > Best Case / Worst case analysis assumes:

- 100% confidence interval. Every produced individual works.

- Statistical SI analysis predicts:

- Defects at a given confidence interval.

- Help manage overdesign and possible BC/WC failures.

DOE&IBIS | Ericsson Presentation | Asian IBIS Summits | October 2015 | Page 3 (14)

#### DOE AS A STATISTICAL METHODOLOGY

- DOE Design Of Experiments will fit a model to our solutions space (often used is a RSM Response Surface Model)

- Uses much fewer simulation than sweep analysis or Monte Carlo analysis.

- > Catches cross term interaction missed by OFAT analysis.

- (OFAT, One Factor At a Time)

- RSM used to predict the fitted part of the solutions space and to give Confidence Intervals for the predicted respons.

DOE&IBIS | Ericsson Presentation | Asian IBIS Summits | October 2015 | Page 4 (14)

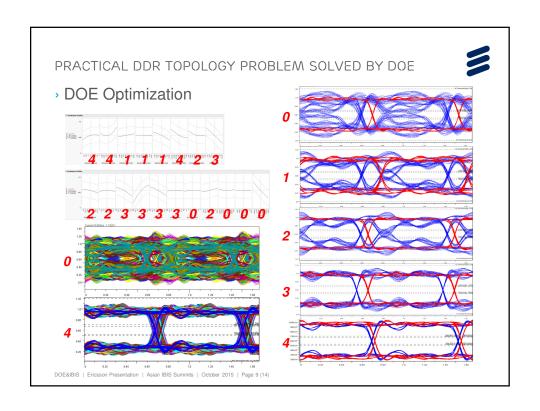

#### PRACTICAL DDR TOPOLOGY PROBLEM SOLVED BY DOE

- Problem of ringing in a high speed DDR3/DDR4 address/command/control bus in memory down solutions with thick PCB's >1mm.

- Find an optimal topology that solves the problem with a given confidence e.g. 95%

DOE&IBIS | Ericsson Presentation | Asian IBIS Summits | October 2015 | Page 5 (14

#

#### PRACTICAL DDR TOPOLOGY PROBLEM SOLVED BY DOE

| Design Parameter                                  | Factor            | Factor Type | Min       | Тур                    | Max       | Analysis Type            |

|---------------------------------------------------|-------------------|-------------|-----------|------------------------|-----------|--------------------------|

| Length of lead Tline                              | 01Length_TLead    | Continuous  | 1.5inch   | 2.25inch               | 3 inch    | Design                   |

| Length of first load Tline                        | 02Length_TLoad1   | Continuous  | 0.4inch   | 0.7inch                | 1 inch    | Design                   |

| Length of second load Tline                       | 03Length_TLoad2   | Continuous  | 0.4 inch  | 0.7inch                | 1 inch    | Design                   |

| Length of third load Tline                        | 04Length_TLoad3   | Continuous  | 0.4 inch  | 0.7inch                | 1 inch    | Design                   |

| Length of forth load Tline                        | 05Length_TLoad4   | Continuous  | 0.4 inch  | 0.7inch                | 1 inch    | Design                   |

| Length of Tline to the termination resistor       | 06Length_TRterm   | Continuous  | 0.06 inch | 0.53inch               | 1 inch    | Design                   |

| Length of memory fanout Tline                     | 07Length_TBreakin | Continuous  | 0.02 inch | 0.04inch               | 0.06 inch | Design                   |

| Routing layer/ Via barrel length                  | 08Layer_Via       | Categorical | 3, 5,     | 5, 7, 18, 20, 22 layer |           | Design                   |

| Driver impedance of controller                    | 09Z_Controller    | Categorical | 34ohm     | 40 ohm                 | 48 ohm    | Design                   |

| Via anti-pad size                                 | 10C_Via           | Categorical | 1=hiC     | 2=typC                 | 3=lowC    | Design                   |

| Impedance of lead Tline                           | 11Z_TLead         | Categorical | 40 ohm    | 50 ohm                 | 60 ohm    | Design&<br>Manufacturing |

| Impedance of load Tline                           | 12Z_TLoad         | Categorical | 40 ohm    | 50 ohm                 | 60 ohm    | Design&<br>Manufacturing |

| Impedance of Tline to the<br>termination resistor | 13Z_TRterm        | Categorical | 40 ohm    | 50 ohm                 | 60 ohm    | Design&<br>Manufacturing |

| Impedance of memory fanout Tline                  | 14Z_TBreakin      | Categorical | 40 ohm    | 50 ohm                 | 60 ohm    | Design&<br>Manufacturing |

| Input capacitance of memory IO buffer             | 15C_MemoryIO      | Categorical | 2=0.2     | 4=0.4                  | 6=0.6     | Manufacturing            |

| Termination resistor                              | 16R_Rterm         | Continuous  | 36 ohm    | 39 ohm                 | 43 ohm    | Design                   |

| Packaging resistance of memory                    | 17R_Pkg           | Continuous  | 0.05 ohm  | 0.525 ohm              | 1 ohm     | Manufacturing            |

| Packaging inductance of memory                    | 18L_Pkg           | Continuous  | 0.5nH     | 1.75nH                 | 3nH       | Manufacturing            |

| Packaging capacitance of memory                   | 19C_Pkg           | Continuous  | 0.2pF     | 0.5pF                  | 0.8pF     | Manufacturing            |

DOE&IBIS | Ericsson Presentation | Asian IBIS Summits | October 2015 | Page 7 (14)

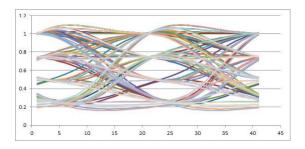

#### PRACTICAL DDR TOPOLOGY PROBLEM SOLVED BY DOE

#### > Prediction Profiler

- Confidence interval ----> Quality

- Slope ----> Influence /Importance

- Vertical red line -----> "What if " analysis & Interactions

- Desirability function -----> Optimization

DOE&IBIS | Ericsson Presentation | Asian IBIS Summits | October 2015 | Page 8 (14)

# HOW CAN WE EXTEND IBIS TO SUPPORT CONFIDENCE INTERVAL ANALYSIS.

- IBIS currently and traditionally uses a typ, min, max parameter definition.

- This is based on a Best/Worst case scenario analysis. E.g. 100% confidence.

- Best/Worst case analysis has served us well during the years and still does in some cases, however more and more cases will not reach design closure using Best/Worst case analysis.

- When it does not reach design closure how will we know how many of our produced units will fail ?????

DOE&IBIS | Ericsson Presentation | Asian IBIS Summits | October 2015 | Page 11 (14)

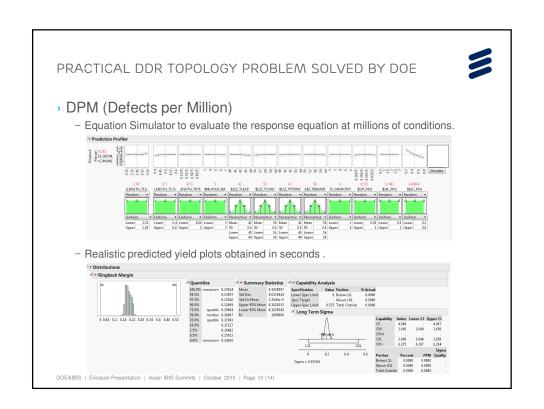

# ADD AN OPTION TO IBIS TYP, MIN, MAX CORNERS TO USE DISTRIBUTION DATA AS A PARAMETER DEFINITION.

- If we add an option to IBIS to support distribution data for parameters as an average/mean and a variation/sigma.

- If we feel we can not assume a standard distribution we could even add support for other distributions.

- These parameters could be used in DOE analysis scenarios and could help us predict confidence intervals for our products as well as DPM (Defect Per million) predictions.

DOE&IBIS | Ericsson Presentation | Asian IBIS Summits | October 2015 | Page 12 (14)

#### CONCLUSIONS.

- > Our design work is moving beyond Best case, Worst case analysis.

- We need to start working on an infrastructure both in modeling and tool support for statistical analysis.

- Many of us EE's need to go back to our statistics books and review statistical analysis.

- > We need to secure that we can get the correct information from IC and PCB vendors on parameter distributions.

- > SI/PI statistical analysis is the next step to secure our product quality.

DOE&IBIS | Ericsson Presentation | Asian IBIS Summits | October 2015 | Page 13 (14

# IBIS Interconnect BIRD Update Walter Katz Signal Integrity Software, Inc. Asian IBIS Summit Shanghai, China November 9, 2015

# **Overview**

- IBIS Interconnect Task Group

- Models Represent Package and On-Die Interconnect

- On Die, Package, Supply and Signal Interconnect can be Combined or Kept Separate

- IBIS Interconnect Model Terminals

- Examples

2

# IBIS Interconnect Task Group

- Meets Wednesdays 8AM PDT

- http://www.ibis.org/interconnect\_wip/

- **Major Contributors**

- Altera

- Cadence Design Systems

- Intel Corp

- Keysight Technologies

- Mentor Graphics

- Micron Technology Signal Integrity Software

- Synopsys

- Teraspeed Labs

- David Banas

- **Bradley Brim**

- Michael Mirmak (Chair)

- Radek Biernacki

- Arpad Muranyi

- Justin Butterfield, Randy Wolff

- Walter Katz, Mike LaBonte

- Rita Horner

- **Bob Ross**

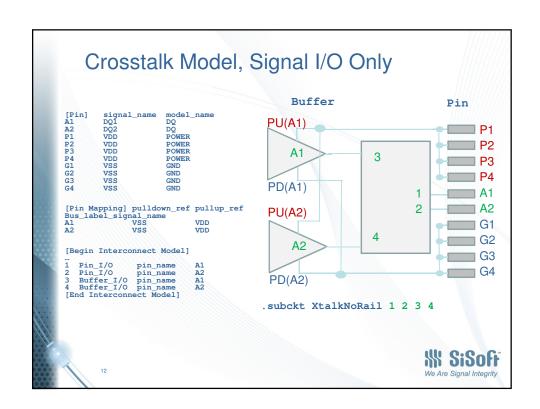

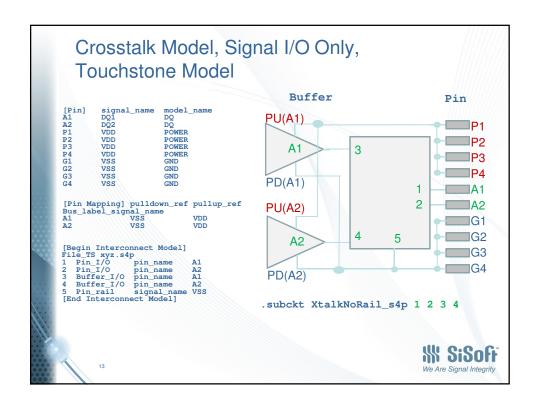

# Models Represent Package and On-Die Interconnect

- Currently IBIS supports lumped coupled RLC models or lossless uncoupled distributed models.

- New modeling will support broadband, coupled, signal interconnect and power distribution models.

- Languages Supported

- IBIS-ISS

- IBIS Interconnect SPICE Subcircuit (IBIS-ISS) Specification, Version 1.0, October 7th 2011 http://www.ibis.org/ibis-iss\_ver1\_0.pdf

- Touchstone <sup>®</sup>

- http://www.ibis.org/touchstone\_ver2.0/

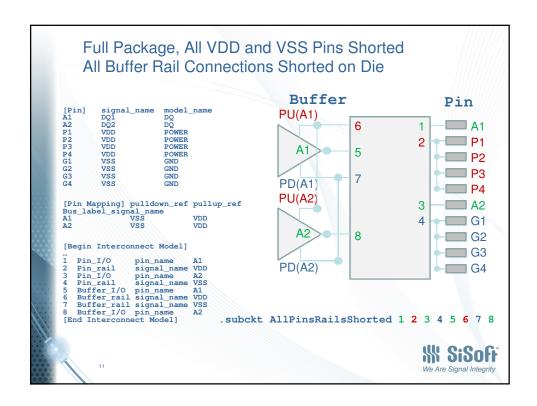

# On Die, Package, Supply and Signal Interconnect can be Combined or Kept Separate

- Supports separate on-die and package interconnect models and combined on-die and package interconnect models

- Independent Supply and Signal Interconnect Models

- · Coupled Supply and Signal Interconnect Models

- Singled Ended and Differential Interconnect Models

# Similar Approach for Both IBIS and EBD

- IBIS (.ibs) Interconnect Model Terminals

- Pins ([Pins])

- Die Pads

- Buffers

- EBD (.ebd) Interconnect Model Terminals

- A similar approach will be used to update EBD (Electrical Board Description) or EMD (Electrical Module Description) to support broadband, coupled interconnect models

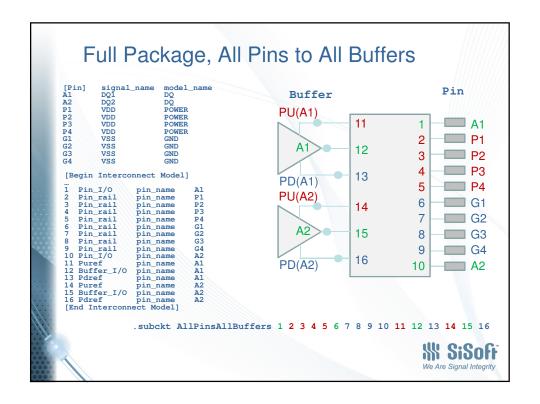

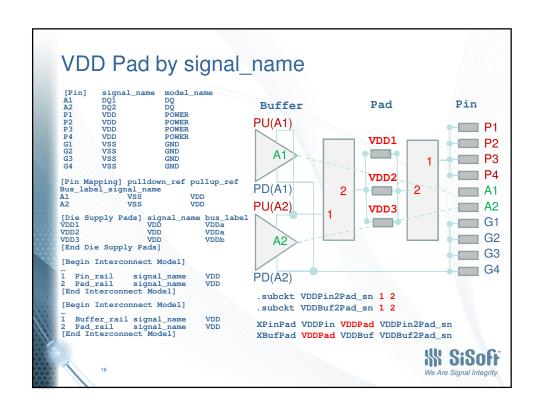

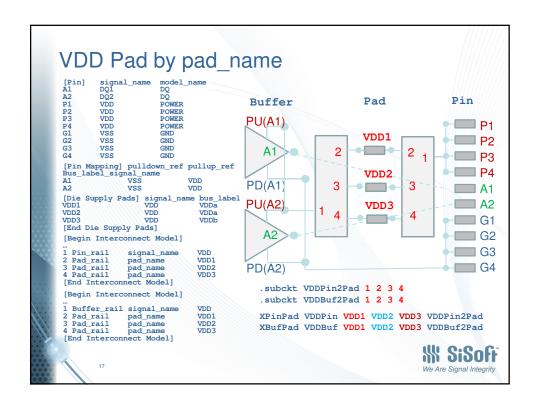

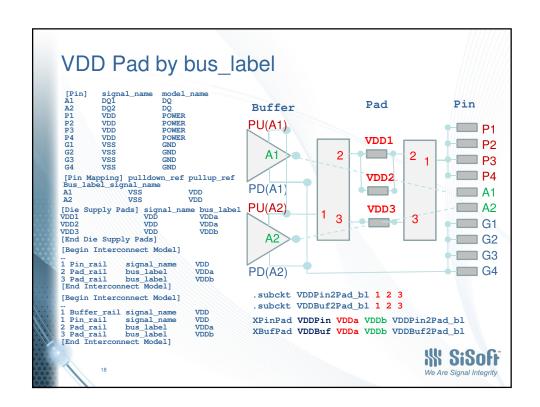

#### **IBIS** Interconnect Model Terminals

- Pins

- Pin\_name (aka Pin Number)

- Signal\_name (assumes signal\_name pins shorted)

- Bus\_label (allows sub-groups of rail signal\_name pins)

- Pads (Die/Package Interface)

- Pin\_name (aka Pin Number) for I/O connections

- Pad\_name for rail connections

- Signal\_name (assumes signal\_name pads shorted)

- Bus\_label (allows sub-groups of rail signal\_name pads)

- Buffers

- Signal (I/O)

- Rails

- Pin\_name and (puref/pdref/pcref/gcref)

- Signal\_name (assumes signal\_name terminals shorted)

- Bus\_label (allows sub-groups of rail buffer terminals)

# **Interconnect Model Terminals**

- <Terminal Number> <Terminal Type> <Qualifier>

- X: I/O pin\_name

- Y: Supply pin\_name, signal\_name or bus\_label

- Z: Supply pad\_name

| Terminal_Type | pin_name | signal_name | bus_label | pad_name |

|---------------|----------|-------------|-----------|----------|

| Buffer_I/O    | Х        |             |           |          |

| Puref         | Х        |             |           |          |

| Pdref         | Х        |             |           |          |

| Pcref         | Х        |             | N .       |          |

| Gcref         | Х        |             |           |          |

| Extref        | Х        |             |           |          |

| Buffer_rail   |          | Υ           | Y         |          |

| Pad_I/O       | X        |             |           |          |

| Pad_rail      |          | Υ           | Y         | Z        |

| Pin_I/O       | X        |             |           |          |

| Pin_rail      | Y        | Υ           | Υ         |          |

|               |          |             |           |          |

Page 51 of 111

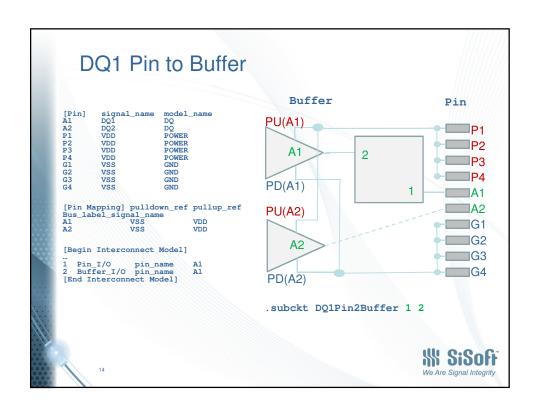

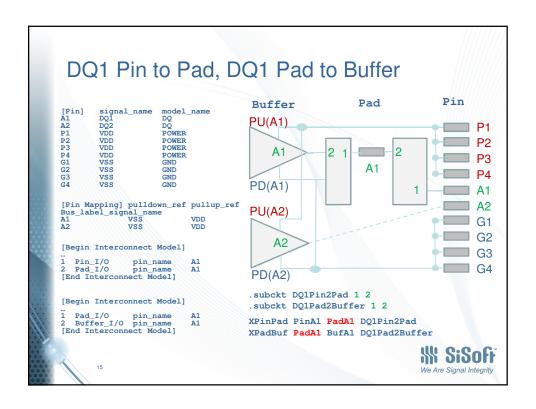

```

Interconnect Model Examples

[Interconnect Model]

DQ1

| IBIS-ISS Model

File IBIS-ISS DQ.iss

Param Length Value

0.1

Number_of_Terminals =

1 Pin_I/O

pin_name

A1

2 Buffer_I/O

pin_name

A1

[End Interconnect Model]

[Interconnect Model]

| Touchstone File Shortcut

File_TS

A1.s2p

Number_of_Terminals = 3

1 Pin_I/O

pin_name

Α1

2 Buffer_I/O

pin_name

A1

3 Pin rail

signal_name

VSS

[End Interconnect Model]

```

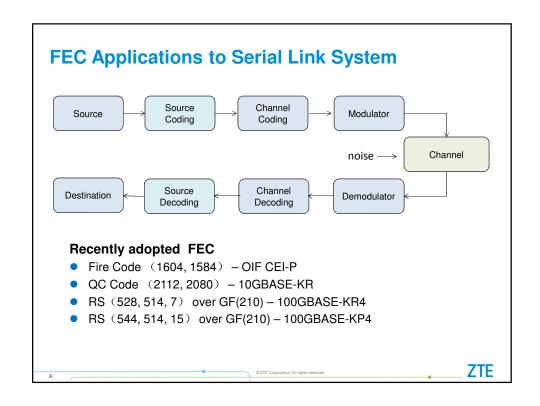

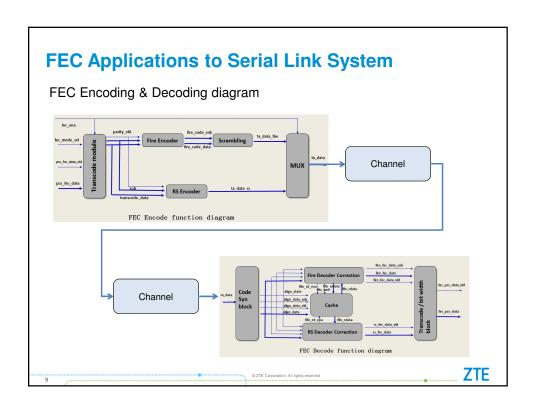

# **FEC Applications to Serial Link System** FEC Applications on the 100GE standard of IEEE802.3bj HIGHER LAYERS LLC OR OTHER MAC CLIENT Backplane System —100GBASE-KR4 FEC block is placed between PCS and SESSION Reed-Solomon Code is suggested, NETWORK defined in clause 91 DATA LINK RS(528,514,7) — about 5dB gain PHY = PHYSICAL LAYER DEVICE PMA = PHYSICAL MEDIUM ATTACHMENT PMD = PHYSICAL MEDIUM DEPENDENT RS-FEC = REED-SOLOMON FEC XLGMII = 40 GIGABIT MEDIA INDEPENDENT INTERFACE NOTE 1-OPTIONAL **ZTE**

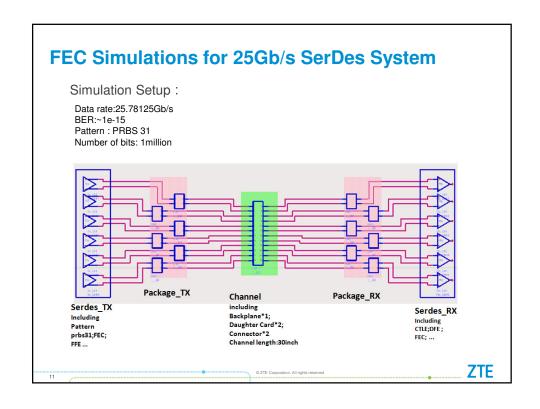

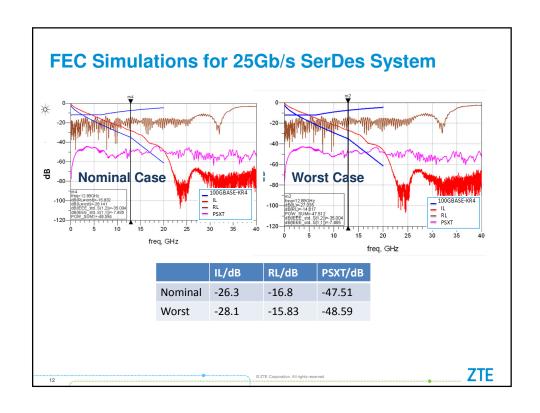

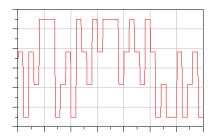

# FEC Simulations for 25Gb/s SerDes System

Comparison between with and without FEC

|        | Nominal Case |           | Worst      |           |                    |

|--------|--------------|-----------|------------|-----------|--------------------|

| AtBER  | Width/*UI    | Height/mV | Width/%*UI | Height/mV | Condition          |

| ^1e-12 | 16.2%        | 23.1      | 4.51%      | 5.39      | With emphasis/DFE; |

| ^1e-15 | 12.2%        | 17.4      | 0.07%      | 0.00      |                    |

| ^1e-17 | 9.92%        | 14.2      | 0.00%      | 0.00      |                    |

| ^1e-12 | 42.5%        | 57.0      | 42.2%      | 48.6      | With emphasis/DFE; |

| ^1e-15 | 40.6%        | 54.8      | 40.2%      | 46.4      |                    |

| ^1e-17 | 39.5%        | 53.4      | 38.9%      | 45.1      |                    |

Eye diagram at the BER of 1e-12 of the channel simulation can not meet the requirement of 100GE Standard without FEC.

Crosstalk must be concerned in the channel simulation.

\_\_\_ZTE

13

## FEC Simulations for 25Gb/s SerDes System

Comparison between with and without FEC

|        | Nominal Case |           | Worst Case |           |                                    |  |

|--------|--------------|-----------|------------|-----------|------------------------------------|--|

| AtBER  | Width/*UI    | Height/mV | Width/%*UI | Height/mV | Condition                          |  |

| ^1e-5  | 33.5%        | 63.6      | 32.6%      | 54.6      |                                    |  |

| ^1e-6  | 29.1%        | 62.4      | 23.2%      | 53.5      | With emphasis/DFE;<br>Without FEC; |  |

| ^1e-7  | 25.9%        | 61.4      | 17.1%      | 52.6      | ,                                  |  |

| ^1e-12 | 42.5%        | 57.0      | 42.2%      | 48.6      |                                    |  |

| ^1e-15 | 40.6%        | 54.8      | 40.2%      | 46.4      | With emphasis/DFE;<br>With FEC;    |  |

| ^1e-17 | 39.5%        | 53.4      | 38.9%      | 45.1      |                                    |  |

Eye diagram at the BER of 1e-15 of the channel simulation can meet the requirement of 100GE Standard with FEC, while relaxing the BER requirement from 1e-15 to 1e-5 or 1e-6.

© ZTE Corporation. All rights reserved

ZTE

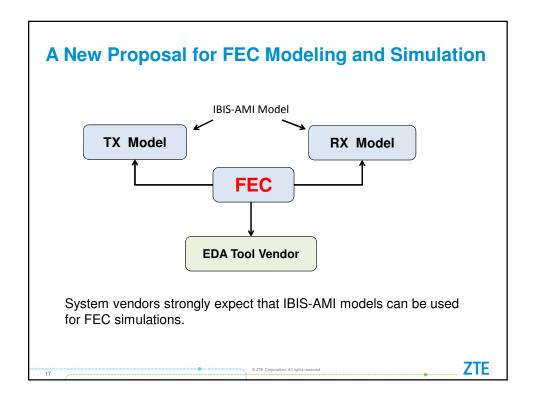

## A New Proposal for FEC Modeling and Simulation

#### **Current Situation:**

IBIS-AMI model

(my\_AMIname | Header, such as AMI\_version ... | Function such as, GetWave\_Exists ... | Modulation such as, NRZ, PAM4 ... | Jitter such as, Dj ... | Repeater ...

EDA Tool

FEC blocks are not supported in IBIS-AMI model nor in EDA tool

System Simulation

Uses the same Serdes IP on the TX and RX end supported by the IC Vendor

© ZTE Corporation. All rights reserved ZTE

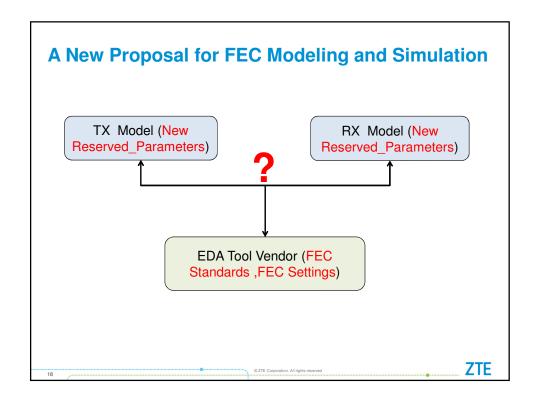

#### A New Proposal for FEC Modeling and Simulation

#### [Reserved\_Parameters] / [Model\_Specific] → tx\_fec / rx\_fec ?

```

On the transmit end

Add the branch 'tx_fec' into Model_Specific, then add parameters, config

min/typ/max, mode on/off, such as

(Model_Specific

(tx_fec

(config (Usage In)(List "min" "typ" "max")(Type String)

(Default "typ") (Description "enable fec function setting")) (mode (Usage In) (Format List "on" "off") (Type String)

(Default "off") (Description "fec control mode"))

On the receiver end.

{\tt Add\ the\ branch\ `rx\_fec'\ into\ Model\_Specific,\ then\ add\ the\ same\ parameters}

to respond the tx configuration, such as

(Model_Specific

(rx_fec

(config (Usage In) (List "min" "typ" "max") (Type String)

(Default "typ") (Description "enable fec function setting")) (mode (Usage In) (Format List "on" "off") (Type String)

(Default "off")(Description "fec control mode"))

```

**ZTE**

**Agenda**

- Introduction

- FEC Applications to Serial link System

- FEC Simulations for 25Gb/s SerDes System

- A New Proposal for FEC Modeling and Simulation

- Summary

#### **Summary**

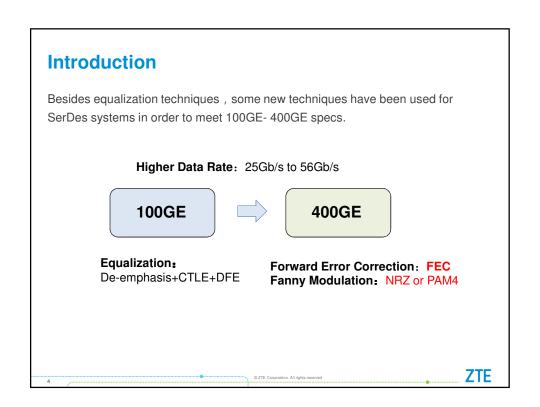

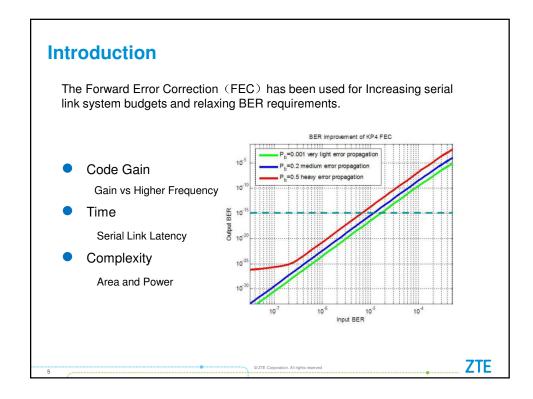

- FEC can be used for many dispersion and noise limited systems, such as high-speed serial link systems in order to meet 100GE- 400GE specs.

- FEC relaxes PHY BER requirement from 1e-15 to 1e-06 for serial link systems.

- FEC is one of critical techniques for 25-56Gb/s SerDes systems and IBIS-AMI model is an efficient solution for complex IO modeling.

- System vendors strongly expect that IBIS-AMI models can be used for FEC simulations.

- "One model, one platform, one simulator" needed for both passive and active components, such as FFE, DFE, FEC ...

21 OZTE Corporation, All rights reserved ZTE

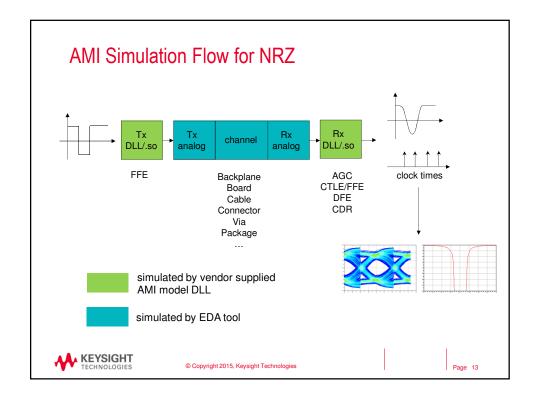

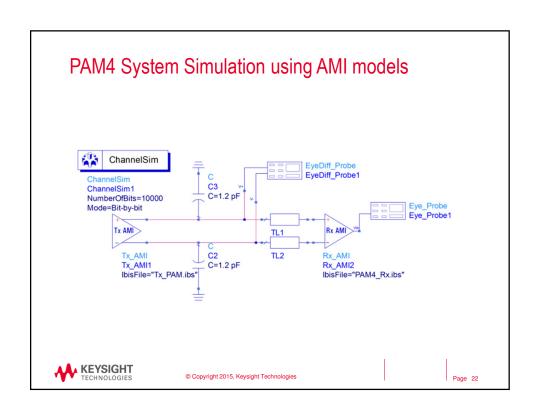

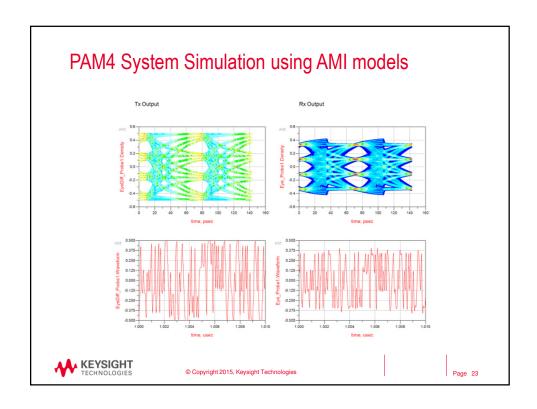

Agenda - Overview of PAM4 - Challenges in PAM-4 Link Designs - Solutions for Simulating PAM-4 Links with IBIS-AMI Models KEYSIGHT TECHNOLOGIES

© Copyright 2015, Keysight Technologies

# Enabling the next step in link data rate

- 56 Gb/s lane data rate will be the principle enabler for 400GbE

- Two contenders for implementing 56Gb/s lane data rate:

- 56G NRZ

- + No new science linear evolution from 25/28G lanes

- · Difficult to manage channel loss & channel reflections

- 28 Gbaud PAM-4

- · + Channel loss problems worked out with 28 Gb/s NRZ

- - 30% chip real estate, 35+% more power

- - Lose 9.6 dB usable SNR

- · Lots of new challenges little experience to draw from

- Both signaling technologies will be utilized to enable 400GbE

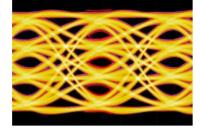

# NRZ (Non-Return-to-Zero) VS. PAM (Pulse Amplitude Modulation) NRZ (PAM-2) PAM-4 2 amplitude levels 1 bit of information in every symbol 56 Gbaud for 56 Gb/s 4 amplitude levels 2 bits of information in every symbol 2 throughput for the same Baud rate 28 Gbaud for 56 Gb/s, half of the loss in dB Lower SNR, more susceptible to jitter & noise More complex TX/RX design, higher cost

# Moving from NRZ to PAM-4

Revolutionary – not Evolutionary

- Jump from 10G NRZ to 25G introduced many new concepts....

- Still a linear transition (more or less)

- Multi-Level signaling changes all the rules in place for 50+ years!

- · Saturating to linear output stages

- More complex (and precise) level threshold detection for inputs

- · Finite rise time creates inherent ISI

- · How to implement clock recovery?

- · How will DFE need to change?

- ...

- ....

# Agenda

- Overview of PAM4

- Challenges in PAM-4 Link Designs

- Solutions for Simulating PAM-4 Links with IBIS-AMI Models

© Copyright 2015, Keysight Technologies

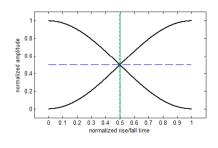

# Implementing PAM-4 links = "New Science"

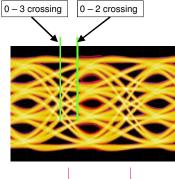

Inherent ISI requires receivers to be less susceptible to pattern dependent jitter

----- decision threshold

----- Amount of switching jitter

# Implementing PAM-4 links = "New Science" (2)

- Some of the other challenges learned so far include...

- Eye time skew from linear drive of VCSELs

- · Upper eyes arrive sooner than lower transitions

- Each eye needs to be sampled with independent delay

#### Challenges shifting from NRZ to PAM

PAM-4 is one of the enablers of 56 G lane rate supporting 400G links

Multi-level signaling changes all the rules that have in place for 50+ years! Saturating to linear output stages

More complex (and precise) level threshold detection for inputs

Finite rise time creates inherent ISI How to implement clock recovery?

How will DFE need to change?

Page 9

#### Other impairments that challenge PAM-4 receivers

- · Non-linearity Amplitude compression in lower eyes

- · Non uniform effective SNR across individual eyes

- Receivers sensitive to additional artifacts beyond "traditional" jitter types in NRZ

- · Still learning what impairments cause problems

- New measurements WILL be defined for Tx Outputs

- · New stress types WILL be defined for Rx Input testing

#### Challenges in PAM-4 SerDes Design

- Nonlinearity between levels due to saturation

- CDR

- Upper and lower eye slicer reference level tuning

- Timing skews between three slicers for optimal sampling

- Analog based architecture vs ADC based architecture

- **–** ..

#### Challenges in PAM-4 Link Simulation

- How to capture PAM-4 SerDes behaviors

- How to measure PAM-4 eyes (three stacking eyes vs single eye in NRZ)

© Copyright 2015, Keysight Technologies

Page 1

#### Agenda

- Overview of PAM4

- Challenges in PAM-4 Link Designs

- Solutions for Simulating PAM-4 Links with IBIS-AMI Models

© Copyright 2015, Keysight Technologies

#### **IBIS-AMI Based PAM-4 Link Simulation**

- AMI successfully brings SerDes vendors' models and EDA tools together

- Interoperability: AMI defines a common interface between SerDes model and channel simulator

- IP protection: SerDes behavior is concealed in model DLL/shared object

- Superior simulation speed

- AMI has been widely adopted by IC, system and EDA companies

© Copyright 2015, Keysight Technologies

#### AMI Modeling for PAM4 Signaling: Tx

- For NRZ, input stimulus to Tx DLL has two levels (0.5 and -0.5V), representing 1 and 0 bits

- For PAM4, input to Tx DLL has four levels (0.5, 0.5/3, -0.5/3 and -0.5V), representing symbols 0, 1, 2 and 3

- Tx DLL/.so interface is unchanged for PAM4

© Copyright 2015, Keysight Technologies

Page 15

#### Tx AMI Reserved Parameters

#### Modulation

- String. Allowed values are "NRZ" and "PAM4"

- Optional. Default is "NRZ"

#### PAM4\_Mapping

- String of four non-repeated integers 0, 1, 2 and 3 (e.g. "0123")

- Bit pairs 00, 01, 10 and 11 map to symbol levels specified by 1<sup>st</sup>, 2<sup>nd</sup>, 3<sup>rd</sup> and 4<sup>th</sup> integers, respectively

- Optional. Default is "0132" (Gray coding)

© Copyright 2015, Keysight Technologies

#### AMI Modeling for PAM4 Signaling: Rx

- PAM4 Rx symbol decision relies on three slicers

- Slicer thresholds can be adjusted adaptively and can vary with time

- Sampling time skew can be applied independently to each slicer for optimal result and can vary with time

- Rx model should provide transient slicer threshold and timing skew information

© Copyright 2015, Keysight Technologies

Page 17

#### Rx AMI Reserved Parameters

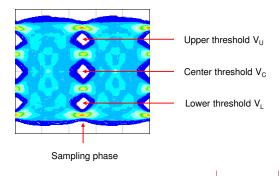

#### PAM4\_UpperThreshold, PAM4\_CenterThreshold, PAM4\_LowerThreshold

- Float. Upper, center and lower slicer thresholds

- Optional. If not provided by models, EDA tools have to guess their values for SER calculations

#### PAM4 UpperEyeOffset, PAM4 CenterEyeOffset, PAM4 LowerEyeOffset

- Float. Upper, center and lower slicer sample time offsets relative to clock times

- Optional. Default is 0

Rx model can update values of these parameters in AMI\_Init and AMI\_GetWave and return them through the *AMI\_parameters\_out* string argument

© Copyright 2015, Keysight Technologies

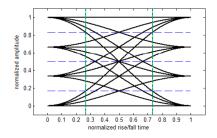

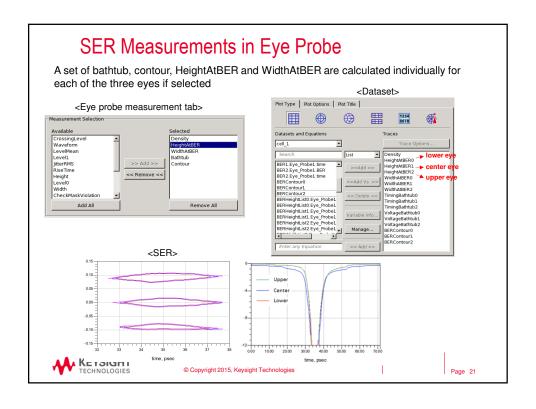

#### Symbol Error Rate (SER) Measurement

- Measure bathtubs and SER contours individually for each of the three stacking eyes

- Horizontal eye center is placed at clock time + offset to capture CDR behavior and skew

- Vertical eye center is placed at threshold  $V_{U}/V_{C}/V_{L}$  to capture slicer level fluctuation

|            | Logic high traces | Logic low<br>traces |

|------------|-------------------|---------------------|

| Upper eye  | $v_3(t) - V_U(t)$ | $v_2(t) - V_U(t)$   |

| Center eye | $v_2(t) - V_C(t)$ | $v_1(t) - V_C(t)$   |

| Lower eye  | $v_1(t) - V_L(t)$ | $v_0(t) - V_L(t)$   |

$(v_0,\,v_1,\,v_2$  and  $v_3$  are waveforms of expected 0, 1, 2 and 3 symbols, respectively)

© Copyright 2015, Keysight Technologies

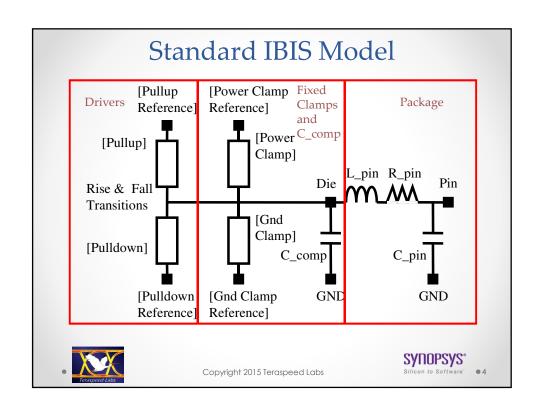

#### Some Results for General K-table **Extraction Proposal Using SPICE**

Bob Ross, Teraspeed Labs bob@teraspeedlabs.com Xuefeng Chen, Synopsys xfchen@synospsys.com

> Asian IBIS Summit Shanghai, China November 9, 2015

(From material originally presented January 30, 2015, this presentation given Oct. 28, 2015)

Copyright 2015 Teraspeed Labs

#### **Updated Material**

- More derivation detail: January 30, 2015, "General K-Table Extraction Proposal Using SPICE"

- o http://www.ibis.org/summits/jan15/ross2.pdf

- Contains Summit references

- Some results and other observations here

- Purpose Use SPICE for PROTOTYPING IBIS extraction algorithms (with general C\_comp, on-die, package structures and fixture loads)

SYNOPSYS\*

#### Overview

- Fixed C\_comp to local GND for extraction

- Detailed C\_comp model from S-parameters or IBIS-ISS allowed

- IBIS Interconnect BIRD proposal adds on-die and package models

- SPICE-based extraction proposal supports total path measurement with more detailed C\_comp/ondie/package structures

- Limitations exist

Copyright 2015 Teraspeed Labs

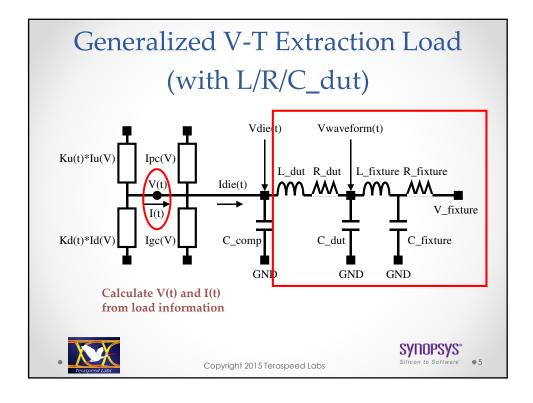

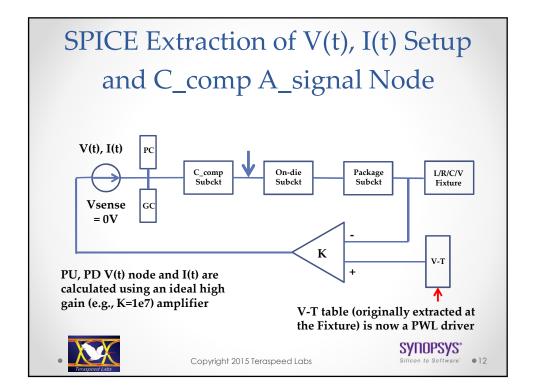

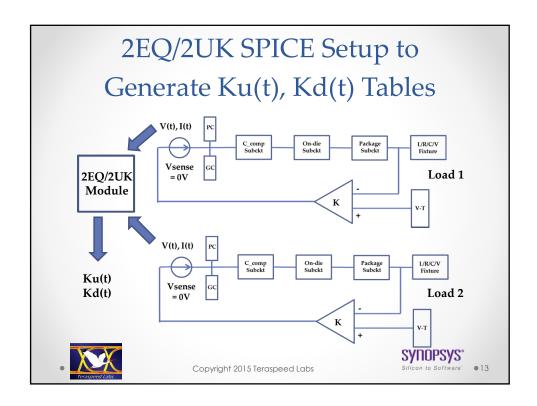

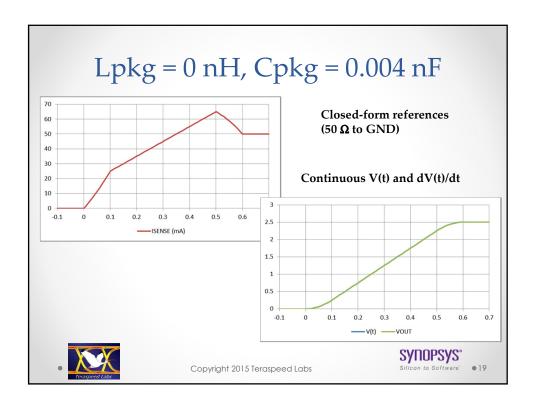

#### Direct V(t), I(t) Solution

- Xuefeng Chen, Asian IBIS Summit (China), September 11, 2007: V(t), I(t) extracted directly for L/R/C/V\_fixture by applying i=C\*dv(t)/dt and v=L\*di(t)/dt

- Extension can include L/R/C\_dut (where L/R/C\_dut replaces the L/R/C\_pin values for the measured pin)

- Ku(t) and Kd(t) tables extracted using the 2equations/2-unknowns (2EQ/2UK) method (later)

SYNOPSYS®

Copyright 2015 Teraspeed Labs

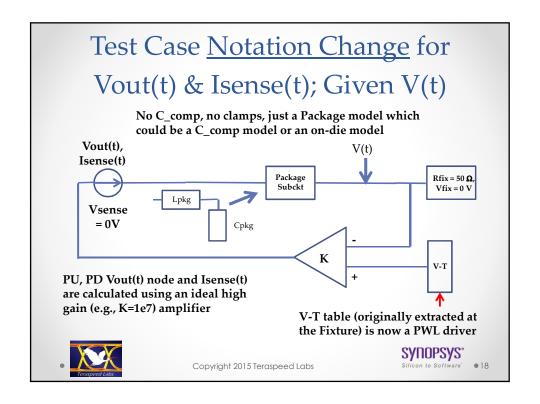

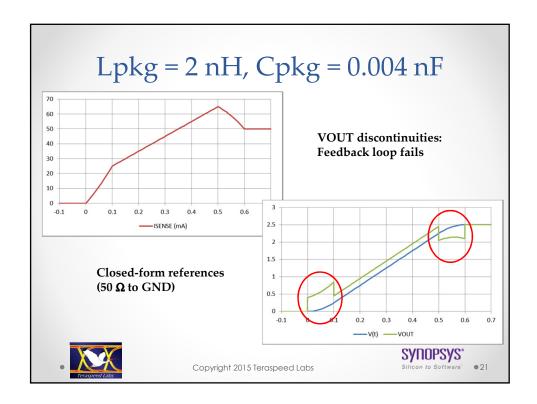

#### **Indirect Feedback Solution Next**

- Avoids encoding equations for complex structures

- Calculates K-tables with high-gain (e.g., 1E7) feedback loop multiplier

- o Kur(t), Kdr(t) from two rising V-T waveforms and fixtures

- Kuf(t), Kdf(t) from two falling V-T waveforms and fixtures

- Calculated and specified responses converge

- Requires vendor-specific SPICEs (versus IBIS-ISS)

- Tables

- Feedback loop issues with tables

Copyright 2015 Teraspeed Labs

07

# Partial SPICE Circuit Showing 2EQ/2UK K-Table Extraction

```

* FEEDBACK TABLE ADJUSTMENT

GDET NDET GND CUR='(I(VDN2)*I(VUP1)-I(VDN1)*I(VUP2))/(1E7)'

VDET NDET GND 0

*

GKUR NKU GND

+ CUR='(V(IN2)-V(PIN2)*I(VDN1)-V(PIN1)*I(VDN2))/I(VDET)'

VKUR NKU GND 0

*

GKDR NKD GND

+ CUR='(V(IN1)-V(PIN1))*I(VUP2)-V(IN2)-V(PIN2)*I(VUP1))/I(VDET)'

VKDR NKD GND 0

Kdr

```

$I_{I}(t) = Ku(t)*Iu(V_{I}(t)) + Kd(t)*Id(V_{I}(t))$

$I_2(t) = Ku(t)*Iu(V_2(t)) + Kd(t)*Id(V_2(t))$

Copyright 2015 Teraspeed Labs

SYNOPSYS\*

Silicon to Software

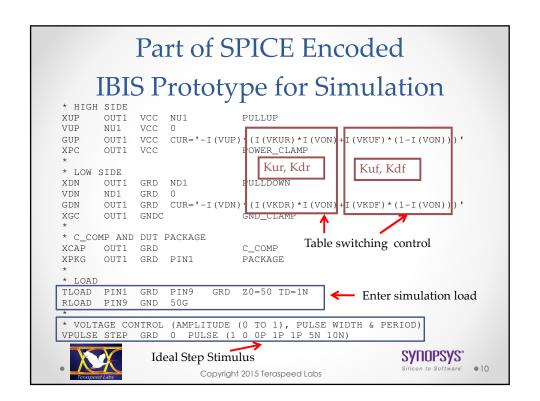

#### SPICE Encoding

- I-V tables: G elements (VCCS)

- V-T tables: PWL voltage sources

- Voltage rails: Entered

- SPICE interpolation

- Allows higher resolution time steps in V-T tables

- o Interpolates G table currents

- I-V and V-T tables extended from final values

- · Convergence criteria adjustable

- K-tables printed for Kur(t), Kdr(t); Kuf(t), Kdf(t)

- Simulation done with K-table drivers:

- G elements for K-tables

- Scaled controlled ramp (1V/nS)

- Step stimuli (0 to 1, 1 to 0)

Copyright 2015 Teraspeed Labs

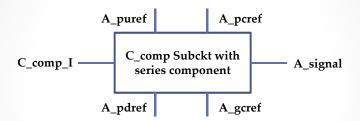

# General Proposed Single-ended C\_comp Subckt Model

- (Notation and details under development)

- C\_comp\_I: If needed for series path

- o Resistance needs to be de-embedded from I-V tables

- A signal: Output

- Extend model for differential connections

Copyright 2015 Teraspeed Labs

SYNOPSYS®

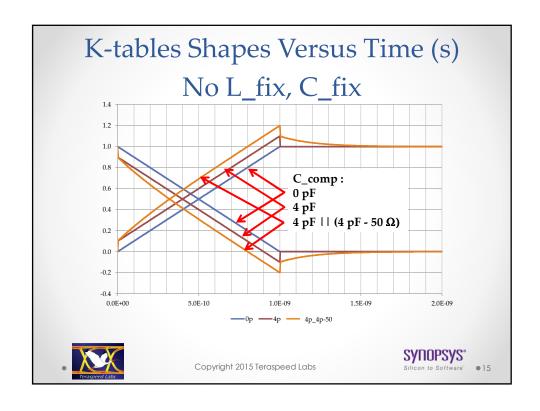

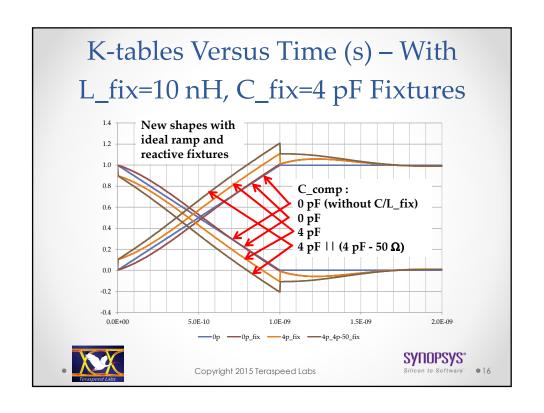

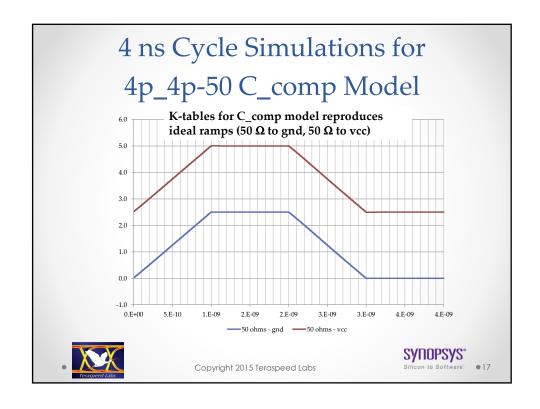

#### **Ideal Ramp Test Cases**

- Reference Waveforms

- $_{\odot}$  1 ns ramp (0% to 100%) into 50  $\Omega$ -to-gnd and 50  $\Omega$ -to-vcc loads

- o 5 V supply

- o 2 ns duration

- C\_comp cases

- 0 pF

4 pF

4 pF | (4p)

4 pF | (4pF 50 Ω)

(4p\_4p-50)

- Pullup/Pulldown I-V tables

- $\circ$  50  $\Omega$  straight lines

- 1001 point extractions (not critical)

Copyright 2015 Teraspeed Labs

SYNOPSYS®

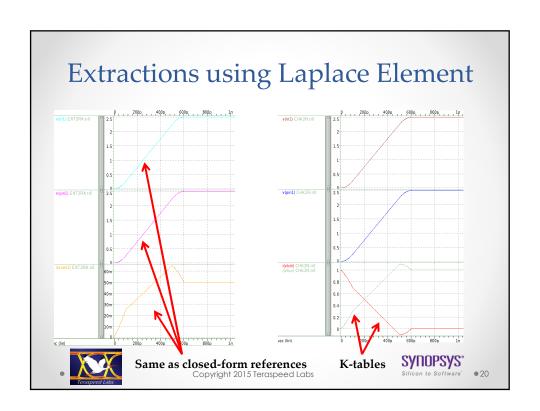

#### **Observations and Conclusions**

- Result accuracy

- K-table extraction insensitive to K=1e5 to K=1e9 feedback multipliers

- Requires SPICE maximum accuracy settings

- Not sensitive to number of extraction points

- Severe test cases

- Sharp waveform derivative discontinuity in ideal ramp

- Large C\_comp model load can be used

- Large L\_fixture, C\_fixture reactive loads are ok

- BOTH L\_pkg, and C\_pkg do not converge (even with smooth waveforms) – therefore topology limited and must use tooldependent methods

- o Fails for T-line models (delay in feedback loop)

- Works for S-parameter, Laplace transform, lumped models

Copyright 2015 Teraspeed Labs

SYNOPSYS®

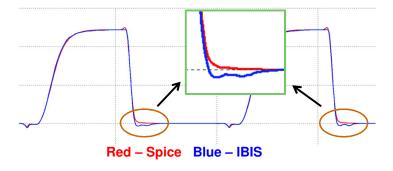

# IBIS Simulation Case Study: Unexpected Glitch and Using C\_fixture

Lance Wang Asian IBIS Summit Shanghai, China Nov. 9<sup>th</sup>, 2015

#### Outline

- Motivation

- Unexpected glitch issue in the IBIS simulation

- · Seeking for solutions

- Case study and solutions

- · The root cause of glitch issue

- · Possible solutions

- Using C\_fixture in IBIS V-T curves

- Conclusions

© 2006-2015 IO Methodology Inc.

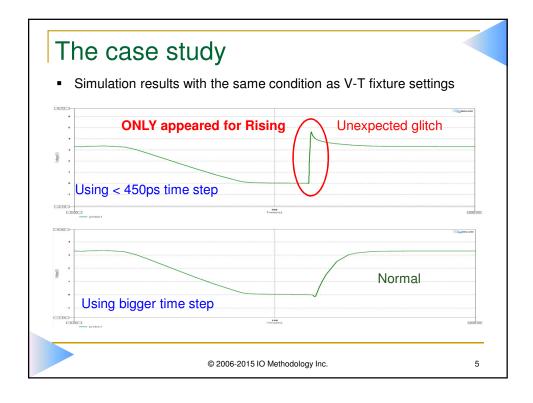

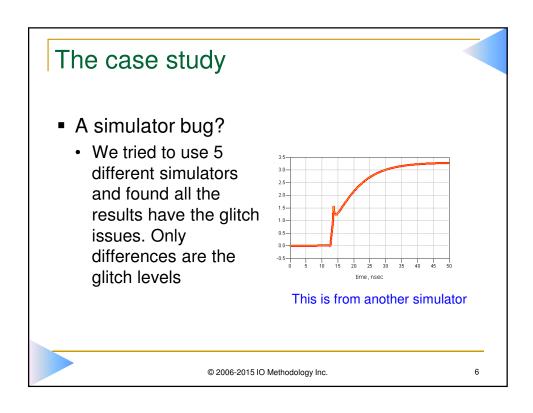

#### Motivation

- An unexpected glitch found when doing an IBIS model validation (transient analysis simulations)

- An unexpected glitch found when we used < 450ps time step setting (called resolution setting in some EDA tools)

- Everything is correct when we used bigger time step in the simulations

- Want to find out the root cause of this issue and solutions

© 2006-2015 IO Methodology Inc.

3

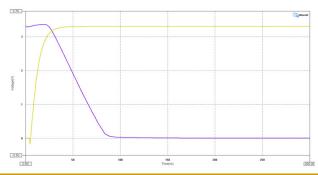

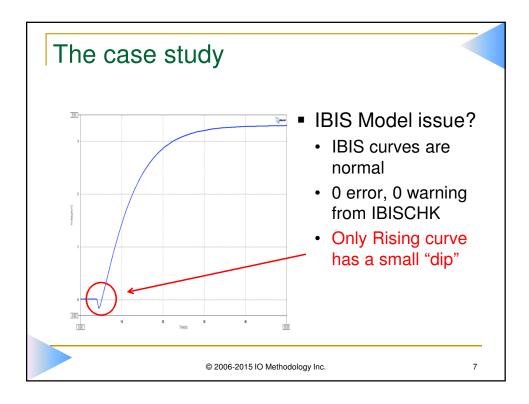

#### The case study

- IBIS buffer model

- This is normal I<sup>2</sup>C pad buffer (Open Drain type)

- It is relatively low speed buffer

- About 60ns for rising and 300ns for falling to be settled with 4.7K ohm load and 3.3v to pull up

© 2006-2015 IO Methodology Inc.

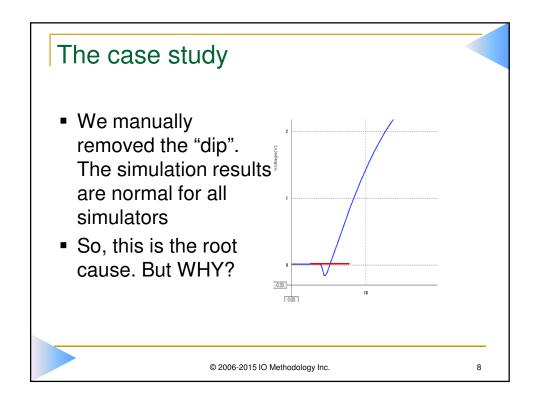

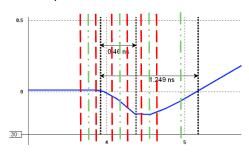

#### The root cause

Simulator works fine when the time step is bigger than the "dip down" period. It produces only 1 or 0 step in the "dip down" region. It would be "skipped" when it leads to a wrong direction

Simulator got confused when the time step is less than the "dip down" period when it produces 2 or more steps in the "dip down" region. It leads to a wrong direction without any information from I-V curves

The "dip" width is about 1.25ns. The dip down period is about 460ps.

© 2006-2015 IO Methodology Inc.

9

#### Solutions

- Using large time step size in transient analysis

- It could lead to an inaccurate result

- The setting needs to be manually forced. A dynamic step setting feature might not work.

- Manually remove the "dip" area in IBIS Model

- Adding C\_fixture to reduce or make the "dip" area "lighter" or to disappear

- This method leads to another discussion topic in this presentation

© 2006-2015 IO Methodology Inc.

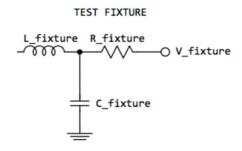

### C\_fixture setting in IBIS V-T section

- C\_fixture optionally can be used in IBIS V-T waveforms

- We normally do not recommend using C\_fixture in V-T curves

© 2006-2015 IO Methodology Inc.

11

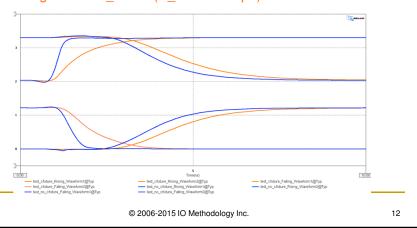

#### C\_fixture test case

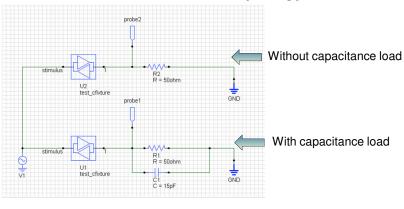

- We used the same Spice netlist to create 2 IBIS Models.

All settings are the same except C\_fixture

- Blue without C\_fixture (C\_fixture = 0)

- Orange with C\_fixture (C\_fixture = 15pF)

#### C\_fixture test case

Use both Models with this topology

© 2006-2015 IO Methodology Inc.

13

#### C\_fixture test case

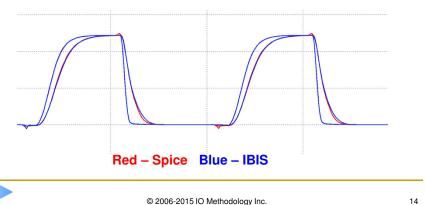

Both cases correlate well with Spice simulations for C\_fixture=0 IBIS Model

#### C\_fixture test case

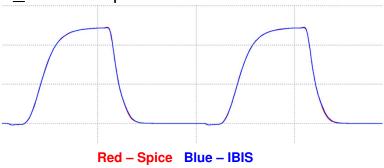

The result from the load with capacitance correlates well with Spice simulations for C\_fixture=15pF IBIS Model

© 2006-2015 IO Methodology Inc.

15

#### C\_fixture test case

The slight difference in results from the load without capacitance for C\_fixture=15pF IBIS Model

© 2006-2015 IO Methodology Inc.

#### C\_fixture test case

- C fixture can be used in IBIS V-T curves

- Simulators need to use a de-capacitance algorithm when C\_fixture is present in the V-T curves. C\_fixture may reduce simulation accuracy

- It is better that IBIS V-T curves only have resistance load (linear load)

© 2006-2015 IO Methodology Inc.

17

#### Supporting C\_fixture in simulations

■ This is a surprise!

# 3 out of 6 major simulators don't support C\_fixture in IBIS Model. It got ignored!

© 2006-2015 IO Methodology Inc.

#### Summary

- In some simulations for a slow IBIS model, we found unexpected glitch in the result

- It is due to a "dip down" area and it could be solved by using larger time step size (resolution value)

- The "dip down" period could be removed manually or use C fixture to reduce "dip down" area (size)

- Be careful when using C fixture

- · It might cause some inaccurate simulation results

- Some simulators do not support C\_fixture in IBIS model

- · Recommend using linear load for V-T curves in IBIS model.

© 2006-2015 IO Methodology Inc.

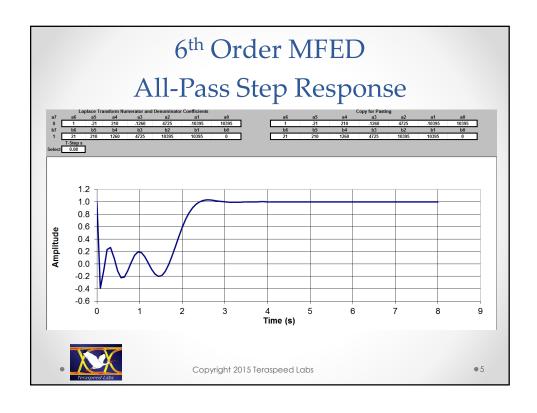

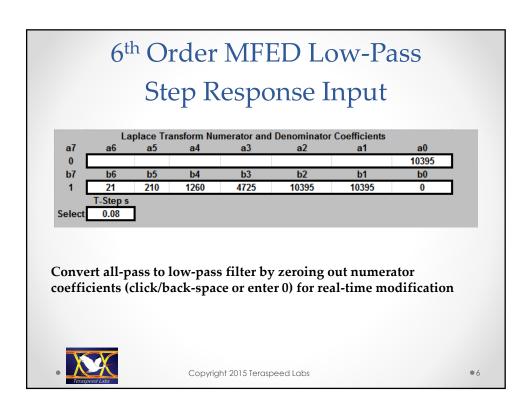

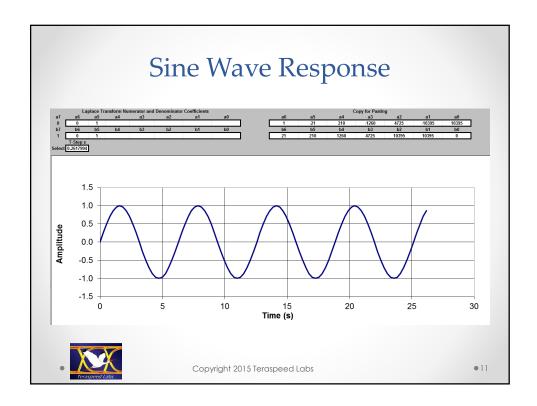

#### Laplace Transform Time Response Utility

Bob Ross, Teraspeed Labs bob@teraspeedlabs.com

Asian IBIS Summit Shanghai, China November 9, 2015

(Presented by Anders Ekholm, Ericsson) Originally presented May 13, 2015

Copyright 2015 Teraspeed Labs

.

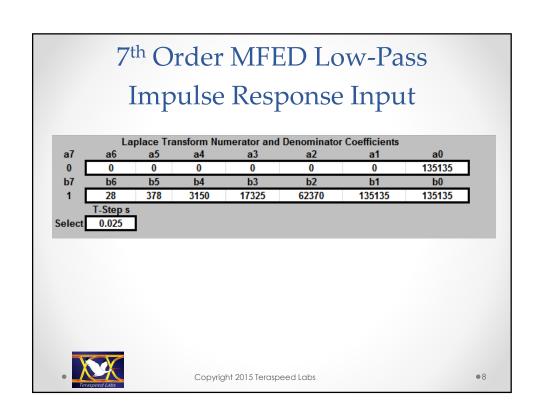

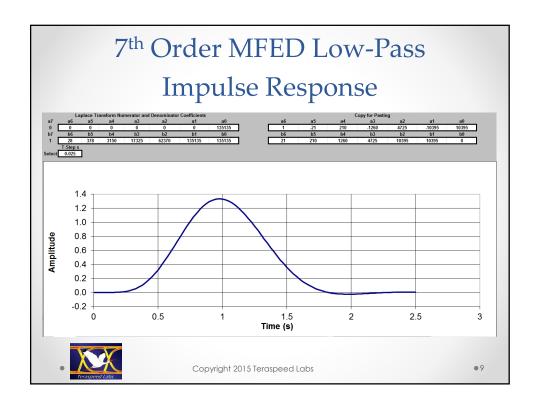

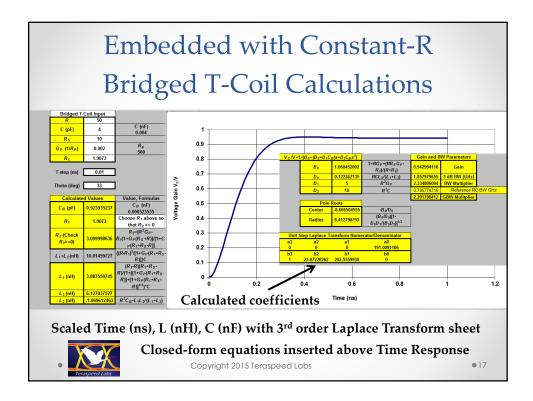

#### Some Applications

- Show step and impulse response for network analysis

- Show step and impulse response for lower-order, reduced order (or pole-zero) Touchstone formulations in IBIS-AMI analysis

- Embed for time-response displays in analysis applications by inserting calculations at top

Copyright 2015 Teraspeed Labs

#### Notation and Introduction

Laplace Transform

$$X(s) = \frac{a_{n-1}s^{n-1} + \dots + a_0}{s^n + b_{n-1}s^{n-1} + \dots + b_0},$$

**Differential Equation**

$$x^{n}(t) + b_{n-1}x^{n-1}(t) + \dots + b_{0}x(t) = 0$$

initial conditions,  $x(0), \dots, x^{n-1}(0)$ ,

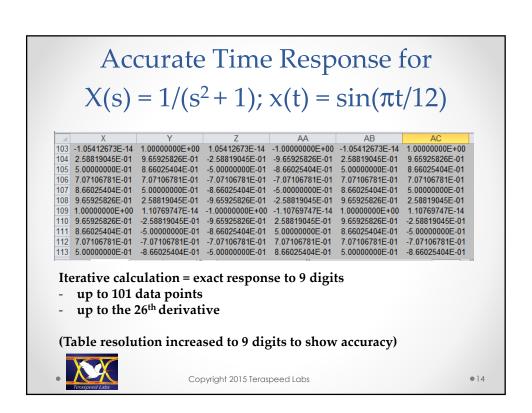

Utility calculates and displays immediately 101 points for  $x^i(t)$ , i=0 to i=26 for the time response and all of its derivatives

Extended for more time points by copying and pasting last row

Can be used as an embedded utility involving other Laplace Transform calculations

Copyright 2015 Teraspeed Labs

•3

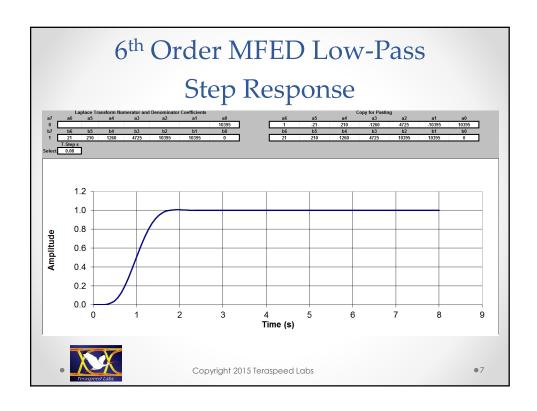

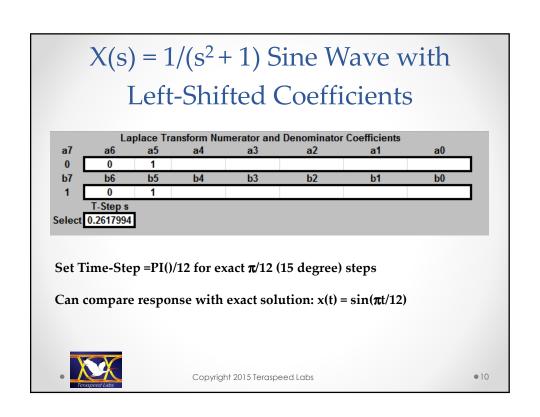

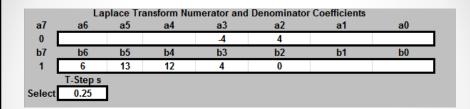

# Enter Laplace Transform Num. and Den. Coefficients and Time-Step

|        | La               | place Tra | ınsform Nuı | merator and | Denominator | Coefficients |       |

|--------|------------------|-----------|-------------|-------------|-------------|--------------|-------|

| a7     | a6               | a5        | a4          | a3          | a2          | a1           | a0    |

| 0      | 1                | -21       | 210         | -1260       | 4725        | -10395       | 10395 |

| b7     | <b>b</b> 6       | b5        | b4          | b3          | b2          | b1           | b0    |

| 1      | 21               | 210       | 1260        | 4725        | 10395       | 10395        | 0     |

| Select | T-Step s<br>0.08 | ]         |             |             |             |              |       |

Step Response of  $6^{th}$  order Bessel (maximally flat envelope delay, MFED) all-pass function

Change time-step to zoom-in or zoom-out and to change resolution

The graph auto-scales over 101 points

Copyright 2015 Teraspeed Labs

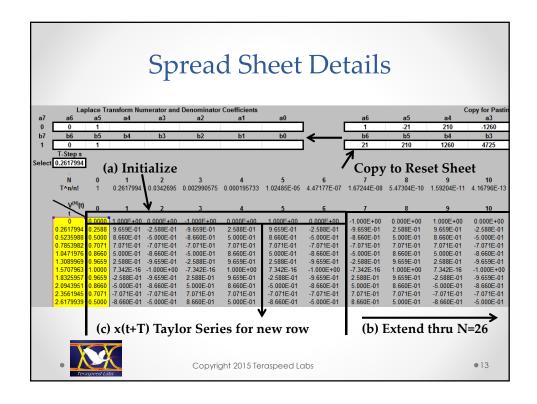

# Recursive Taylor Series Method (Repeat b and c)

a) Initialize:

$$i = 1, ..., n-1$$

(n = 7)

$x(0) = a_{n-1}$   $x^{i}(0) = a_{n-1-i} \cdot \sum_{j=0}^{i-1} b_{n-i-j} x^{j}(0)$

b) Extend:

$$i = n, ..., p$$

(p = 26)  $x^{i}(t) = -\sum_{j=0}^{n-1} b_{j} x^{i-n-j}(t)$

c) Next time step: i = 0, ..., n-1 (Taylor Series)

$$x^{i}(t+T) = \sum_{j=i}^{p} x^{j}(t) \frac{T^{j-i}}{(j-i)!}$$

R. I. Ross, "Evaluating the Transient Response of a Network Function," *Proc. IEEE*, vol.55, pp. 615-616, May 1967

Copyright 2015 Teraspeed Labs

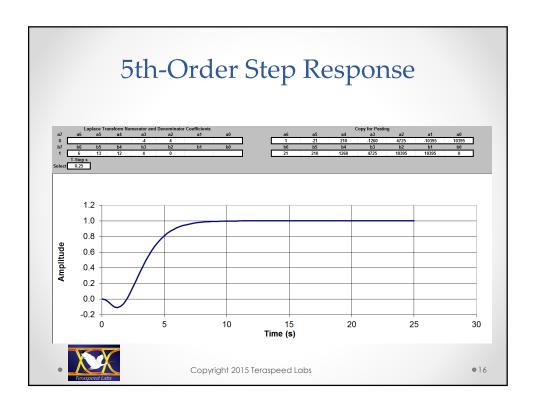

#### 5<sup>th</sup>-order Step Response

$$X(s) = 4(-s+1)/[(s+1)^2(s+2)^2s] = (-4s+4)/(s^5+6s^4+13s^3+12s^2+4s)$$

Laplace transform is normalized ( $b_7 = 1$ ) Left-shift the numerator and denominator coefficients Step response means  $b_2$  is 0 Right-hand plane zero creates pre-shoot

Copyright 2015 Teraspeed Labs

#### Guidance

- Normalize coefficients (highest order denominator coefficient set to 1)

- <u>Scale coefficients</u> so that values are meaningful for time-steps between 0.01 and 1 (because of Taylor Series expansion)

- Left-shift the entries for lower-order functions

- Change time-step to zoom-in or zoom-out

- Get numerical values from spread sheet

- Copy and paste last row to extend spread sheet for more time rows (also adjust display range)

Copyright 2015 Teraspeed Labs

#### **Final Remarks**

- Works with real, complex, multiple roots, pole-zero canceled roots, and right-hand plane zeros

- Response fast even though spread-sheet implementation is based on inefficient storage

- Recursive routine (slide 11) can be done <u>in-place</u> for better storage efficiency in other programming applications

- Display shows changes as coefficients are modified

- Display diverges if Laplace Transform close-form response diverges

Copyright 2015 Teraspeed Labs

•19

## IBIS Summit Downloads and References

- www.ibis.org/summits/nov15a/

- o ross2.xls (time-response utility)

- ross2.pdf (this presentation for instructions, examples)

- www.ibis.org/summits/may11/

- ross3.pdf, "Continuous and Discrete Modeling for IBIS-AMI" (gives theoretical background for both differential and difference equations)

- ross2.pdf, "T-Coils and Bridged-T Networks" (gives general T-coil derivations)

Copyright 2015 Teraspeed Labs