# Inconsistency of EBD (Electrical Board Description) specification in DDR3 DIMM

Asian IBIS Summit Yokohama, Japan November 20, 2014

Shogo Fujimori Fujitsu Advanced Technologies s.fujimori@jp.fujitsu.com

IBIS Promotion Working Group EC Center / JEITA

1 All Rights Reserved, Copyright © 2014 JEITA

**1. IBIS EBD Model** 2. Problems in DDR3 DIMM Differential termination AC termination **3.** Proposal 4. Summary

# 1. IBIS EBD Model

- Electrical Board Description

- The electrical connectivity of a Board level component - PCB

- Components

- User visible pins

IBIS Version 6.0

• Example: DIMM

#### 8 ELECTRICAL BOARD DESCRIPTION INTRODUCTION

A "board level component" is the generic term to be used to describe a printed circuit board (PCB) or substrate which can contain components or even other boards, and which can connect to another board through a set of user visible pins. The electrical connectivity of such a board level component is referred to as an "Electrical Board Description". For example, a SIMM module is a board level component that is used to attach several DRAM components on the PCB to another board through edge connector pins. An electrical board description file (a .ebd file) is defined to describe the connections of a board level component between the board pins and its components on the board.

# 1. IBIS EBD Model

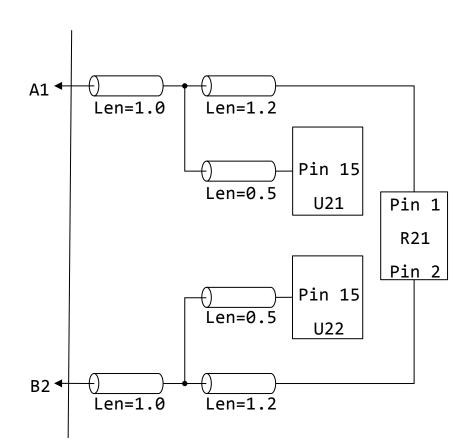

• Example

```

[Path Description] Example

Pin Al

Len = 1.0 \text{ L}=6.0 \text{ C}=2.0 \text{ p} /

Fork

Len = 0.5 L = 1.0n C = 2.0p /

Node U21.15

Endfork

Len = 1.2 L=6.0n C=2.0p /

Node R21.1

Node R21.2

Len = 1.2 L=6.0n C=2.0p /

Fork

Len = 0.5 L = 1.0n C = 2.0p /

Node U22.15

Endfork

Len = 1.0 L = 6.0n C = 2.0p /

Pin B2

```

# 1. IBIS EBD Model

# • Example

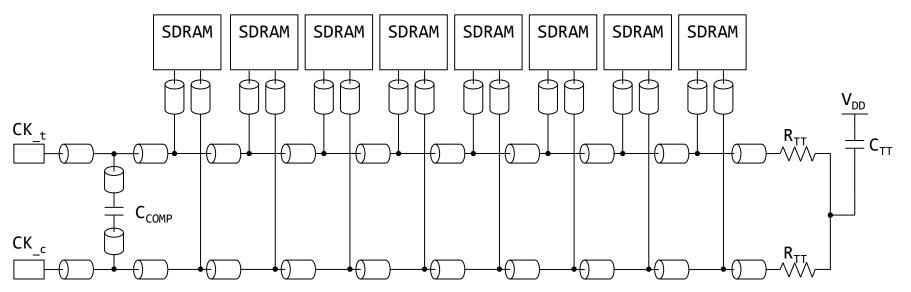

# 2. Problem in DDR3 DIMM

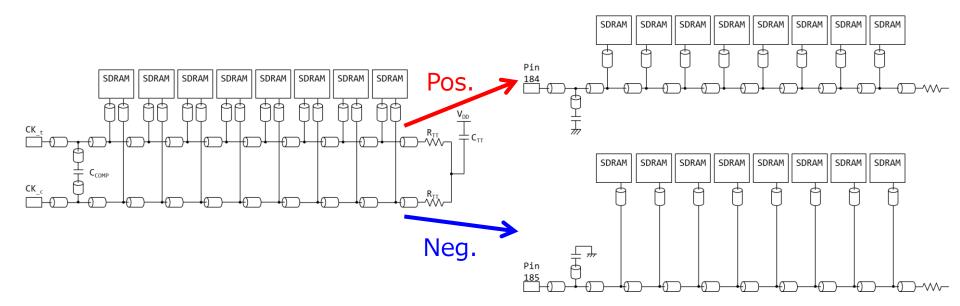

# • DDR3 Clock Net (Fly-by)

# • Problems of EBD

1 Differential termination

② AC termination

③ Differential lines Coupling

This presentation

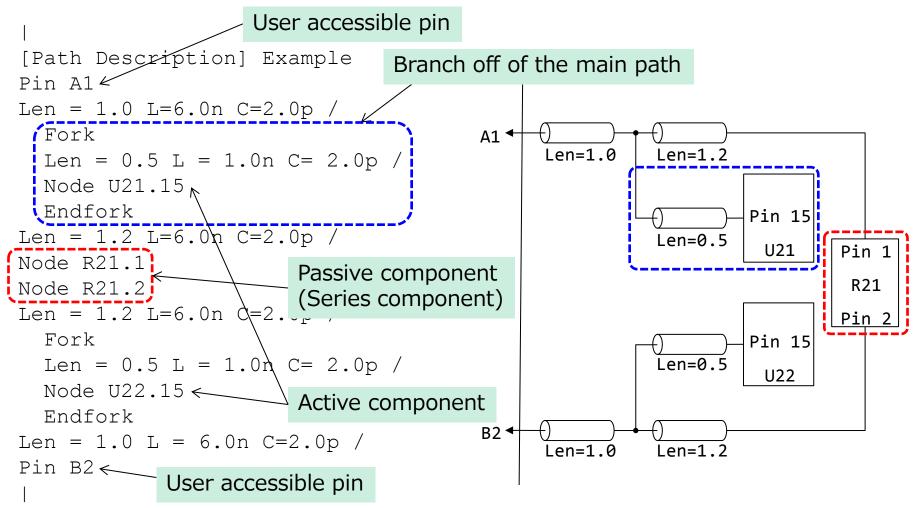

### 2.1 Differential termination

- Description styles of differential terminations are vendor dependent

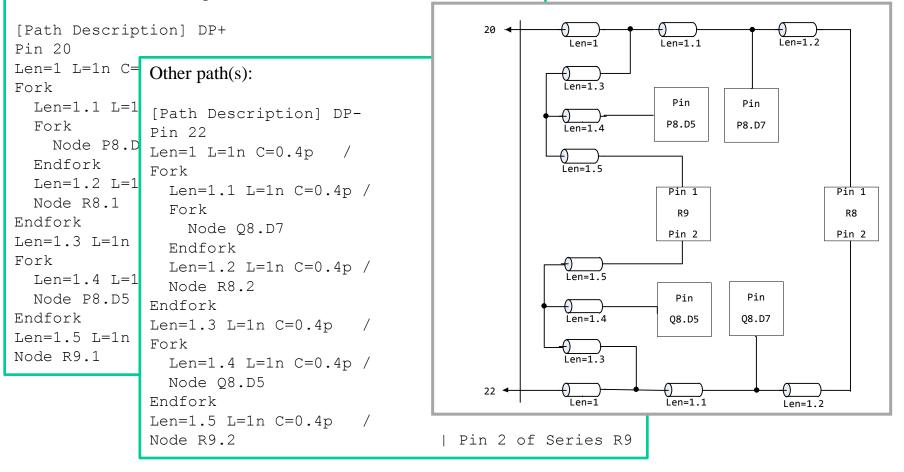

- Case1: A single [Path Description] including differential pair nets

- Case2: Two separate [Path Description]s for each differential pair nets. (See below figure)

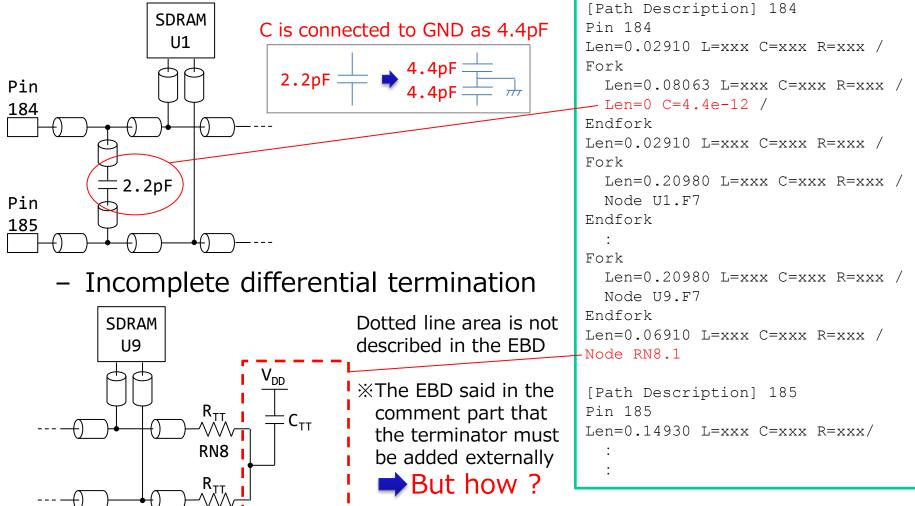

#### Problem case of differential termination

- Problem case of two separate [Path Description]s

- Two paths are completely separated

# Problem case of differential termination (Cont'd)

- Background of the problem

- Until IBIS 5.0, a series component can not connect two separate [Path Description]s

Quoted from IBIS 5.0 specification

Connecting two separate [Path Description]s with a series component is not allowed.

- It was allowed later IBIS 5.1

- The problem will be solved in the future

- However, check IBIS Version your EDA tool can use

Quoted from IBIS 5.1 specification

It is also allowed to insert a series component between two branches of a single [Path Description], or even between two separate [Path Description]s (see the examples below).

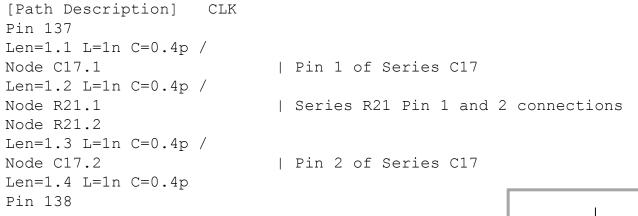

#### **Example described in IBIS specification**

• Example of A [Path Description] including a differential pair nets (Quoted from IBIS 5.1 specification)

A path including series passive components (C17, R21) between branches forming a differential termination:

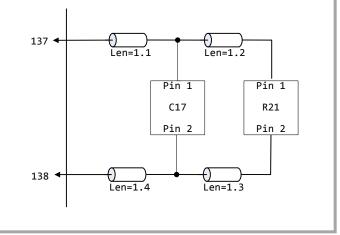

# Example described in IBIS specification (Cont'd)

• Example of two separate [Path Description]s connected by series component (Quoted from IBIS 5.1 specification)

Two paths connected by series resistors (R8, R9) used as differential termination between components:

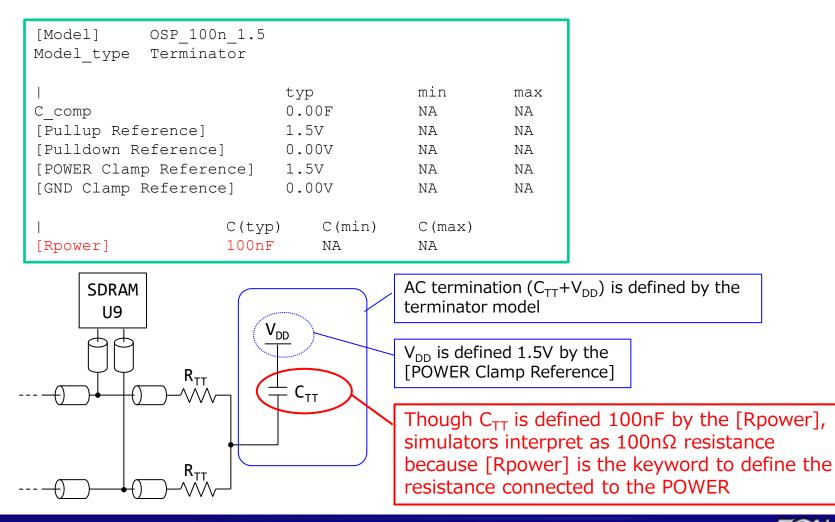

#### 2.2 AC termination

- Problem case of AC termination

- The capacitor is interpreted as  $100n\Omega$  resistance

# 2.2 AC termination (Cont'd)

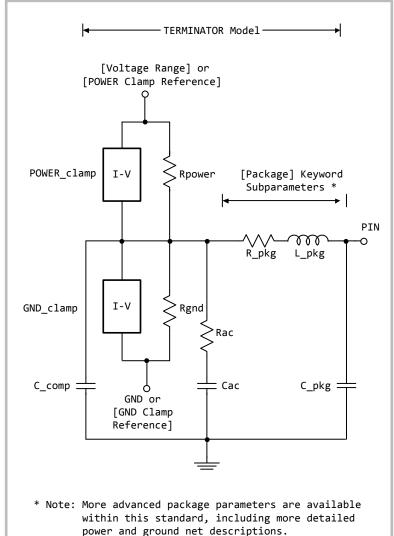

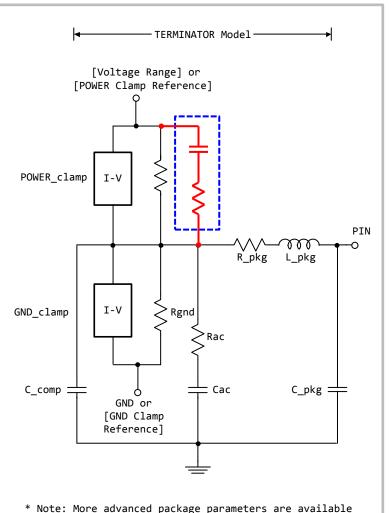

- Background of the problem

- IBIS Terminator Model can not define AC termination connected to the POWER

Quoted from IBIS specification

#### 3. Proposal

- Adding a keyword to connect to the POWER to EBD or Terminator model

- Adding a "Power" keyword to EBD model

- e.g. Connected to 1.5V ideal voltage source

```

Fork

Len=2.100402 L=xxx C=xxx R=xxx/

Node U1.F7

Endfork

Len=88.011076 L=xxx C=xxx R=xxx/

Node CTT.2

Node CTT.1

Power 1.5

```

Adding a keyword of AC termination connected to the POWER to Terminator model

within this standard, including more detailed

power and ground net descriptions.

#### 4. Summary

- There are several problems of EBD model to use DDR3 DIMM Simulation

- Check details of the IBIS EBD model you got

- Edit simulation models if necessary

- Check IBIS Version your EDA tool can use

- Proposal and Expecting for IBIS

- Adding a keyword to connect the AC termination to the POWER

- Adding the EBD section to IBIS Cookbook

- IBIS Promotion Working Group provide any IBIS related information, and proposal to the IBIS specification

#### Reference

- "IBIS (I/O Buffer Information Specification) Version 6.0", IBIS Open Forum 2013

- "IBIS (I/O Buffer Information Specification) Version 5.1", IBIS Open Forum 2012

- "IBIS (I/O Buffer Information Specification) Version 5.0", IBIS Open Forum 2008

- "IBIS EBD for DDR2/DDR3 Module Board", Lance Wang (IO Methodology), 2009 IBIS Summit, DesignCon