#### WELCOME FROM MICHAEL MIRMAK, INTEL CORPORATION

On behalf of the I/O Buffer Information Specification (IBIS) Committee, I would like to welcome you to this Asian IBIS Summit, our fifth in Taiwan. We are delighted to see continued interest in our IBIS summits, and hope that these events have now become an autumn "tradition" for the IBIS community here.

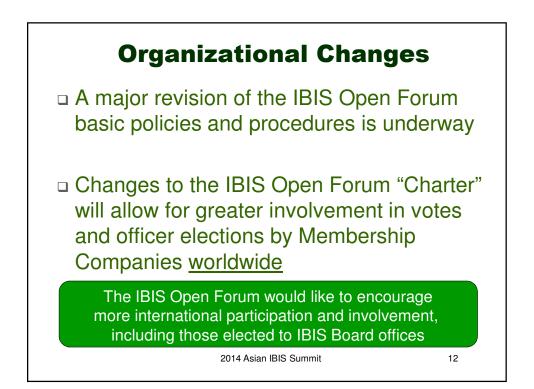

IBIS itself recently celebrated the 15<sup>th</sup> year of being an international standard under the International Electrotechnical Commission (IEC). Our growth worldwide and our long history present us with challenges and opportunities. We are challenged daily in maintaining the stability of IBIS across versions while offering new features and supporting the latest technologies. You can see this most clearly in recent IBIS-AMI updates for advanced buffer designs as well as our work in improving IBIS support of modern interconnects.

Our greatest opportunity is the ability to hear from you, the IBIS community. Through these Summits and our online conversations, we are able to understand your needs and work together to ensure IBIS meets them. We encourage you to provide feedback both on our specifications and on how we can interact with you better.

We are especially grateful to our sponsors ANSYS, Cadence Design Systems, Intel Corporation, IO Methodology, and Synopsys for making this Summit possible.. We encourage you to express your thanks to them for their support of IBIS.

As always, we wish you success and hope that you will find the presentations and discussions beneficial and enjoyable.

Sincerely,

Michael Mirmak Chair, IBIS Committee

#### WELCOME FROM MICHAEL MIRMAK, INTEL CORPORATION

首先我僅代表 IBIS 委員會, 歡迎您來到這次亞洲 IBIS 峰會, 今年是我們在台灣 的第五次會議。我們很高興看到我們的 IBIS 峰會被持續關注, 並希望這個會議現 在能成為一個秋天的"傳統"節目。

IBIS 標準本身成為國際電子技術委員會(IEC)的國際標準已有的 15 個年頭了 。我們在全球的增長和我們悠久的歷史為我們提供了機遇和挑戰。在維持 IBIS 跨 版本的穩定性,同時提供新的功能,並支持最新的技術方面我們每天都面臨著挑戰 。您可以從最近為先進的緩衝設計的 IBIS-AMI 更新,以及我們在改善 IBIS 支持現 代互連器件的工作可以清楚地看到這一點。

我們最大的機遇是您對 IBIS 社區的支持。通過這些峰會和我們的在線交談,我 們能夠理解您的需求,我們要共同努力,確保 IBIS 滿足需求。我們鼓勵您對我們 的規范以及如何更好的互動給予反饋。

我們要特別感謝我們的贊助商 ANSYS, Cadence,英特爾公司, IO Methodology 和 Synopsys 使這次峰會可能。我們感謝他們對 IBIS 支持。

一如以往,我們祝你成功,並希望你能發現演講和討論對您有益。

此致 馬夢寬 IBIS 委員會主席

### AGENDA AND ORDER OF THE PRESENTATIONS

## (The actual agenda might be modified)

|                | IBIS SUMMIT MEETING AGENDA                                                                                                                                                                   |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8:15           | SIGN IN<br>- Vendor Tables Open at 8:30                                                                                                                                                      |

| 9:00           | Welcome<br>- Michael Mirmak<br>(Chair IBIS Open Forum, Intel Corporation, USA)                                                                                                               |

| 9:10           | Activities and Direction of IBIS                                                                                                                                                             |

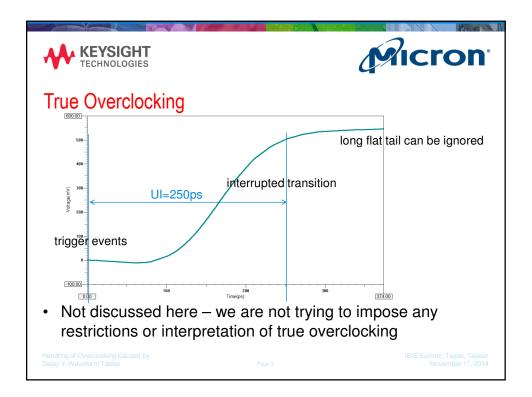

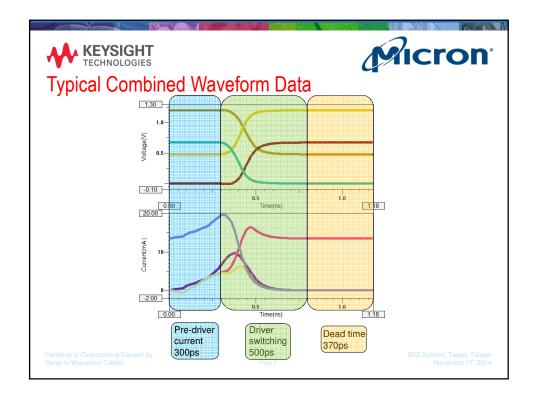

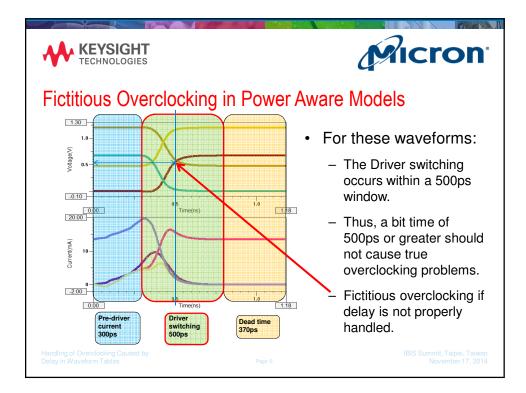

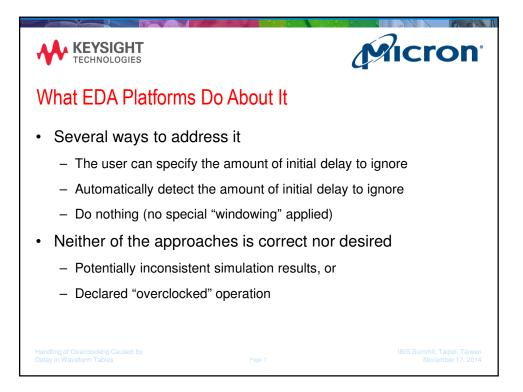

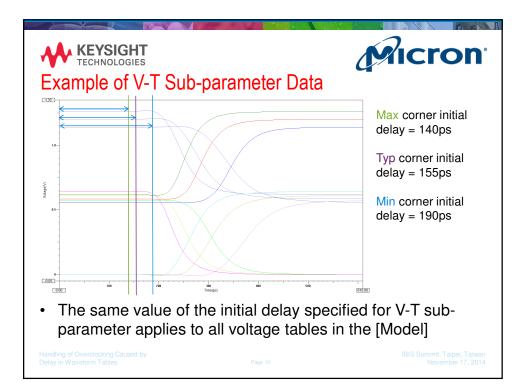

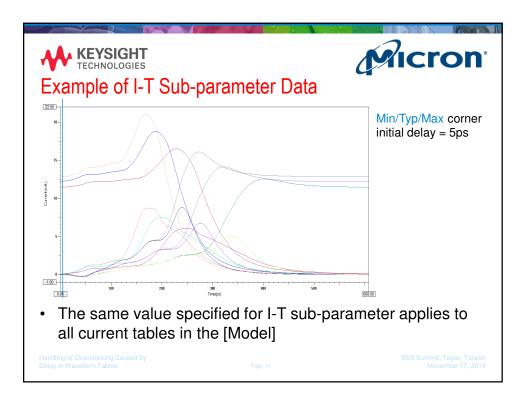

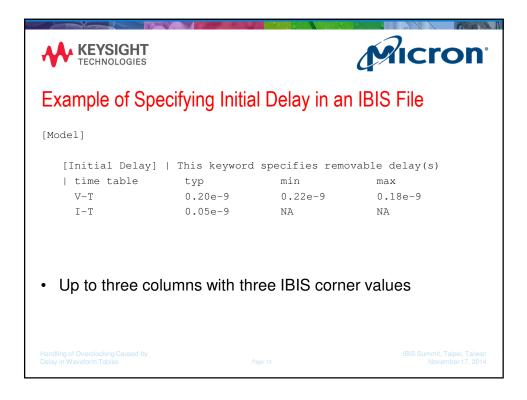

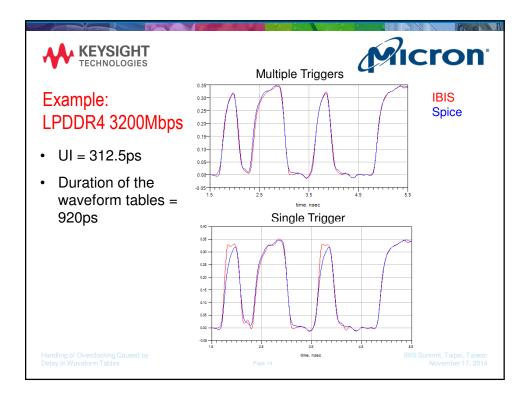

| 9:35           | <pre>Handling of Overclocking Caused by Delay in Waveform Tables 12 Radek Biernacki*, Ming Yan*, Randy Wolff** Justin Butterfield** (*Keysight Technologies, **Micron Technology, USA)</pre> |

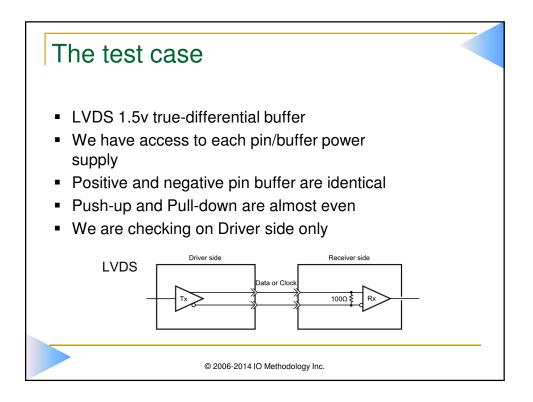

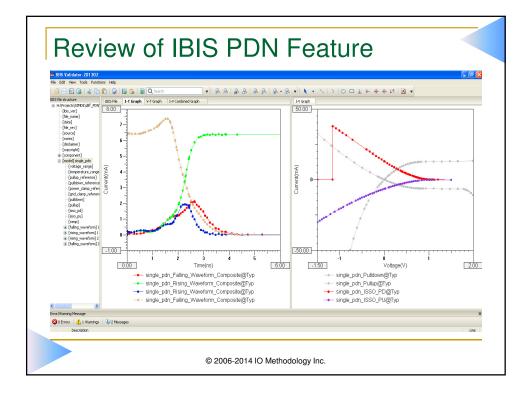

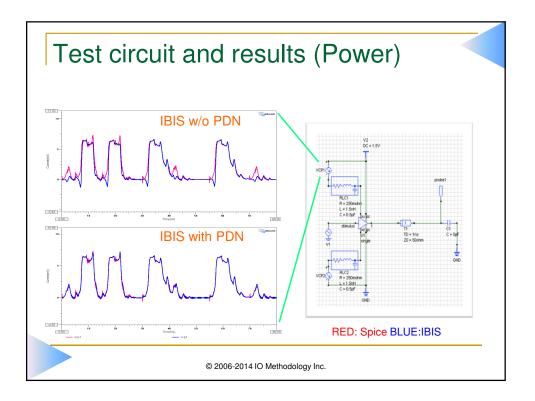

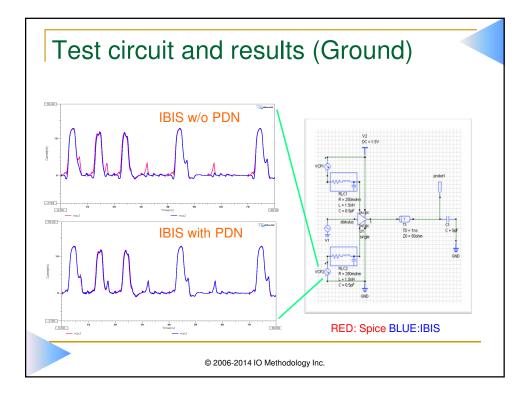

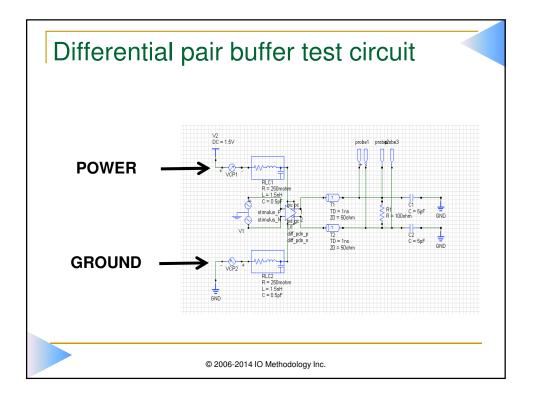

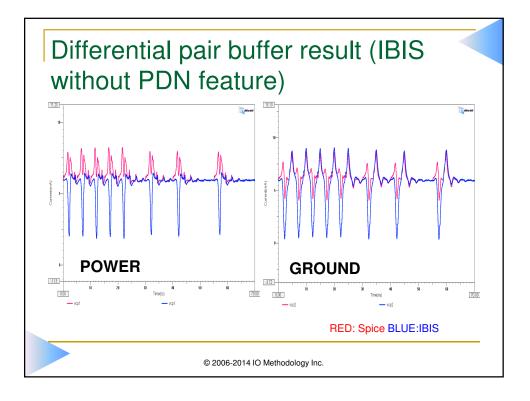

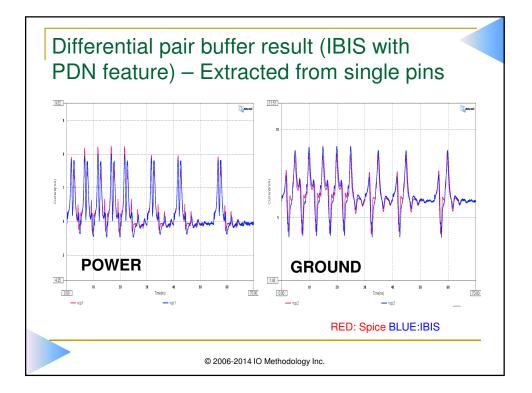

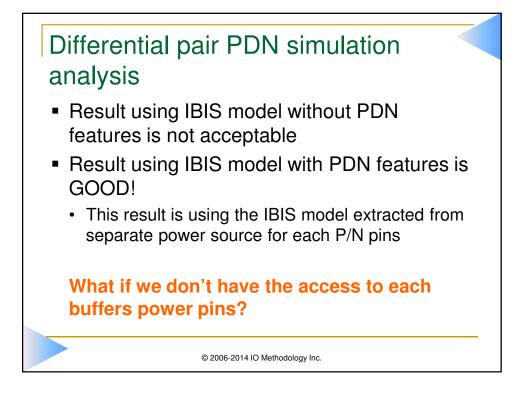

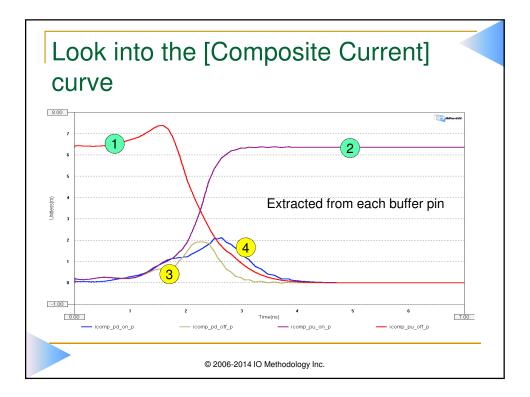

| 10:05          | Differential Buffer Using IBIS Models for PDN Simulations 20<br>Lance Wang (IO Methodology, USA)                                                                                             |

| 10:35          | BREAK (Refreshments and Vendor Tables)                                                                                                                                                       |

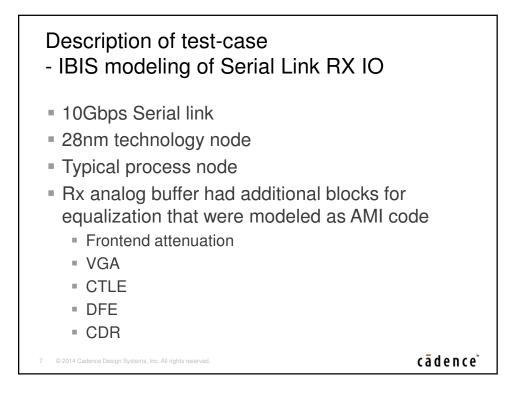

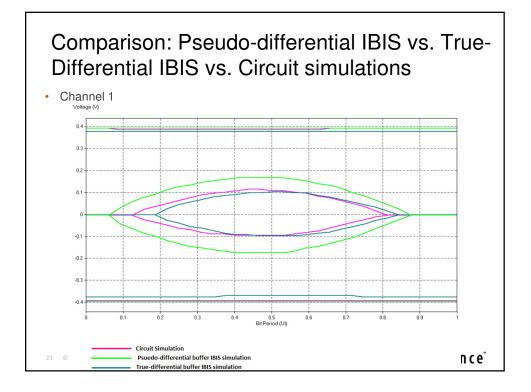

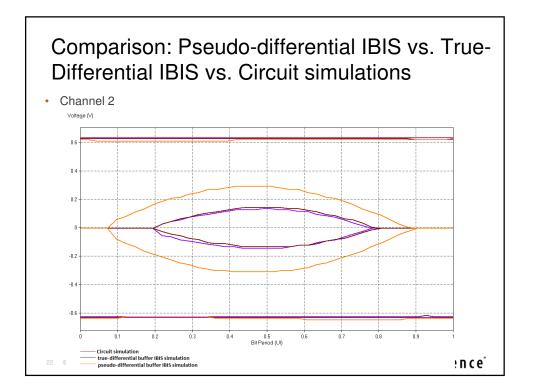

| 10 <b>:</b> 55 | <pre>True Differential IBIS Model for SerDes Analog Buffer 29 Shivani Sharma, Tushar Malik, Taranjit Kukal (Cadence Design Systems, India)</pre>                                             |

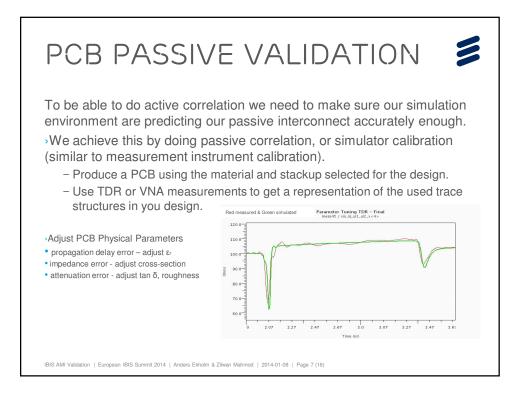

| 11:30          | IBIS AMI Validation                                                                                                                                                                          |

| 12:00          | FREE BUFFET LUNCH (Hosted by Sponsors)<br>- Vendor Tables                                                                                                                                    |

# AGENDA AND ORDER OF THE PRESENTATIONS (Continued)

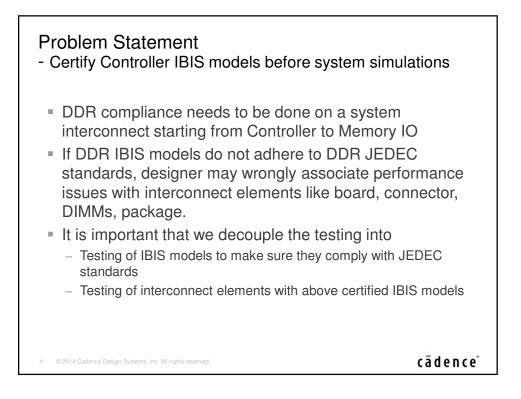

| Signing IBIS Model Against DDR4 Spec                 |

|------------------------------------------------------|

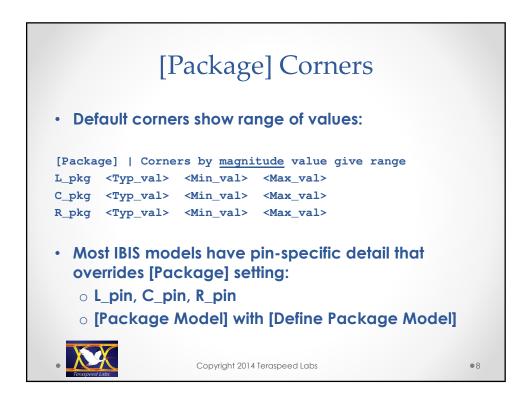

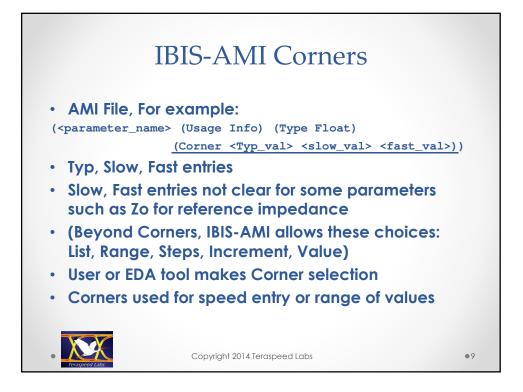

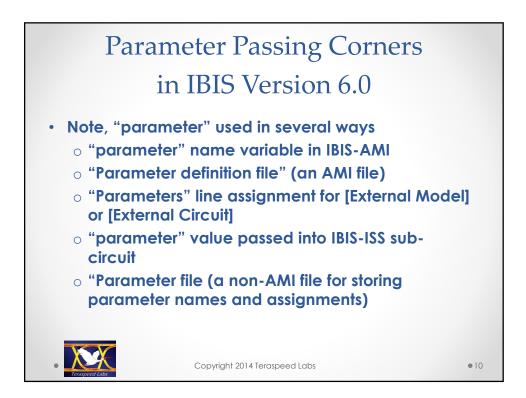

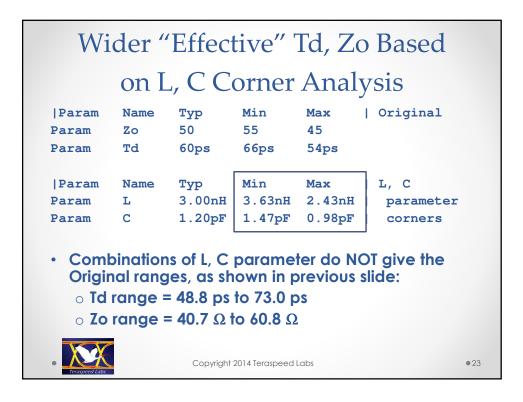

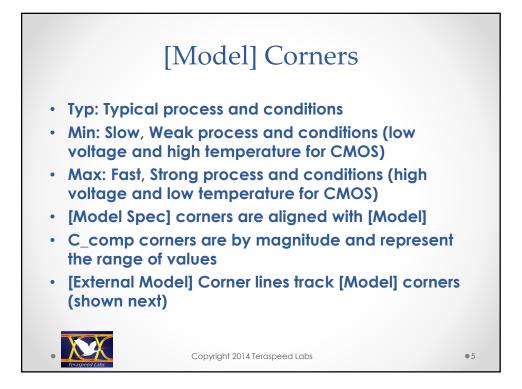

| Corner Considerations                                |

| BREAK (Refreshments and Vendor Tables)               |

| Best Practices for High-Speed Serial Link Simulation |

| Discussion                                           |

| CONCLUDING ITEMS                                     |

| END OF IBIS SUMMIT MEETING                           |

|                                                      |

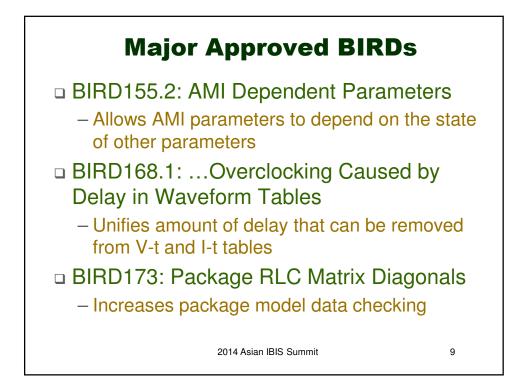

# **UPCOMING CHANGES**

2014 Asian IBIS Summit

7

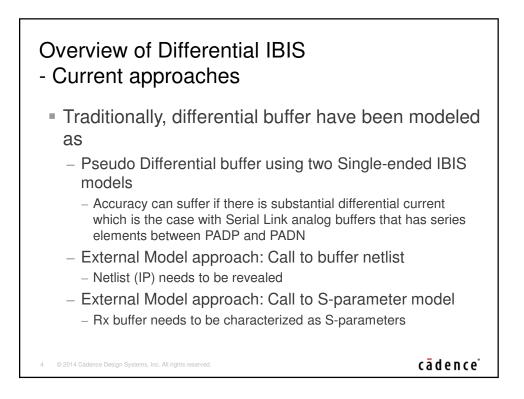

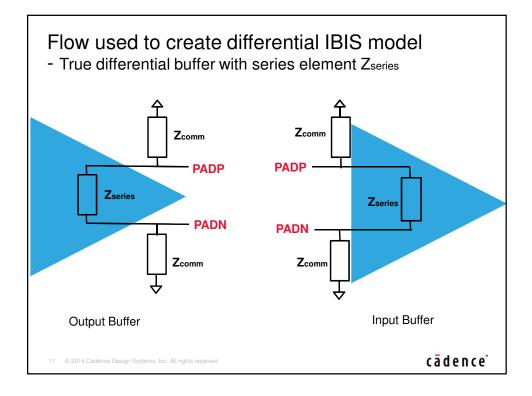

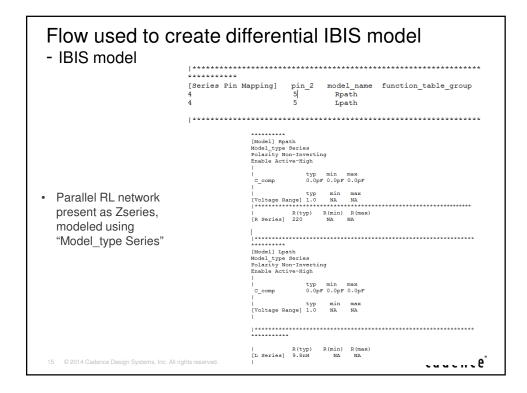

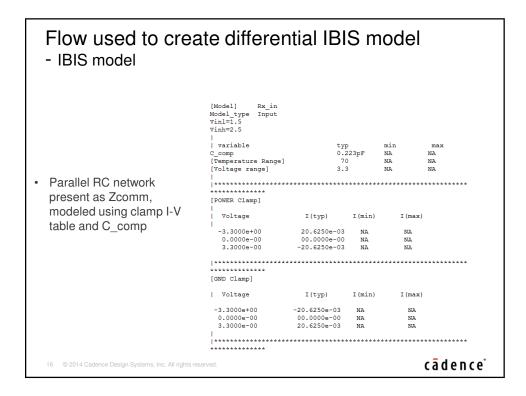

- While S-parameter approach is best suited for analog buffers in serial links, we provide an alternate way to model it through standard IBIS tabular format with use of series elements to model differential current.

- This extends the approach suggested in IBIS cookbook that suggests modeling of differential current using series Resistance.

- Here we propose use of reactive elements (R/L/C) to model differential current.

5 © 2014 Cadence Design Systems, Inc. All rights reserved

cādence°

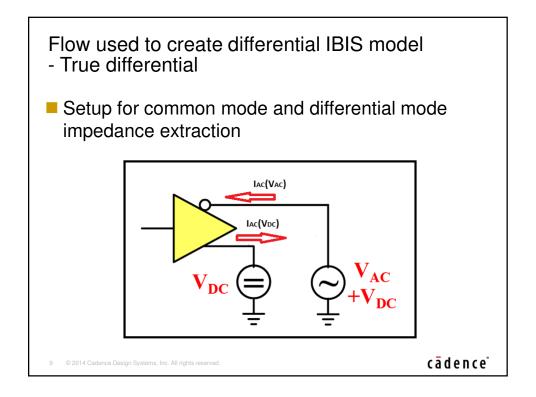

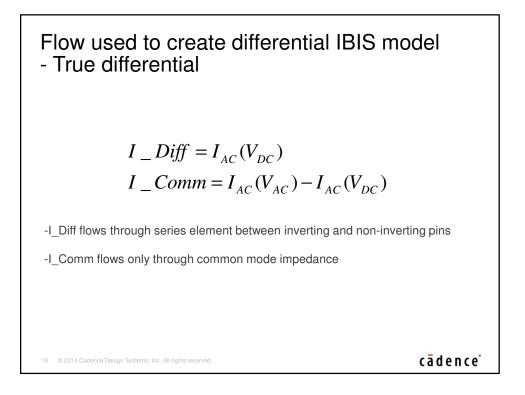

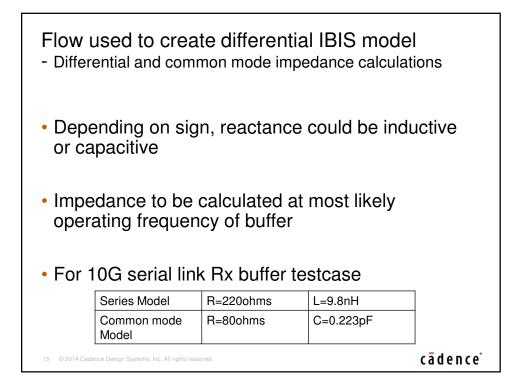

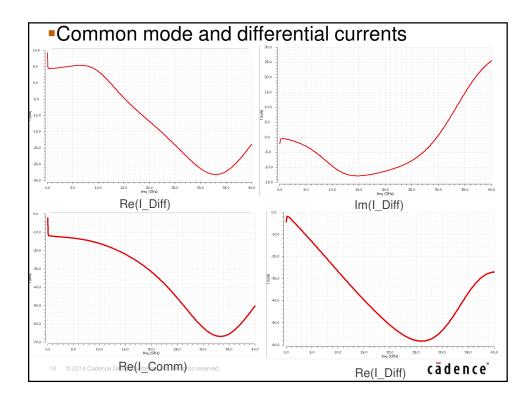

Flow used to create differential IBIS model• Differential and common mode impedance calculations• Series Reactance = $X_{series} = \frac{V_{AC}}{\ln(I \_ Diff)}$ • Series Resistance = $R_{series} = \frac{V_{AC}}{Re(I \_ Diff)}$ • Common mode Resistance = $R_a = \frac{V_{AC}}{Re(I \_ Comm)}$ • Common mode Reactance = $X_a = \frac{V_{AC}}{\ln(I \_ Comm)}$

| Units                    |  |  |  |

|--------------------------|--|--|--|

|                          |  |  |  |

| -                        |  |  |  |

| ns                       |  |  |  |

| tbd –(Definition tbd) ps |  |  |  |

| tCK(av                   |  |  |  |

| +<br>ot                  |  |  |  |

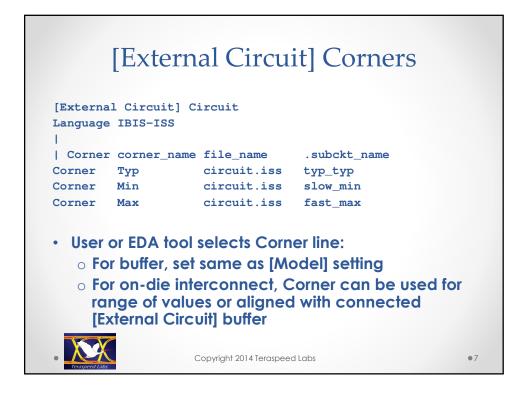

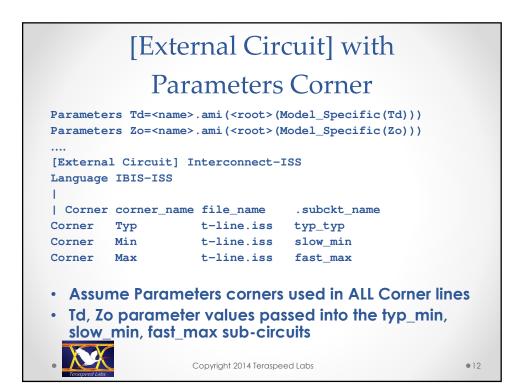

|              | [Extern       | al Mod                     | el] Corners               | 5      |

|--------------|---------------|----------------------------|---------------------------|--------|

| [External    | l Model] Bufi | fer                        |                           |        |

| Language     | IBIS-ISS      |                            |                           |        |

| <br>  Corper | corner name   | file_name                  | .subckt name              |        |

| Corner       | Typ           | buffer.iss                 | —                         |        |

| Corner       | Min           | buffer.iss                 |                           |        |

| Corner       | Max           | buffer.iss                 | fast_max                  |        |

|              | el] corner s  | is under [M<br>election de | odel]<br>termines which ( | Corner |

|              |               | Copyright 2014 Teraspe     |                           |        |