## WELCOME FROM MICHAEL MIRMAK, INTEL CORPORATION

On behalf of the I/O Buffer Information Specification (IBIS) Open Forum, I would like to welcome our presenters and guests to the Asian IBIS Summit in Shanghai.

This year, we celebrate our ninth annual IBIS Summit in the People's Republic. Since the first summit in China, four separate revisions of the IBIS specification have been released. The Open Forum is lucky to have a solid nine-year history of working alongside our friends and colleagues in the People's Republic to improve IBIS. We are thankful for your help and for another challenging technical program this year.

We are especially grateful to our sponsors Huawei Technologies, Agilent Technologies, ANSYS, Cadence Design Systems, Intel Corporation, IO Methodology Inc., Synopsys, and Teledyne LeCroy for making this Summit possible.

Our thanks to you for participating and best wishes for a successful summit!

Sincerely,

马梦宽 Michael Mirmak Chair, IBIS Open Forum

我仅代表 I / O 缓冲信息规范(IBIS)开放论坛,欢迎我们的嘉宾来参加在上海举行的亚洲 IBIS 峰会。

今年是在中华人民共和国举行的第九个年度的 IBIS 峰会。在这九年中,我们已推出了四个 IBIS 更新版本。IBIS 开放论坛非常幸运的能和大家一起来进行技术更新的工作。我们也感谢有机会在中华人民共和国再次和我们的朋友和同仁一起研讨更深入的技术方案。

我们要特别感谢我们的赞助商华为技术有限公司,安捷伦科技公司,ANSYS,Cadence Design Systems,IO Methodology,英特尔公司, Synopsys 公司 和 Teledyne LeCroy, 他们使本次峰会成为可能。

感谢您的参与并预祝会议圆满成功!

马梦宽 主席,IBIS 开放论坛

## WELCOME FROM LI JINJUN, HUAWEI TECHNOLOGIES

Ladies and Gentleman,

On behalf of Huawei Technologies, welcome to the eighth annual Asian IBIS Summit (China). I would like to express my appreciation to IBIS Open Forum and all the sponsors for co-organizing this event.

Since 2005, IBIS Asian Summit in China has been the top-level international conference in high speed digital design society in China. I am looking forward to work with IBIS members in China, and to expand our participations in the region.

Huawei has actively involved in all IBIS society's events. We hope to resolve high speed link issues with IBIS Open Forum, EDA vendors and IC vendors. Your comments and suggestions will be deeply appreciated!

Welcome all of you to Shanghai! Hope you will enjoy all the technical discussions and sharing throughout the meeting, and have a nice journey!

Thank you! Li Jinjun Huawei Technologies

各位专家,各位来宾:

我代表华为公司,欢迎大家来参加第8届亚洲 IBIS 技术研讨会,衷心地感谢 IBIS 协会组织本次会议。

自从 2005 年以来,IBIS 技术研讨会已经成为了中国高速设计领域的一次盛会。我 很高兴有机会与 IBIS 协会一起促进和扩大在该领域的分享。

华为积极参与各项 IBIS 活动,希望与 IBIS 协会、EDA 软件、芯片公司一道来共同解决许多高速链路设计上的挑战,欢迎大家会上讨论和建议。

欢迎 IBIS 专家来到上海,希望你们能够喜欢所有的技术讨论和会议分享,度过美好一天。

谢谢大家 华为公司 厉进军

## AGENDA AND ORDER OF THE PRESENTATIONS

## (The actual agenda might be modified)

|       | IBIS SUMMIT MEETING AGENDA                                                                                                         |

|-------|------------------------------------------------------------------------------------------------------------------------------------|

| 8:15  | SIGN IN - Vendor Tables Open at 8:30                                                                                               |

| 8:45  | <pre>Welcome - Li, JinJun   (Huawei Technologies, China) - Wang, Lance   (Vice-Chair, IBIS Open Forum, IO Methodology, USA)</pre>  |

| 9:00  | <pre>Introducing IBIS 6.0</pre>                                                                                                    |

| 9:30  | IBIS Summary Documents                                                                                                             |

| 10:00 | More on IBIS Modeling for Load-Dependent Current-Mode                                                                              |

| 10:30 | BREAK (Refreshments and Vendor Tables)                                                                                             |

| 10:50 | Combined I-V Table Checking Problem                                                                                                |

| 11:20 | An Advanced Behavioral Buffer Model With Over-Clocking Solution 32 Sun, YingXin and Chen, Raymond Y. (Cadence Design Systems, USA) |

| 12:00 | FREE BUFFET LUNCH (Hosted by Sponsors) - Vendor Tables                                                                             |

## AGENDA AND ORDER OF THE PRESENTATIONS (Continued)

| 13:30 | When Could PCB and PKG PDN Lumped Loop be Extracted Separately? 4 Xu, ZhenRong (Huawei Technologies, China)                                                                       | 4  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

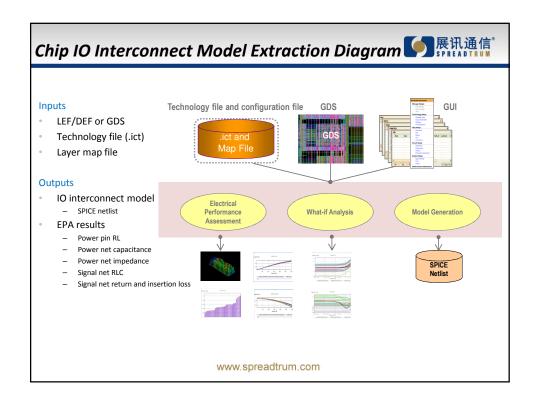

| 14:00 | DDRn Interface Signoff Analysis with Distributed Chip IO 5 Interconnect Model Guo, Steven*; Qin, ZuLi**; and Zhong, ZhangMin** (*Spreadtrum and **Cadence Design Systems, China)  | 50 |

| 14:45 | IBIS Model for IO-SSO Analysis                                                                                                                                                    | 55 |

| 15:20 | BREAK (Refreshments and Vendor Tables)                                                                                                                                            |    |

| 15:40 | Modeling, Extracting and Verification of VCSEL Model for                                                                                                                          | 7  |

| 16:10 | Adaptive Crosstalk Cancellation Block for SERDES and its AMI 8 Implementation Kukal, Taranjit#; Sharma, Shivani#; and Zhong, ZhangMin## (Cadence Design Systems, #India, ##China) | }5 |

| 16:50 | Anisotropic Substrate for IBIS-AMI Simulation                                                                                                                                     | 96 |

| 17:20 | Concluding Items                                                                                                                                                                  |    |

| 17:30 | END OF IBIS SUMMIT MEETING                                                                                                                                                        |    |

## **Introducing IBIS 6.0**

Michael Mirmak Intel Corp. Chair, IBIS Open Forum

Asian IBIS Summit Shanghai, People's Republic of China November 15, 2013

http://www.eda.org/ibis/

2013 Asian IBIS Summit

## **Agenda**

- > IBIS 6.0 in Summary

- Key Features

- Changes from IBIS 5.1

- > What problems does 6.0 address?

- > Issues to Resolve

- What's Next?

- > Questions

2013 Asian IBIS Summit

## **Key Features of IBIS 6.0**

- > IBIS 6.0 was approved September 20, 2013

- http://www.eda.org/ibis/ver6.0/

- Major additions focus on IBIS-AMI

- Adds redriver and retimer support

- Expands jitter/noise parameters

- Clarifies analog buffer impedance descriptions

- Supports IBIS-ISS (Interconnect SPICE Subcircuits) and Touchstone 1.x/2.0

2013 Asian IBIS Summit

3

## **Other Changes from IBIS 5.1**

- Clarifications of A/D and D/A converters in [External Model] and [External Circuit]

- Parameter passing now supported!

- Additional files supported for IBIS-AMI

- Including explicit paths

- Identifiers for individual IBIS-AMI model instances

- List Tips for IBIS-AMI Lists

- Associates labels with parameter lists

- Improved organization of the document

- Easier to read and use

2013 Asian IBIS Summit

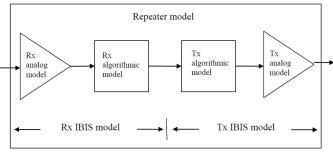

## **IBIS 6.0 Support Examples** How do I model a mid-bus repeater? - Recall the repeater types: retimers and redrivers - Think of redriver as filtering and/or amplifying analog signals - Think of retimer as using clock-data recovery to re-transmit data Redriver RX TX **Device Device** (filter) (amp) Retimer **RX Device** 10101... TX **Device** CDR) 2013 Asian IBIS Summit 5

## **IBIS 6.0 Support Examples**

- > How do I model a mid-bus repeater?

- Use [Repeater Pin] to identify RX and TX pins

- Define "Redriver" or "Retimer" in the .ami parameters file under "Repeater Type"

- For Retimers, ensure AMI\_GetWave is defined and included

from the IBIS 6.0 specification

2013 Asian IBIS Summit

## **IBIS 6.0 Support Examples**

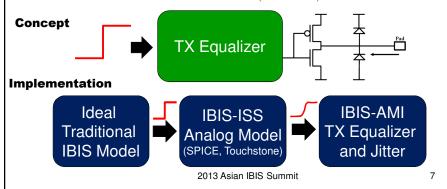

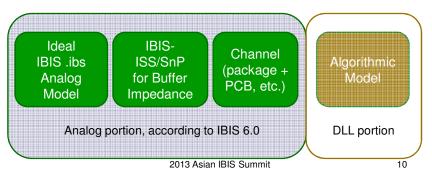

- > Where to "put" the analog impedance of the buffer?

- What if I can't easily represent the analog behavior of my buffer using traditional IBIS?

- In 6.0, use IBIS-ISS to represent complex analog buffer behavior

- Traditional IBIS becomes ideal (TX or RX)

## **IBIS 6.0 Support Examples**

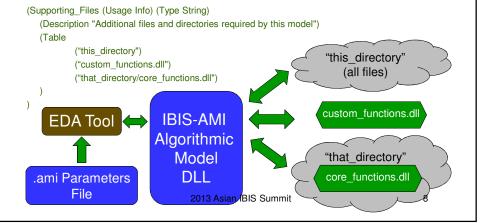

- > What if your algorithmic model isn't a single file?

- Multiple files, in different locations, now supported

- From the .ami parameters file...

## **Issues to Resolve**

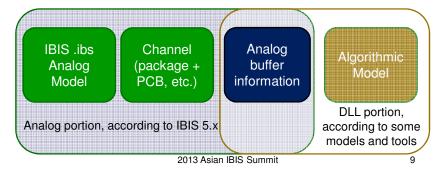

- > Ensuring true IBIS-AMI model compatibility

- Some models under IBIS 5.x place buffer analog information in the executable (DLL or SO file)

- This may be a problem for some tools

- Use of IBIS 6.0 improved analog modeling can help ensure portability

## **Issues to Resolve**

- Ensuring true IBIS-AMI model compatibility

- Some models under IBIS 5.x place buffer analog information in the executable (DLL or SO file)

- This may be a problem for some tools

- Use of IBIS 6.0 improved analog modeling can help ensure portability

## **Issues to Resolve**

- > Improving IBIS packages

- Two separate approaches being discussed

- Objective is to finalize a package model format that...

- > Can interact with IBIS and related files

- Supports time- and frequency-domain modeling data in IBIS-ISS format

- > Supports arbitrary numbers of crosstalking signal lines in individual segments

- Target is to include this in the next major IBIS release

2013 Asian IBIS Summit

11

## What's Next?

- A parser: IBISCHK6

- Check new keyword syntax

- Check new IBIS-AMI parameter syntax

- Simple checks for IBIS-AMI DLL/SO executables?

- > Are the required IBIS-AMI functions present?

- > Do the functions execute (instead of crashing)?

- Is a parser for IBIS-ISS required?

- SPICE features used in IBIS-ISS are very common across EDA tools

- > IBIS version updates

- IBIS continues to target updates twice per year

2013 Asian IBIS Summit

## **IBIS Summary Documents**

Bob Ross

Asian IBIS Summit, Shanghai, China

November 15, 2013

bob@teraspeed.com

(presented by Anders Ekholm, Ericsson)

Page I

© 2013 Teraspeed Consulting Group LLC

## **Document Samples**

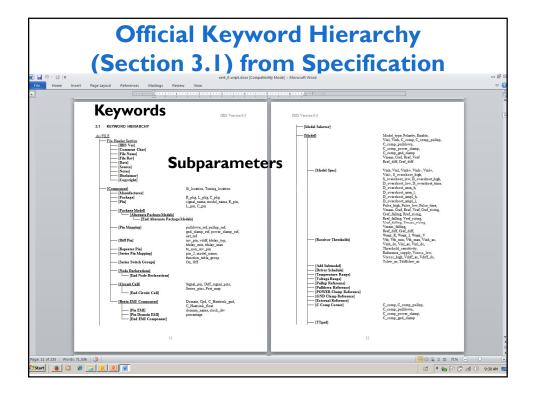

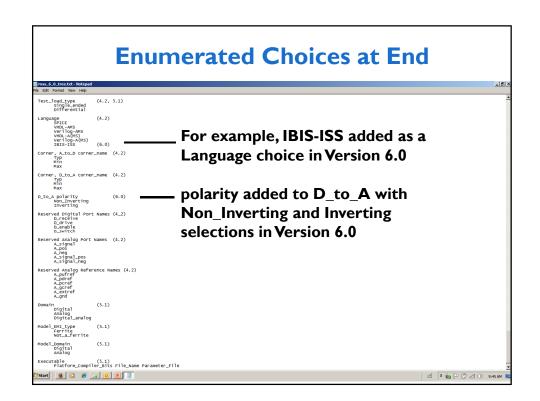

- Keyword Hierarchy tree in IBIS Version 6.0, Section 3.1

- Expanded Keyword Hierarchy tree

- Evolution document

- IBIS-AMI parameter tables in IBIS Version 6.0, Section 10.7

- These documents summarize the IBIS elements

TERASPEED CONSULTING GROUP

Page 2

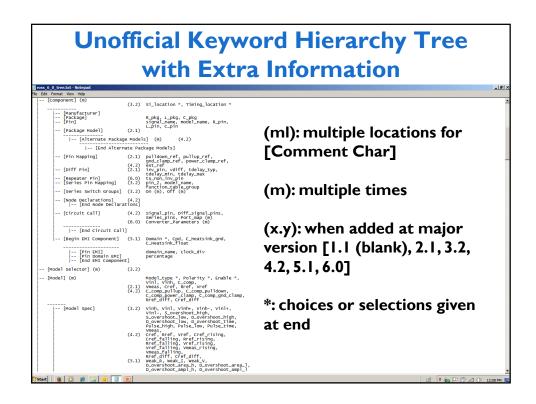

# **Unofficial Keyword Hierarchy Updated from September, 2007**

- Keyword Hierarchy tree

- 165 distinct keyword usages

- Some keywords are re-used in different contexts (e.g., [IBIS Ver], [End], [Rising Waveform], etc. and in .ibs, .pkg and .ebd files)

- Hierarchy documents updated with Version

5.1 and Version 6.0 information

Page 4

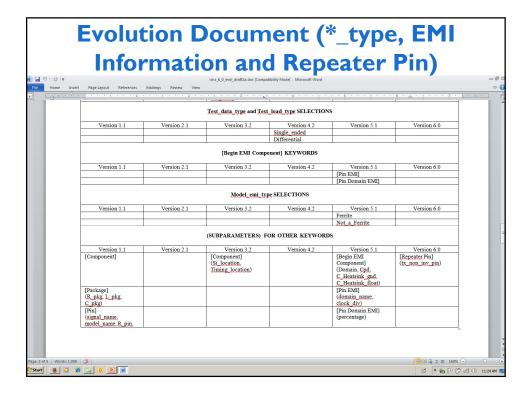

## **Unofficial Evolution Document**

- Evolution document features:

- Updated columns show major version evolution

- Rules and changes evolution

- Significant subparameter selections such as the \*\_type subparameter choices

- Hierarchy and Evolution documents contain overlapping information, but expanded Hierarchy document has more detail

- Sample page shown next

TERASPEED CONSULTING GROUP

Page 7

# IBIS-AMI .ami File Parameter Syntax (Section 10.3)

```

(<parameter_name>

(Usage <usage>)

| required

| required

(Type <data_type>)

({Format} <data_format> <data>) | required *

(List_Tip)

optional with ({Format} List)

| optional or illegal *

(Default <value>)

(Description <string>)

| optional

* Value or Default, but not both, and other rules

TERASPEED

CONSULTING

© 2013 Teraspeed Consulting Group LLC

GROUP

```

# **New - Four Summary Tables in Section 10.7 of the Specification**

- Usages for Reserved Parameters

- Types for Reserved Parameters

- Formats for Reserved Parameters

- Types for Format values

- 28 Reserved Parameters, 18 new since Version 5.1

- · Part of one table shown next

Page 10

| and All                                    | OWS         | hl      | <u>م</u>                | ata '  | Tynes   |          |

|--------------------------------------------|-------------|---------|-------------------------|--------|---------|----------|

| and An                                     |             |         | ility Mode] - Microsoft |        | i ypes  |          |

| age Layout References Mailings Review View |             |         |                         |        |         |          |

| Table 31 – Allowable Data Ty               | ypes for Re | eserved | Paramete                | rs     |         |          |

| D 1D                                       | Data Type   |         |                         |        |         |          |

| Reserved Parameter                         | Float       | UI      | Integer                 | String | Boolean |          |

| AMI_Version <sup>1</sup>                   |             |         |                         | X      |         |          |

| DLL_ID³                                    |             |         |                         | X      |         |          |

| DLL_Path <sup>3</sup>                      |             |         |                         | X      |         |          |

| GetWave_Exists                             |             |         |                         |        | X       |          |

| Ignore_Bits <sup>2</sup>                   |             |         | X                       |        |         |          |

| Init_Returns_Impulse                       |             |         |                         |        | X       |          |

| Max_Init_Aggressors                        |             |         | X                       |        |         |          |

| Repeater_Type <sup>3</sup>                 |             |         |                         | X      |         |          |

| Rx_Clock_PDF                               | X           | X       |                         |        |         |          |

| Rx_Clock_Recovery_DCD <sup>3</sup>         | X           | X       |                         |        |         |          |

| Rx_Clock_Recovery_Dj <sup>3</sup>          | X           | X       |                         |        |         |          |

| Rx_Clock_Recovery_Mean <sup>3</sup>        | X           | X       |                         |        |         |          |

| Rx_Clock_Recovery_Rj <sup>3</sup>          | X           | X       |                         |        |         |          |

| Rx_Clock_Recovery_Sj <sup>3</sup>          | X           | X       |                         |        |         |          |

| Rx_DCD <sup>3</sup>                        | X           | X       |                         |        |         |          |

| Rx_Dj <sup>3</sup>                         | X           | X       |                         |        |         |          |

| Rx Noise <sup>3</sup>                      | X           |         |                         |        |         | mora a s |

## **Conclusion**

- Summary information provides quick references for IBIS and IBIS-AMI syntax

- Document references

http://www.eda.org/ibis/ver6.0/

tree\_6\_0.txt (unofficial)

evol\_6\_0.docx, .pdf (unofficial)

Page 12

# More on IBIS Modeling for Load-Dependent Current-Mode Differential Drivers

Lance Wang (Iwang@iometh.com)

IO Methodology Inc.

2013 IBIS Asian Summit

Nov. 15, 2013 Shanghai

© 2006-2013 IO Methodology Inc.

1

## **Outlines**

- Motivation

- Load-Dependent Current-Mode Differential Driver

- IBIS Extraction Method

- · Legacy method

- · Enhanced extraction method

- Summary

Note: The partial materials in this presentation have been presented in 2013 European IBIS Summit in Paris

© 2006-2013 IO Methodology Inc.

## Motivation

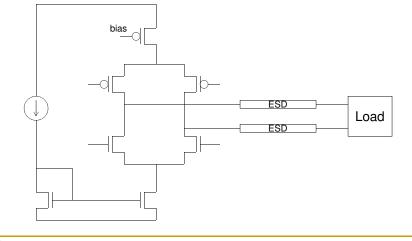

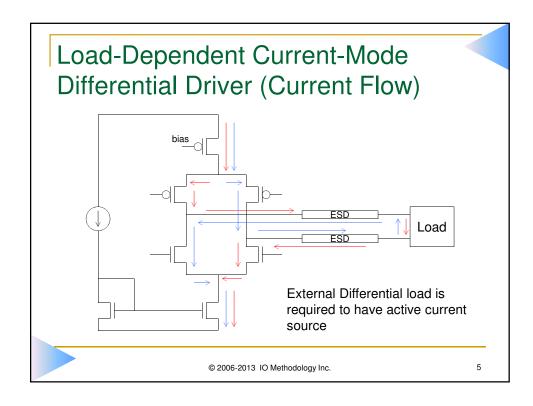

- Load-dependent current-mode differential pair buffers are found increasingly often in GHz serial link designs

- · Easy to control the output current and common-mode voltage

- · Often used in pre-emphasis buffers

- Using traditional IBIS buffer extraction method is not accurate enough

Is it possible to use the current IBIS spec for this kind of differential buffer?

© 2006-2013 IO Methodology Inc.

3

# Load-Dependent Current-Mode Differential Driver

© 2006-2013 IO Methodology Inc.

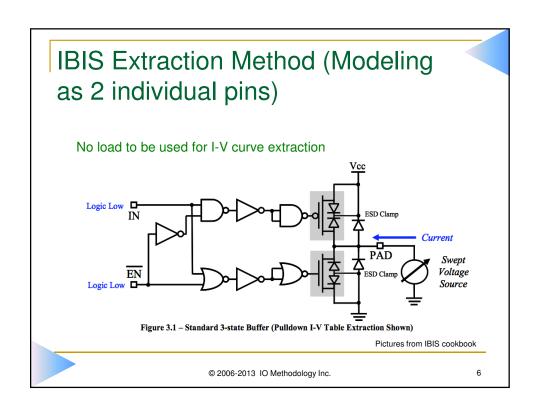

# IBIS Extraction Method (Modeling as 2 individual pins) Load connected to GND or VCC to be used for V-T curve extraction VCC END Clamp PAD Logic Low Figure 3.2 – Simulation Setup for Extracting Ramp Rate Information (Rising Edge Shown) Pictures from IBIS cookbook

## Summary

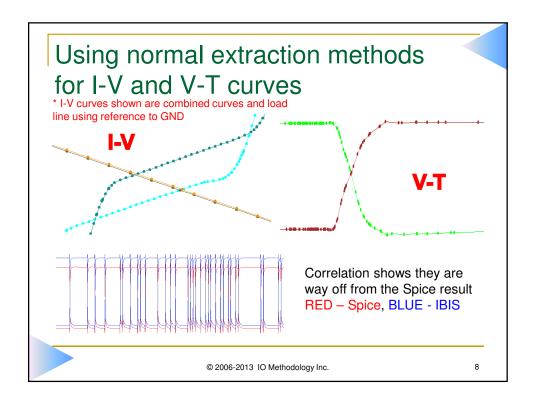

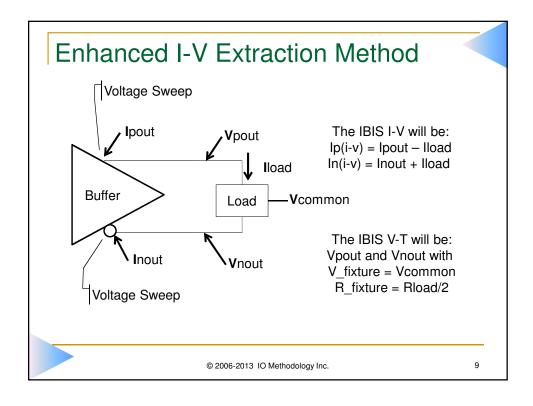

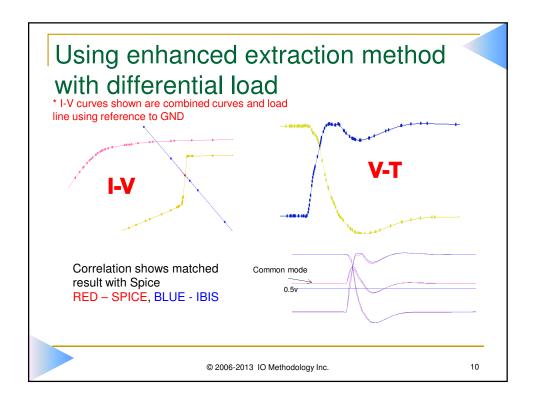

- Normal IBIS extraction method for load-dependent current-mode differential pair buffers produces inaccurate models

- Enhanced method considering differential load can solve this issue. It gives the matched results when correlating with Spice simulation results

- It would be better to have IBIS Spec accept "Rref\_diff/Cref\_diff" kind of differential loads for regular IBIS differential pair models

- Rref\_diff/Cref\_diff is limited for External model use now

- IBIS Spec needs to be enhanced when modeling dynamic PLL current mode buffer

- Various I-V tables for different diff\_loads

- Current dependent C-comp value table

© 2006-2013 IO Methodology Inc.

Asian IBIS Summit Shanghai, China, November 15, 2013

Bob Ross Teraspeed Consulting Group bob@teraspeed.com Yingxin Sun and Joy Li Cadence Design Systems sunyx@cadence.com joyli@cadence.com

Presented by Anders Ekholm, Ericsson

TERASPEED

CONSULTING

Page I

© 2013 Teraspeed Consulting Group LLC

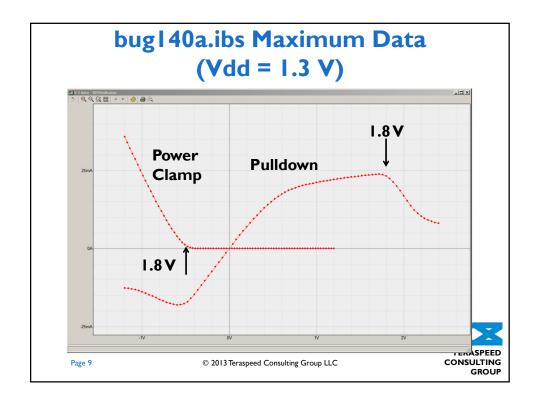

## Real Data from BUG140 and Cadence Presentations

- BUG140: http://www.eda.org/ibis/bugs/ibischk/bug140.txt

- (In all test cases, the [Gnd Clamp] data is 0.0 in the region of interest)

- Presentations

- "Golden Parser Non-monotonic Warning's Investigation" by Yingxin Sun and Joy Li, November 9, 2012: <a href="http://tinyurl.com/byqu7yn">http://tinyurl.com/byqu7yn</a> (Presented at the IBIS Quality Committee November 27, 2012)

- "Combined I-V Table Checks (BUG140)", January 31, 2013 IBIS Summit, Bob Ross, Yingxin Sun, and Joy Li

- "Ibischk5 Specification and Parser", May 15, 2013 IBIS Summit,

Bob Ross and Mike LaBonte (Signal Integrity Software)

© 2013 Teraspeed Consulting Group LLC

Page 2

## **BUG140** Issue

- Unexpected Non-Monotonic Warnings for Combined I-V Tables (derived from monotonic data)

- · Combined I-V table checks:

- [Pulldown] + [Gnd Clamp] + [Power Clamp]

- [Pullup] + [Gnd Clamp] + [Power Clamp]

TERASPEED CONSULTING

GROUP

- Ibischk5 parser is de facto standard for IBIS model correctness (and ibischk5 is embedded in tools)

- Some companies require 0 Errors, 0 Warnings

- IBIS Quality Spec, recommends 0 Errors and 0 Warnings

- Warning messages create support issue for model authors or automatic modeling utilities

Page 3

© 2013 Teraspeed Consulting Group LLC

## **Facts**

- No specification REQUIREMENT that individual or combined I-V tables be monotonic

- No stated method to sum mismatched voltage points (piecewise linear interpolation is allowed and used)

- Non-monotonicity often occurs outside of normal simulation region – in clamping region and not a problem

- Ibischk5 parser is working correctly

Page 4

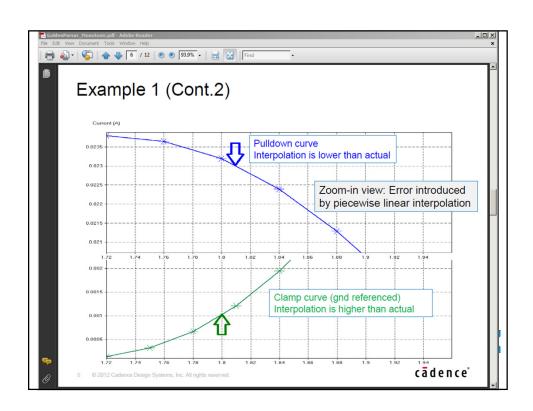

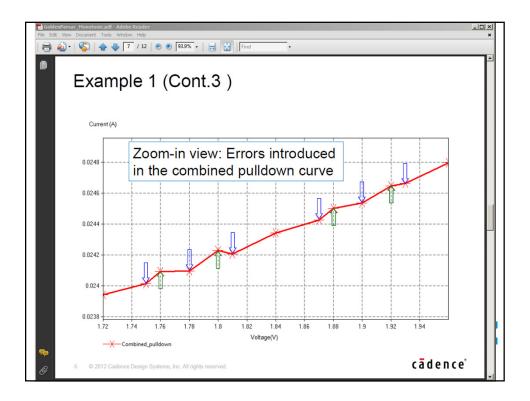

## **Observations**

- Non-monotonic behavior can occur

- Combined I-V table slope is small

- I-V table points are misaligned due to

- Offset V intervals due to Gnd, Vdd and delta V

- Different reference voltages (min/max)

- Extraction done with piecewise linear interpolation calculations (if not done right)

- Combination of above cases

- Example  $(y = x^2)$  next shows monotonic tables yielding non-monotonic summations

Page 5

s $\odot$  2013 Teraspeed Consulting Group LLC

# Example: x Step 2, Offset by I (Red: Interpolated Value)

Non-monotonic due to piecewise linear interpolation on both columns

TERASPEED CONSULTING

GROUP

Page 6

# x Step 0.02, Offset by 0.01 (Red: Interpolated Value)

Still non-monotonic with higher resolution data

Page 7

© 2013 Teraspeed Consulting Group LLC

# x Steps 0.02 and 0.01, 0.00 Offset (Red: Interpolated Value)

| x    | <b>y</b> 1 | y2      | y1-y2    |

|------|------------|---------|----------|

|      | = x^2      | $= x^2$ |          |

| 0.00 | 0.0000     | 0.0000  | 0.0000   |

| 0.01 | 0.0002     | 0.0001  | 0.0001   |

| 0.02 | 0.0004     | 0.0004  | 0.0000   |

| 0.03 | 0.0010     | 0.0009  | 0.0001   |

| 0.04 | 0.0016     | 0.0016  | 0.0000   |

| 0.05 | 0.0026     | 0.0025  | 0.0001   |

| 0.06 | 0.0036     | 0.0036  | \0.0000/ |

Page 8

TERASPEED CONSULTING GROUP

Different resolution data causes

non-monotonic combination

## **BUG140** Resolution

- Change WARNING to NOTE

- Valid solution for user

- Avoids tool and model developer support issues

- Add "based on piecewise linear interpolation" to message

- No practical fix

- Still issues with higher resolution or choosing percentage threshold for non-monotonic warning

- Piecewise linear interpolation is legal, and spline fitting would just hide information

**TERASPEED**

CONSULTING

Page 12

## Checking bug I 40a.ibs

### IBISCHK5 V5.1.2

```

Checking bug140a.ibs for IBIS 3.2 Compatibility...

```

```

NOTE (line 39) - Pulldown Typical data is non-monotonic NOTE (line 42) - Pulldown Minimum data is non-monotonic NOTE (line 42) - Pulldown Maximum data is non-monotonic NOTE (line 135) - Pullup Typical data is non-monotonic NOTE (line 137) - Pullup Maximum data is non-monotonic NOTE (line 138) - Pullup Minimum data is non-monotonic

```

WARNING - Combined Pulldown for Model: iobuf Maximum data is non-monotonic

Errors : 0

Warnings: 1

File Passed

Page 13

© 2013 Teraspeed Consulting Group LLC

## Fixed bug I 40a.ibs in Version 5.1.3

## IBISCHK5 V5.1.3

Checking bug140a.ibs for IBIS 3.2 Compatibility...

```

NOTE (line 39) - Pulldown Typical data is non-monotonic NOTE (line 42) - Pulldown Minimum data is non-monotonic NOTE (line 42) - Pulldown Maximum data is non-monotonic NOTE (line 135) - Pullup Typical data is non-monotonic NOTE (line 137) - Pullup Maximum data is non-monotonic NOTE (line 138) - Pullup Minimum data is non-monotonic

```

${\tt NOTE-Combined\ Pulldown\ for\ Model:\ iobuf\ Maximum\ data\ is\ non-monotonic\ based\ on\ piece-wise\ linear\ interpolation}$

Errors : 0

File Passed

Page 14

## Closure

- For best checking results, use the latest version of ibischk5

- Parser being updated as new BUG reports are submitted and processed.

Page 15

Yingxin Sun and Raymond Y. Chen IBIS Asia Summit Shanghai, China Nov. 15, 2013

$c\bar{a}dence^{\circ}$

## Agenda

- 1. SPICE Model and Behavioral Buffer Model

- 2. Over-Clocking Problem in IBIS

- 3. Proposed Solution and Results

2 © 2013 Cadence Design Systems, Inc. All rights reserved

cādence\*

## Agenda

- 1. SPICE Model and Behavioral Buffer Model

- 2. Over-Clocking Problem in IBIS

- 3. Proposed Solution and Results

3 © 2013 Cadence Design Systems, Inc. All rights reserved

cādence°

## SPICE Model and Behavioral Buffer Model

- SPICE model is a circuit netlist at transistor level, it contains detailed information about the circuit design and process parameters.

- Behavioral model is a black box model with certain terminal information, which is obtained from measurement or extracted from SPICE model. IBIS is a widely adopted standard behavioral model.

4 © 2013 Cadence Design Systems, Inc. All rights reserved

cādence

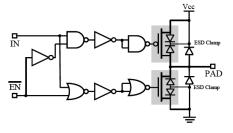

## A Simple Schematic for IBIS Model

- The non-linear behavior of pullup, pulldown and clamps are described by I/V tables, and modeled as voltage controlled current sources.

- The transition behavior is described by the V/T table of the rising/falling waveforms under specified loading condition. And they are used to derive/scale instantaneous value of the I/V curves.

- Other important parasitic elements

- IBIS, as a behavioral model, does not contain transistor equation, some of the physics and detailed response may not exist in a simple model, hence the issue that will be discussed next.

## Agenda

- 1. SPICE Model and Behavioral Buffer Model

- 2. Over-Clocking Problem in IBIS

- 3. Proposed Solution and Results

6 © 2013 Cadence Design Systems, Inc. All rights reserved

cādence°

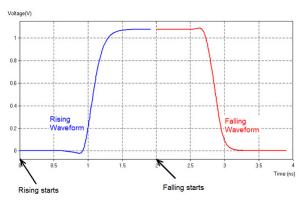

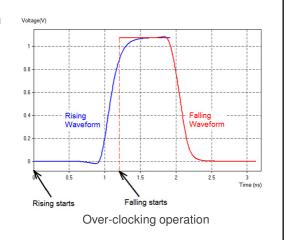

## Understand the Over-Clocking

Normal operating, the input data bit width > the time range of the IBIS rising and falling waveform.

Normal operation

7 © 2013 Cadence Design Systems, Inc. All rights reserved

cādence°

## Understand the Over-Clocking (cont.)

- If the input signal bit width is smaller than the time range of the IBIS waveforms, the next transition is triggered before this transition is finished.

- The behavior of the IBIS simulator may be unpredictable.

- Google "IBIS Overclocking" to find out more about this issue discussion since 2002

8 © 2013 Cadence Design Systems, Inc. All rights reserved

cādence

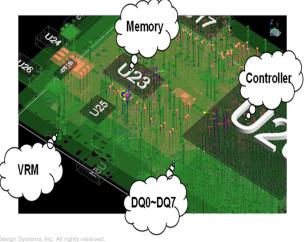

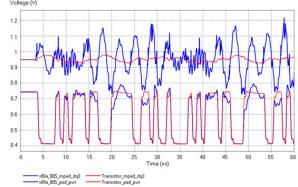

## Simulation Problem Is Shown with A DDR3 SSO **Test Case**

8 signal nets + 1 power nets + 1 ground net from a real PCB design. Bit width is 1ns, the pattern is 000101011101100111110011010010

cādence"

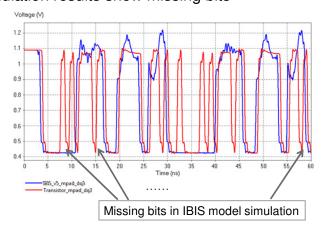

## Problematic Results from Over-Clocking

- A test case operating over-clocking

- Simulation results show missing bits

cādence\*

# Existing Solution to Solve Over-Clocking Problem

- V/T curve windowing by cutting the initial delay and the flat tail of the rising/falling waveforms of IBIS model to make the time range shorter

- The windowing can be done either in IBIS model creation or simulation tools

11 © 2013 Cadence Design Systems, Inc. All rights reserved

cādence\*

# Simulation Results with V/T Windowing

- The missing bits resolved

- Therefore, simulator with proper V/T windowing scheme should automatically handle overclocking issue in IBIS 4.2 model

However, voltage on power net mismatches between transistor model and IBIS model due to the dynamic power noise not modeled.

12 © 2013 Cadence Design Systems, Inc. All rights reserved

cādence\*

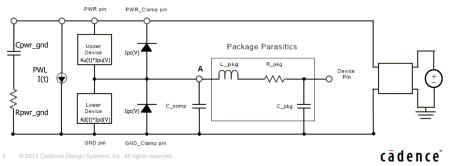

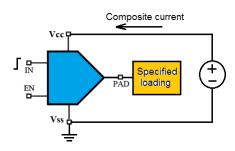

# New Challenge of Over-Clocking with Composite Current

- To accurate model the power-aware buffer model, the composite currents (I/T) are introduced in IBIS V5.0 to give the current waveforms on power pin.

- The I/T data must be time correlated with the waveform V/T data which are extracted from pad pin.

- The composite current includes the contribution of the pre-driver and all the other on-die P/G paths. It has wider time range than V/T waveform.

13 © 2013 Cadence Design Systems, Inc. All rights reserved

cādence°

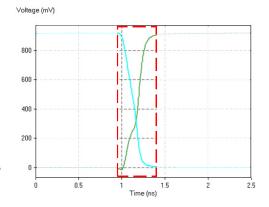

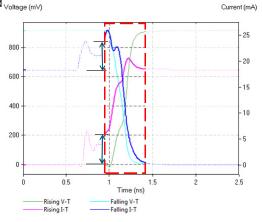

## Windowing with Composite Current

- Now both V/T and I/T need Voltage (m/V) to be windowed.

- Choosing window based on wider I/T curve will not help, since over-clocking solution requires narrow timing window for higher frequency operation.

- Still choosing a window based on V/T will cut the composite current incomplete which will form a sharp step current.

4 © 2013 Cadence Design Systems, Inc. All rights reserved

cādence

## Observation of This New Challenge

- With the addition of composite current (I/T) in IBIS 5.0, old windowing technique (V/T based) in IBIS simulator need to be improved, and can't be directly applied to I/T data to solve over-clocking issue.

- With IBIS 5.0 models become increasingly popular in the last few years, there are more awareness and discussion of this issue.

- A solution was developed by us two years ago to tackle this challenge.

16 © 2013 Cadence Design Systems, Inc. All rights reserved

cādence\*

# Agenda

- 1. SPICE Model and Behavioral Buffer Model

- 2. Over-Clocking Problem in IBIS

- 3. Proposed Solution and Results

17 © 2013 Cadence Design Systems, Inc. All rights reserved

cādence°

# Key Point of Advanced Over-Clocking Solution

- Using the V/T waveform windowing

- Adding one stage to the existing driver to keep the pre-driver behavior for the buffer switching delay and power current

- Taking the composite current compensation into two parts:

- Driver contribution

- Pre-driver contribution

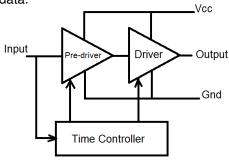

Input Pre-driver Driver Output Gnd

cādence

© 2013 Cadence Design Systems, Inc. All rights reserved

# Implementing the Proposed Over-Clocking Solution

- The proposed over-clocking solution can be implemented into an advanced IBIS model, which is a SPICE netlist with <u>integrated model</u> data and simulation algorithm.

- The proposed over-clocking solution can also be implemented into an advanced IBIS simulator to automatically handle the windowing of both V/T and I/T data.

19 © 2013 Cadence Design Systems, Inc. All rights reserved

cādence\*

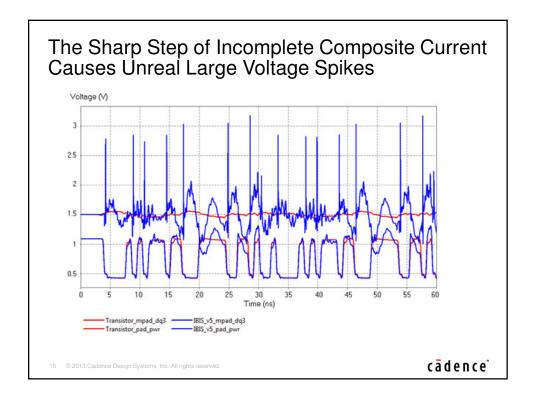

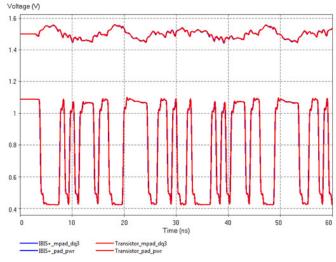

# Simulation results with Advanced Over-Clocking Solution

© 2013 Cadence Design Systems, Inc. All rights reserved.

cādence°

# Simulation Performance Summary

- Very good correlation between IBIS and the original transistor model for real SSO simulation, both signals and power/ground waveforms match very well, even under over-clocking scenario.

- The 60ns simulation time is based on 32 clock cycles of data input.

- It takes 54 minutes for original transistor level SPICE model.

- It takes 55 seconds for the behavioral model with the advanced over-clocking solution.

- Note: HSPICE is used to run the simulations for all the models, including the advanced IBIS model with over-clocking solution.

21 © 2013 Cadence Design Systems, Inc. All rights reserve

cādence°

### Conclusion

- Power-aware buffer model generation has been implemented for IBIS 5.0 standard. When used in highspeed power-aware SSO simulations, user often has to deal with IBIS over-clocking issues.

- With the proposed algorithm for handling composite currents under over-clocking situation, more advanced model shows significant accuracy improvement compared with traditional IBIS models, while keeping the fast simulation advantages of IBIS.

- Advances in IBIS standard, together with advances in modeling and simulation algorithms, continue to make this behavioral model technique a great and practical engineering approach for high-speed design.

22 © 2013 Cadence Design Systems, Inc. All rights reserved.

cādence\*

### References

- [1] Perivand F. Tchrani, Yuzhe Chen, Jiayuan Fang, "Extraction of Transient Behavioral Model of Digital I/O Buffers from IBIS", 46th IEEE Electronic Components & Technology Conference, Orlando, May 28-31, 1996, pp 1009-1015.

- [2] Ying Wang and Han Ngee Tan, "The Development of Analog SPICE Behavioral Model Based on IBIS Model", Proceedings of the Ninth Great Lakes Symposium on VLSI, March 1999.

- [3] Sam Chitwood, Raymond Y. Chen, Jiayuan Fang, "An Initial Case Study for BIRD95 Enhancing IBIS for SSO Power Integrity Simulation", IBIS Summit DesignCon, January 2005

- [4] Raymond Y. Chen, "Recent Development of IBIS and Related EDA Technologies", Sigrity Annual User Forum, May 24, 2011

23 © 2013 Cadence Design Systems, Inc. All rights reserved

cādence°

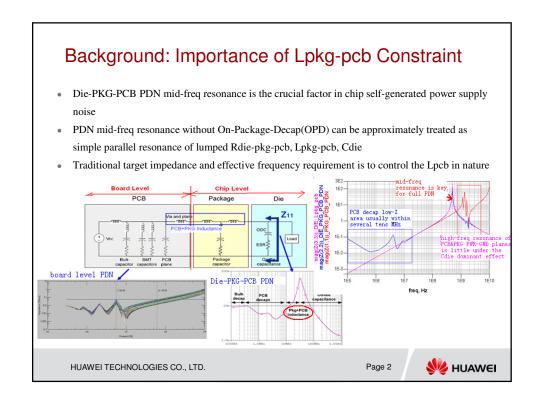

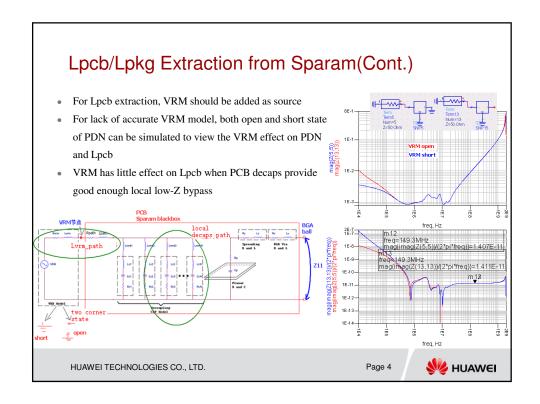

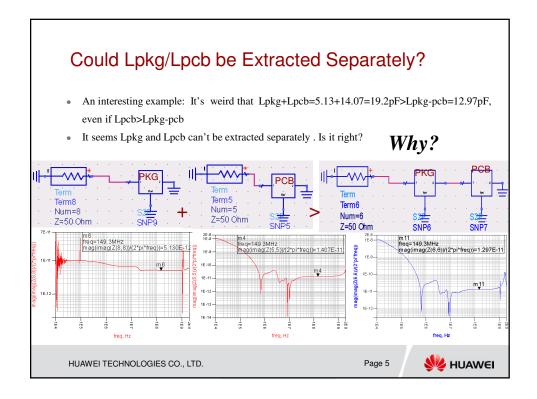

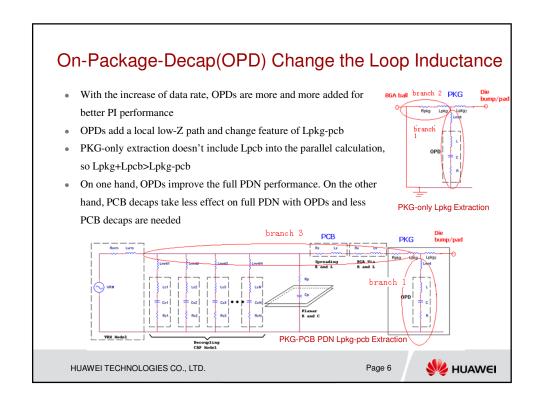

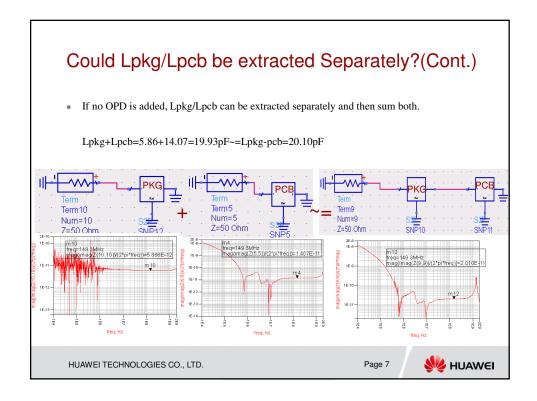

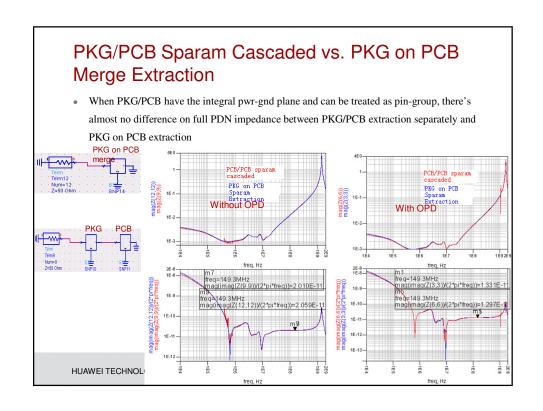

# Lpcb/Lpkg Extraction from Sparam PCB and PKG are belong to different teams or companies, so Lpcb/Lpkg is usually extracted from Sparam separately Inductance is dominant in high frequency, so it can be extracted from imaginary part of Zin in flat area Z(f) = R + jωL + 1/jωC = R + j(ωL - 1/ωC) For Lpkg extraction, BGA ball should be connected to AC ground or AC source to specify the source For Lpcb extraction, see next page Then Lpkg-pcb=Lpkg+Lpcb PKG Z11 PKG Z11 PKG Z11 PKG Z11 PKG Z11 PKG Source PKG-only Lpkg Extraction HUAWEI TECHNOLOGIES CO., LTD. Page 3

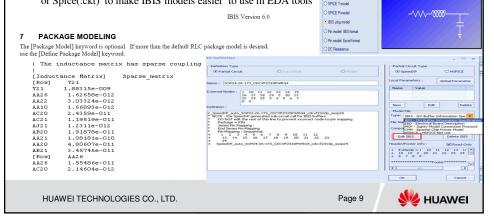

### The Limitation of IBIS PKG PWR/GND RLC Model

- As we discussed, with OPDs it is not suitable to use PKG-only Lpkg like IBIS RLC PKG model to do the full PDN simulation

- For the present, we have to edit the netlist manually to include IBIS with other format PKG model

- We propose that the IBIS grammar be compatible with more complex models based on Sparam or Spice(.ckt) to make IBIS models easier to use in EDA tools

| We propose that the IBIS grammar be compatible with more complex models based on Sparam or Spice(.ckt) to make IBIS models easier to use in EDA tools

| We propose that the IBIS grammar be compatible with more complex models based on Sparam or Spice(.ckt) to make IBIS models easier to use in EDA tools

| We propose that the IBIS grammar be compatible with more complex models based on Sparam or Spice(.ckt) to make IBIS models easier to use in EDA tools

| We propose that the IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models easier to use in EDA tools | The IBIS models ea

# Summary

- With OPDs, Lpkg-pcb can't be summed with Lpkg and Lpcb extracted from sparam separately, but should be extracted from PKG-PCB sparam cascaded

- OPDs not only improve the full PDN performance, but weaken the PCB decaps effect on full PDN as well, which make PCB decaps more simplified

- IBIS PKG RLC model is not suitable for PDN simulation with OPDs. We

propose the IBIS grammar be compatible with Sparam or Spice(.ckt) models to

make IBIS models easier to use in commercial EDA tools

HUAWEI TECHNOLOGIES CO., LTD.

Page 10

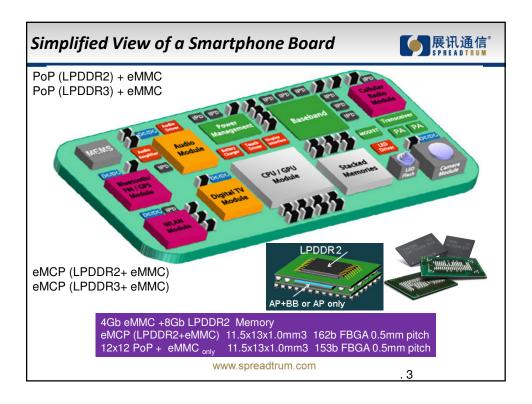

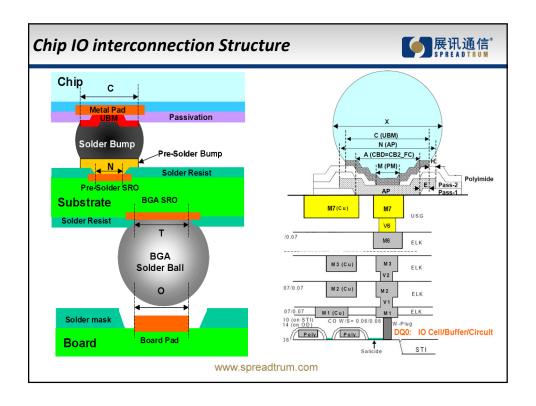

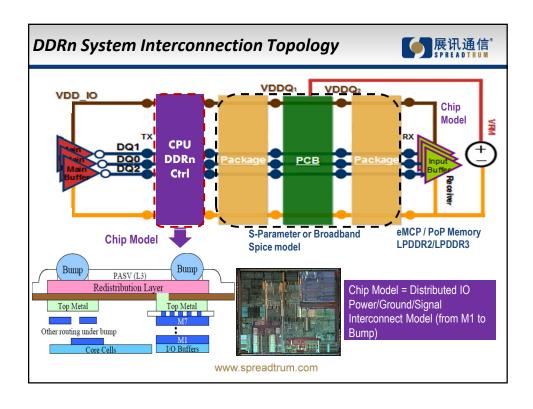

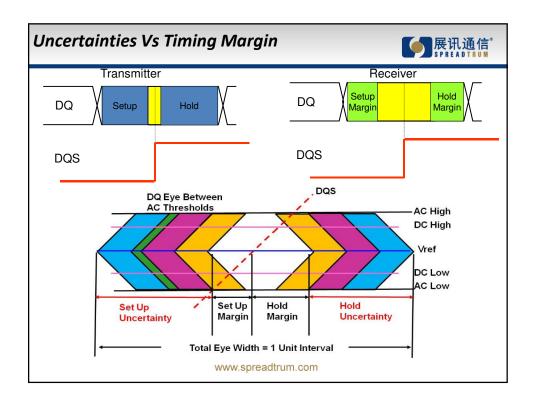

### DDRn Setup/Hold Timing Budgets (Uncertainties : Skew & Jitter) Interconnection Receiver Transmitter Contributions Contributions Contributions DDL (Data Delay Line) Granularity and bit offset (BDL and LCDL ) (Static) Crosstalk (Pushout/Pullin from nearby aggressor signals and serpentine routing ) (Dynamic) DDRn Data Set Up and Hold specifications (tDS, tDH) (Static) Register Mismatch within the PHY (Static) Reflections,Inter-Symbol Interference (ISI) (Impedance discontinuities, topology,loading) DLL Jitter including Clock Source Jitter (Dynamic) Setup and Hold Slew rate Derating (Static) High frequency losses (Dielectric and Conductor losses) DLL Phase Error (Dynamic) PHY Skew between DQS/DQS# and DQ signals (Static) Dielectric mismatches between layers (Dynamic) Process Variation Effects (Static) IO Output Rise Fall Delay Mismatch (Static) SSO/SSN Pushout (Effects of non-ideal power distribution network-PDN) (Dynamic) VT Drift (BDL and LCDL Setting) (Dynamic) www.spreadtrum.com

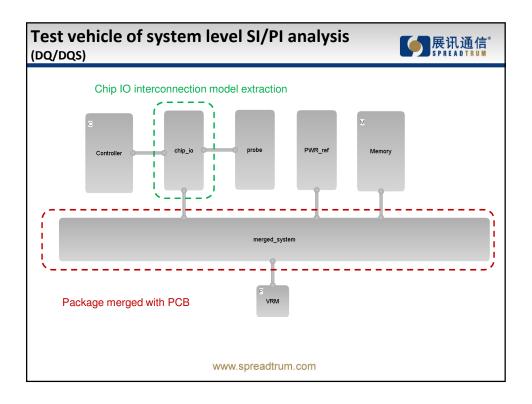

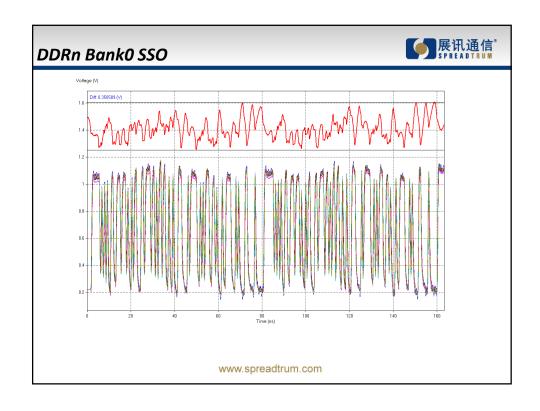

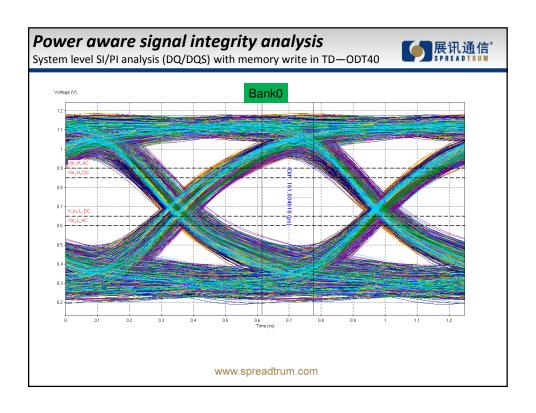

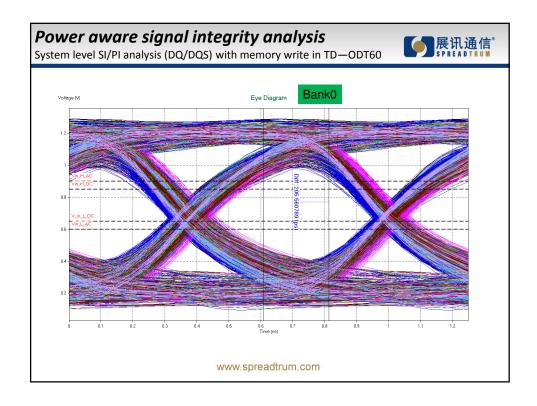

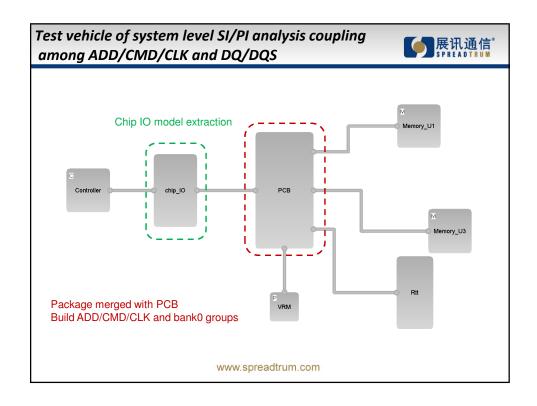

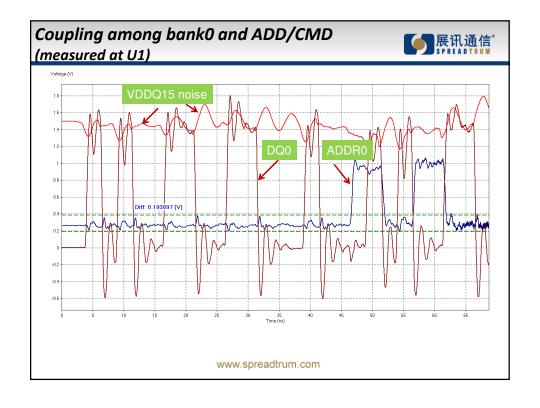

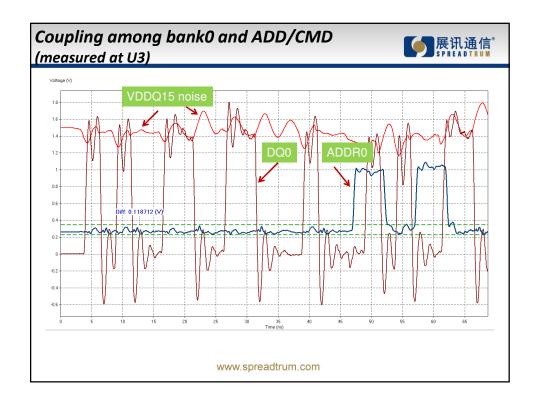

# Test vehicle of system level SI/PI analysis coupling among ADD/CMD/CLK and DQ/DQS | Bus Group/Signal | Stimulus Patern | Stimulus Patern

### Summary

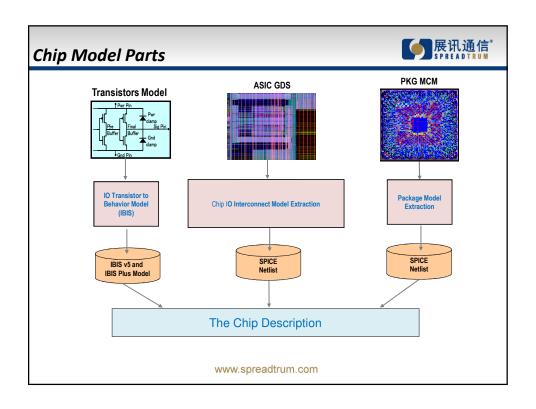

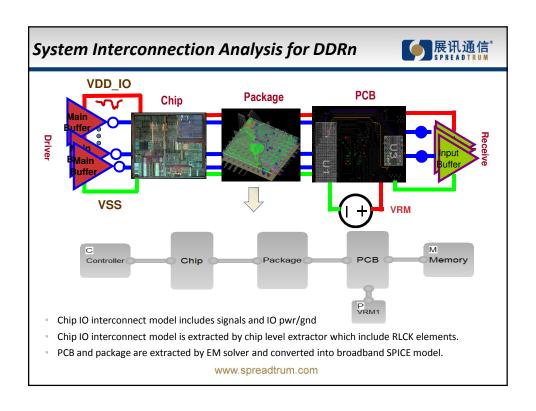

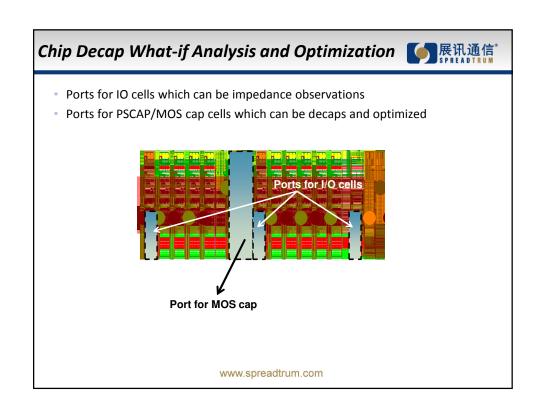

- Chip IO interconnect model should include IO Power/Ground/Signal Interconnect Model

- For high speed and low power DDR systems (LPDDR3/DDR3L/DDR4), Chip IO interconnect model is crucial for IO-SSO analysis.

- Chip IO interconnect model is one part for Chip but not in IBIS model.

- With Chip IO Interconnection model, Chip vendor can do more accurate DDRn signoff analysis to predict System electrical performace before ASIC tapeout.

- On-die RC or better distributed chip IO interconnect model can be more realistic for signal/power analysis

- New System Signoff methodology enable to avoid overdesign or under-design for on-die Decap Cell

www.spreadtrum.com

# cadence

www.spreadtrum.com

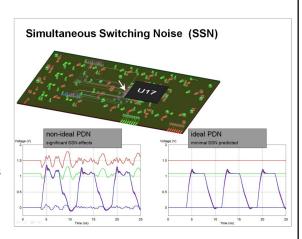

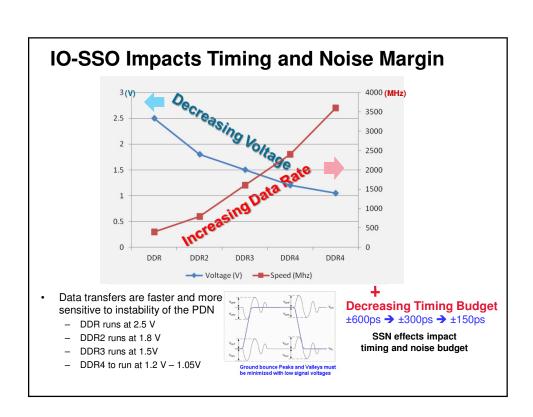

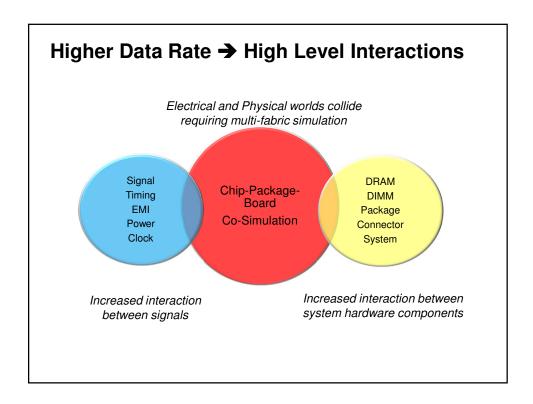

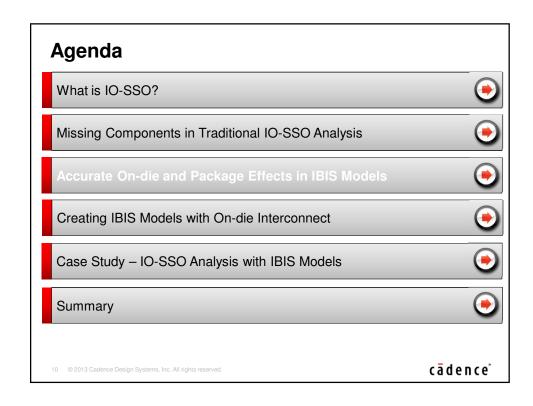

### What is IO-SSO?

- A DDR memory interfaces is a parallel bus

- Many signals represent a data byte/word/32-bit word/64-bit word

- Simultaneous switching signals / outputs are referred to as SSO

- The noise between power and ground created is referred to as simultaneous switching noise (SSN)

- IC Designers refer to this phenomenon as IO-SSO

- SI/PI can be verified by IO-SSO

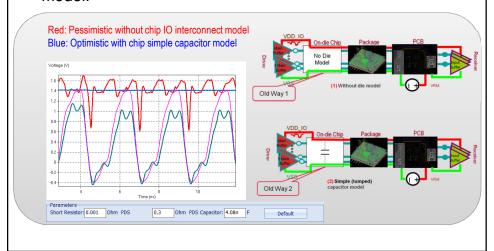

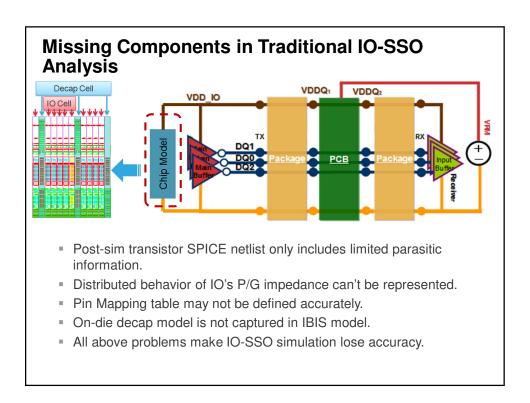

### **Traditional IO-SSO Simulation Scenarios**

- Pessimistic result when analyzed without on-die model.

- Optimistic result when analyzed with estimated on-die model.

### Asia IBIS Summit 2012

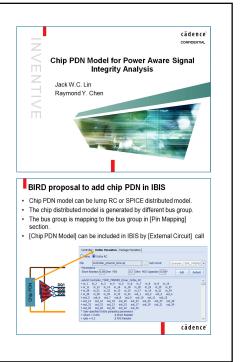

- Chip PDN model is crucial for IO-SSO analysis.

- Without Chip PDN model, artificially large power /ground noise impact the signal waveform significantly

- Chip PDN is responsible to filter high frequency noise

- On-die RC or better distributed chip PDN model can yield realistic power/ground noise analysis

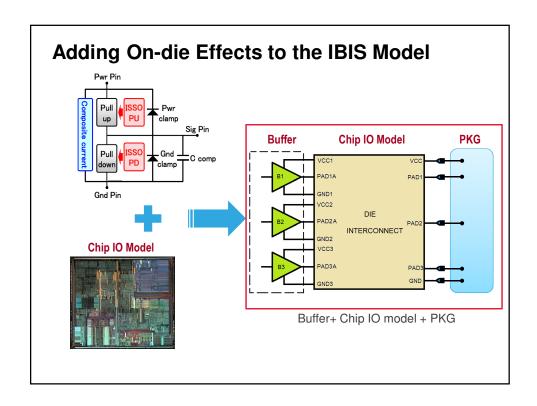

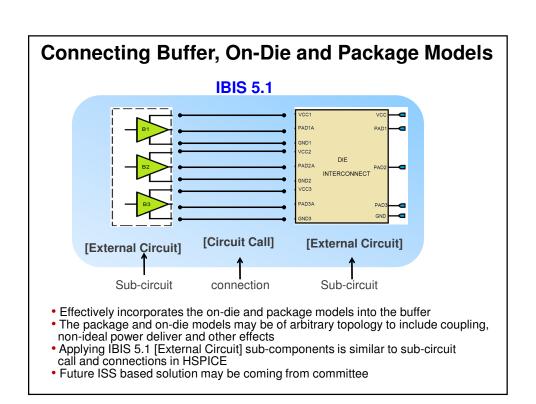

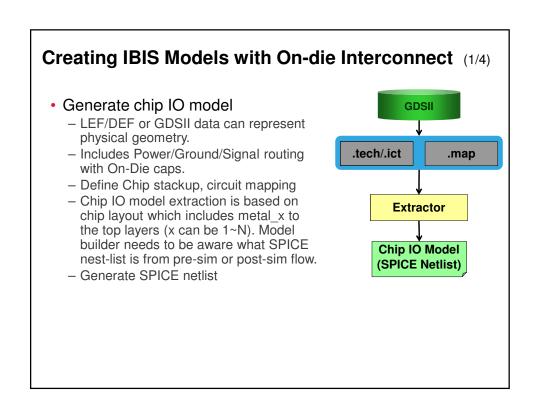

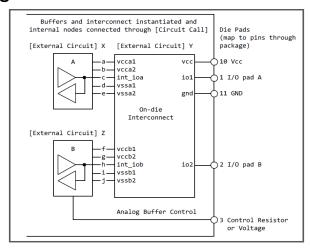

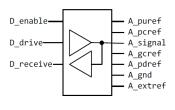

# **Creating IBIS Models with On-Die Interconnect** (2/4)

- [External Circuit] will be represented as IO buffer, chip IO, package.....

- · Connect each [External Circuit] through [Circuit Call]

### **Creating IBIS Models with On-die Interconnect** (3/4)

• Ports under [External Circuit]

The [External Circuit] keyword allows the user to define any number of ports and port functions on a circuit.

Port name for IO Buffer

Ports A\_puref A\_pdref A\_signal A\_drive A\_enable A\_receive A\_pcref A\_gcref

Ports vcca1 Ports vcca2

.....

### **Creating IBIS Models with On-die Interconnect** (4/4)

- Define [Pin] and [Node Declarations]

- When a [Circuit Call] keyword defines any connections that involve one or more die pads (and consequently pins), the corresponding pins on the [Pin] list must use the reserved word "CIRCUITCALL" in the third column instead of a model name.

- [Node Declaration] provides a list of internal die nodes and/or die pads for a [Component] to make unambiguous interconnection descriptions possible

[Node Declarations] | Must appear before any [Circuit Call] keyword | Die nodes:

pu1 pd1 io1p io1 in1 en1 outin1 | List of die nodes

pu2 pd2 io2p io2 in2 en2 outin2 | List of die nodes

pu3 pd3 io3p io3 in3 en3 outin3 | List of die nodes

[End Node Declarations]

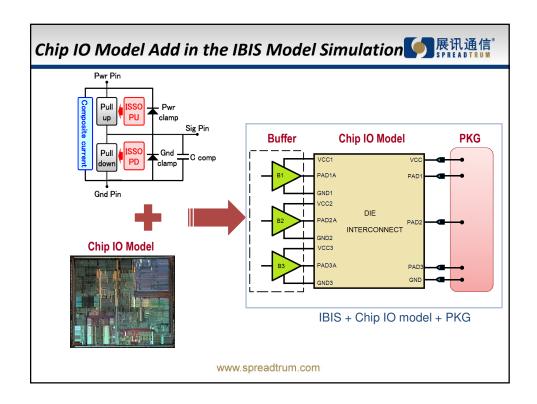

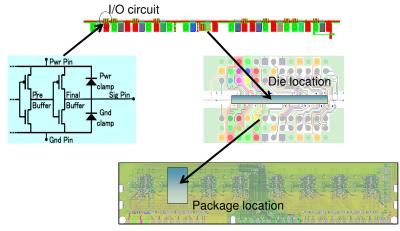

# Case Study – IO-SSO Analysis with IBIS Models

- · I/O transistor circuit is converted into power-aware IBIS model

- · Chip is extracted by chip level extractor which include RLCK elements.

- PCB and package S-parameters are extracted and converted to broadband SPICE models.

- · Only 1 group DDR data is considered for this test

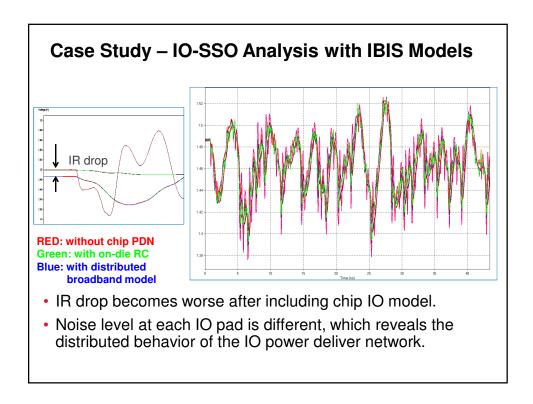

# Case Study – IO-SSO Analysis with IBIS Models RED: without chip PDN Green: with on-die RC Blue: with distributed broadband model SSN from SSO will be over or under estimated without accurate chip IO model. Timing push in/out will become worse if more IOs are switching at the same time.

### **Summary**

- For tighter timing and noise budgets in LPDDR3 or DDR4, system level IO-SSO analysis is helpful for design margin assessment

- IBIS 5.1 models may include power-aware IO buffer, chip P/G/S from IOs to bump pads, and arbitrary package models

- existing IBIS syntax is applied (using [External Circuit])

- additional techniques using ISS within the IBIS model are being discussed in committee

- The approach described allows chip vendors to deliver more complete IBIS models to their customers to enable faster and more accurate product design verification

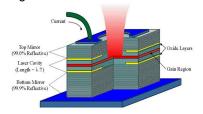

# Modeling, Extraction and Verification of VCSEL Model for IBIS AMI

Asian IBIS Summit Shanghai, China November 15, 2013

Zhaokai YUAN Agilent Technologies, Inc.

Agilent Technologies

### **Outline**

- Introduction

- · Optical Link Simulation

- VCSEL(Vertical Cavity Surface Emitting Laser) simulation under IBIS-AMI

- VCSEL Modeling and Extraction

- · Thermal based modeling

- · Curve fitting algorithm

- VCSEL Verification

- · Test case including VCSEL device

- · The comparison between simulation and measured data

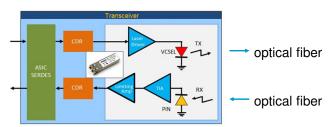

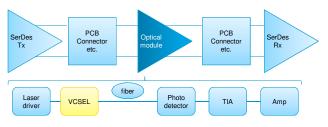

# Introduction Optical Link System and Simulation(cont.)

· Optical Link Simulation

### Inside SerDes Tx & Rx

- Equalization (FFE, CTLE & DFE)

- Clock-data recovery (CDR)

### Inside optical module

- Input voltage signal drives VCSEL to emit photons

- · Photons propagate along optical fiber

- · Photons are converted into photocurrent in PIN

- · TIA converts current into output voltage

# Introduction Optical Link System and Simulation(cont.)

- Extending AMI to Optical Channel

- · Treat the entire optical module as a mid-channel repeater

- Encapsulate all optical behaviors inside the optical model

- · Extend AMI simulation to include repeater

### Introduction **VCSEL Basic**

- VCSEL(Vertical Cavity Emitting Laser)

- · Characteristics

- High Data Rate, up to 40GHz(state of art)

- Low power cost(input ~ mA, output ~ mW)

- Single-longitudinal-mode operation

- Suitability for monolithic 2-D integration

- Application

- Very short range data transmission

- Board to board data transmission

### Introduction **VCSEL Basic**

- VCSEL modeling

- · 3-D modeling and simulation

- From the principle of laser point of view

- Accurate but too complicated

- · SPICE simulation

- As VCSEL is an optical device, SPICE model may not be the initial design, a new SPICE schematic is needed

- Hard to communicate due to IP issue

- IBIS-AMI(Algorithmic Modeling Interface)

- Focusing on performance only

- Treat the VCSEL as an algorithm unit

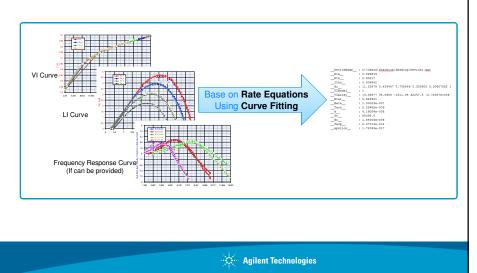

### VCSEL Modeling and Extraction VCSEL Modeling

- · Modeling Principle

- VCSEL's performance vs. Thermal behavior

- Data flow based

- The relationship between input current(I) and output power(Po) under the effect of temperature(T)

- Peripheral simulation

- Working schematic

Agilent Technologies

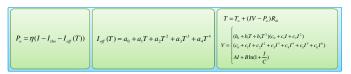

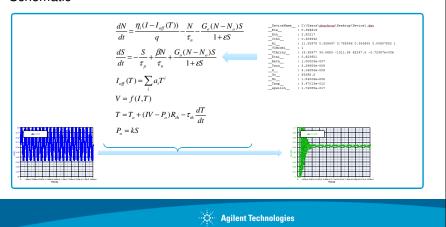

## VCSEL Modeling and Extraction VCSEL Modeling

- Rate-Equation-Based Thermal VCSEL Model

- · Transient Analysis

$$\begin{bmatrix} \frac{dS}{dt} = -\frac{S}{\tau_p} + \frac{\beta N}{\tau_a} + \frac{G_o(N-N_o)S}{1+\varepsilon S} \\ \frac{dN}{dt} = \frac{\eta_c(I-I_{og}(T))}{q} - \frac{N}{\tau_a} - \frac{G_o(N-N_o)S}{1+\varepsilon S} \\ \end{bmatrix} \\ I_{og}(T) = a_0 + a_1T + a_2T^2 + a_3T^3 + a_4T^4 \\ I_{og}(T) = a_0 + a_1T + a_2T^2 + a_3T^3 + a_4T^4 \\ V = \begin{pmatrix} G_0 + b_1T + b_2T^2)(c_0 + c_1I + c_2I^2) \\ G_0 + c_1I + c_2I^2 + c_2I^2$$

Stationary Analysis

### VCSEL Modeling and Extraction VCSEL Extraction

- · Extraction Basics

- VCSEL's performance ↔ Parameter values in rate equations

- Measured curves

- LI ~ Po(I; T)

- Measured stationary, shows the relationship between input current and the output power under different ambient temperature

- VI  $\sim$  V(I; T)

- Measured stationary, shows the relationship between input current and the voltage for connection, also with effect of ambient temperature

- Frequency response ~ H(w)

- Measured stationary, shows the frequency response, reveals the signal transmission characteristics

### VCSEL Modeling and Extraction VCSEL Extraction

- Extraction Method

- · Curve Fitting Algorithm

- LS curve fitting

- · Just solve the matrix equations

- · Suitable for simple relationship equations, such as the polynomial

- · Accurate and less time cost

- Minimal gradient curve fitting

- · Try to find the certain set of values which can generate the smallest error

- · Suitable for more complex equations, especially with iterations

- Need some pre-knowledge of the range of the parameters

- More time cost for accuracy

# **VCSEL Modeling and Extraction VCSEL Extraction**

Schematic

### **VCSEL Verification**

- VCSEL Simulation

- Schematic

### **VCSEL Verification**

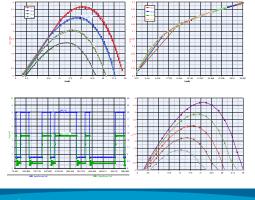

- Case 1 ~ device verification

- 863-nm bottom-emitting VCSEL, 16-mm diameter

- Extraction

- Curves fitting result

- · LI and VI curve

- Behavior mode is generated with file format

- Simulation

- Po(I) under different To

- Response for large signal

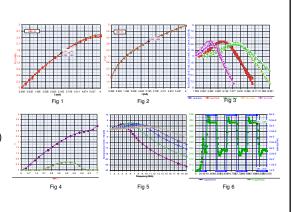

### **VCSEL Verification**

- Case 2 ~ device verification

- · 3.1um diameter thin-oxide-aperture VCSEL

- **Extraction Result**

- Curves fitting result

- LI(Fig 1)

- VI(Fig 2)

- Freq. response(Fig3)

- Simulation

- Po(I) simulation (Fig4)

- Frequency response(Fig5)

- Response for large signal(Fig6)

### **VCSEL Verification**

- Case 3 ~ optical link simulation

- 25GHz signal transmission

- A whole optical link: current  $\rightarrow$  optical signal  $\rightarrow$  current

IBIS Asia Summit Shanghai, China Nov. 15, 2013

cādence°

# Agenda

- Crosstalk in differential buffers

- Overview of Crosstalk Cancellation block

- Need for Adaptive Crosstalk Cancellation

- AMI Modeling of Crosstalk Cancellation block

- Simulation results and Conclusion

# Agenda

- Crosstalk in differential buffers

- Overview of Crosstalk Cancellation block

- Need for Adaptive Crosstalk Cancellation

- AMI Modeling of Crosstalk Cancellation block

- -Simulation results and Conclusion

3 © 2013 Cadence Design Systems, Inc. All rights reserved

cādence°

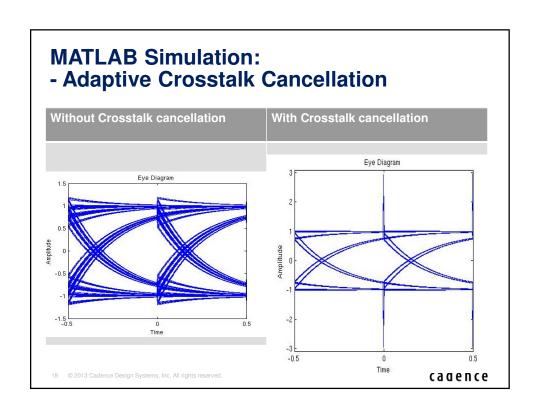

### **Crosstalk in Differential PCB Interconnects**

- Crosstalk from neighboring channels at high frequencies causes Crosstalk-Induced Jitter (CIJ).

- Depends on the length, width and spacing of the traces.

- However, it is also a function of data-pattern.

Faster switching increases crosstalk.

- Cancellation of crosstalk can result in smaller spacing between the traces or higher BER

4 © 2013 Cadence Design Systems, Inc. All rights reserved

# Agenda

- Crosstalk in differential buffers

- Overview of Crosstalk Cancellation block

- Need for Adaptive Crosstalk Cancellation

- AMI Modeling of Crosstalk Cancellation block

- -Simulation results and Conclusion

5 © 2013 Cadence Design Systems, Inc. All rights reserved

cādence°

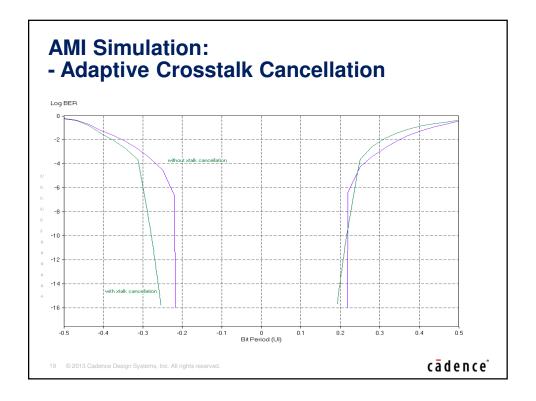

# Crosstalk Induced Jitter (CIJ)

- CIJ causes Far End Crosstalk (FEXT) and Near End Crosstalk (NEXT). FEXT is more dominant for PCB traces.

- Far End Crosstalk (FEXT) from aggressor channel to the victim channel is proportional to the derivative of aggressor channel impulse response:

$h(t)_{FEXT} = -K \frac{\partial h(t)_{aggressor}}{\partial t}$

6 © 2013 Cadence Design Systems, Inc. All rights reserved

# **Crosstalk Induced Jitter (CIJ)**

$$h(t)_{\textit{FEXT}} = -K \frac{\partial h(t)_{\textit{aggressor}}}{\partial t}$$

- Here K is the crosstalk coupling coefficient that depends on length, height and spacing between traces.

- Crosstalk also depends on data transitions. More transitions increase crosstalk

7 © 2013 Cadence Design Systems, Inc. All rights reserved

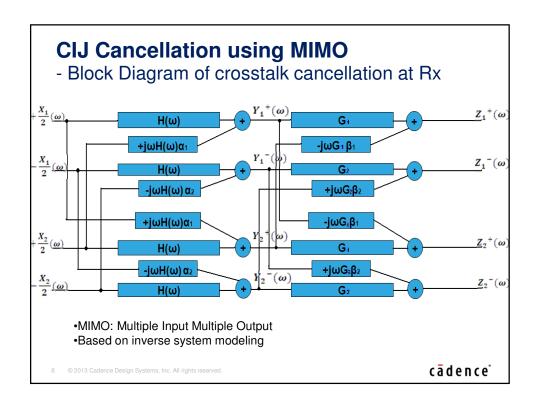

### **CIJ Cancellation using MIMO**

Output as a function of Inputs can be expressed as:

$$\begin{bmatrix} Z_1^-(\omega) \\ Z_2^+(\omega) \\ Z_2^-(\omega) \end{bmatrix}$$

$$=\begin{bmatrix} h(\omega) & 0 & j\omega h(\omega)\alpha_1 & 0 \\ 0 & h(\omega) & 0 & -j\omega h(\omega)\alpha_2 \\ j\omega h(\omega)\alpha_1 & 0 & h(\omega) & 0 \\ 0 & -j\omega h(\omega)\alpha_2 & 0 & h(\omega) \end{bmatrix} \begin{bmatrix} G_1 & 0 & -j\omega G_1\beta_1 & 0 \\ 0 & G_2 & 0 & +j\omega G_2\beta_2 \\ -j\omega G_1\beta_1 & 0 & G_1 & 0 \\ 0 & +j\omega G_2\beta_2 & 0 & G_2 \end{bmatrix} \begin{bmatrix} +\frac{X_1}{2}(\omega) \\ -\frac{X_1}{2}(\omega) \\ -\frac{X_2}{2}(\omega) \\ -\frac{X_2}{2}(\omega) \end{bmatrix}$$

$$=\begin{bmatrix} G_1h(\omega)(1+\omega^2\alpha_1\beta_1) & 0 & j\omega G_1h(\omega)(\alpha_1-\beta_1) & 0\\ 0 & G_2h(\omega)(1+\omega^2\alpha_2\beta_2) & 0 & -j\omega G_2h(\omega)(\alpha_2-\beta_2)\\ j\omega G_1h(\omega)(\alpha_1-\beta_1) & 0 & G_1h(\omega)(1+\omega^2\alpha_1\beta_1) & 0\\ 0 & -j\omega G_2h(\omega)(\alpha_2-\beta_2) & 0 & G_2h(\omega)(1+\omega^2\alpha_2\beta_2) \end{bmatrix} \begin{vmatrix} +\frac{X_1}{2}(\omega) \\ -\frac{X_2}{2}(\omega) \\ +\frac{X_2}{2}(\omega) \\ -\frac{X_2}{2}(\omega) \end{vmatrix}$$

•If  $\alpha$ 1=  $\beta$ 1  $\alpha$ 2=  $\beta$ 2, crosstalk becomes zero!!

9 © 2013 Cadence Design Systems, Inc. All rights reserved

cādence°

### Agenda

- Crosstalk in differential buffers

- Overview of Crosstalk Cancellation block

- Need for Adaptive Crosstalk Cancellation

- AMI Modeling of Crosstalk Cancellation block

- -Simulation results and Conclusion

10 © 2013 Cadence Design Systems, Inc. All rights reserved

# **Need for Adaptive Crosstalk Cancellation**

- Limitations:

- Coupling coefficient needs to be known to the receiver.

- Power required for crosstalk cancellation block

- Proposal

- Determine crosstalk coupling coefficient on the fly based on crosstalk activity.

- If the coupling coefficient is too small then the cancellation scheme can be switched off to save power.

11 © 2013 Cadence Design Systems, Inc. All rights reserved

cādence°

### Agenda

- Crosstalk in differential buffers

- Overview of Crosstalk Cancellation block

- Need for Adaptive Crosstalk Cancellation

- AMI Modeling of Crosstalk Cancellation block

- Simulation results and Conclusion

12 © 2013 Cadence Design Systems, Inc. All rights reserved

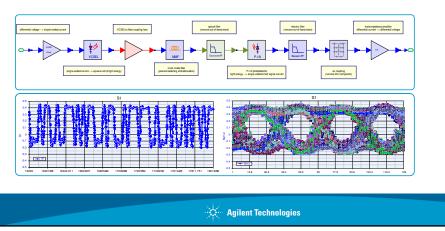

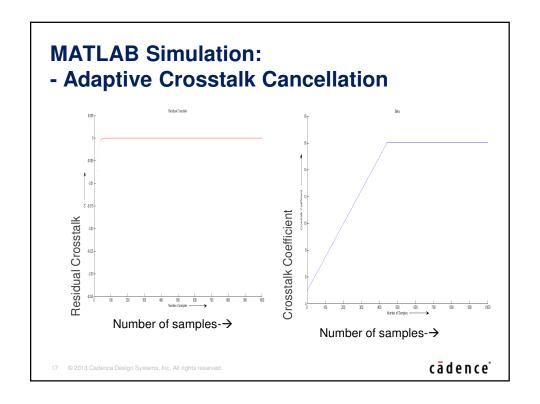

### **Adaptive CIJ Cancellation: AMI Implementation**

- Crosstalk is a function of channel length, spacing between channels and amount of data transitions. The number of data transitions varies with data pattern.

- Effectively, crosstalk between two interconnects keeps varying with data pattern.

- Effective coupling coefficient can be considered directly proportional to the transitions in the datapattern.

cādence<sup>\*</sup>

### Adaptive CIJ Cancellation: AMI **Implementation**

$$\begin{aligned} \frac{Z_1}{2}^+(\omega) &= Gh(\omega)(1 + \omega^2 \alpha_1 \beta_1) \frac{X_1}{2}(\omega) + \frac{j\omega Gh(\omega)(\alpha_1 - \beta_1) \frac{X_2}{2}(\omega)}{G_i &= \frac{1}{1 + sR_iC_i} | i = 1, 2 \end{aligned}$$

$$\beta_{i=R_iC_i}$$

- Training sequence is be used to train the crosstalk cancellation block

- Input is applied only at one channel, and the crosstalk signal is measured at the output of other channel

- Intent is to minimize (zero) the crosstalk at other channel

cādence"

# **Adaptive CIJ Cancellation: AMI Implementation using Varactor**

- Integrate the crosstalk signal to obtain Vf (Reversebias voltage) that would control the capacitance of the varactor (voltage dependent capacitor)

- Compute Ci using Varactor equation  $c_i = \frac{c_0}{\sqrt{1 + \frac{V_f}{V_{bi}}}}$

- With  $C_0$  (0 bias capacitance) = 0.025 and  $V_{\text{\tiny bi}}$  (Built in voltage potential)= 0.5 as constants.

- Ci modifies the crosstalk cancellation block Gi such that the crosstalk becomes zero.  $G_i = \frac{1}{1 + sR_iC_i} \Big| i = 1, 2$

15 © 2013 Cadence Design Systems, Inc. All rights reserved

cādence°

### Agenda

- Crosstalk in differential buffers

- Overview of Crosstalk Cancellation block

- Need for Adaptive Crosstalk Cancellation

- AMI Modeling of Crosstalk Cancellation block

- -Simulation results and Conclusion

16 © 2013 Cadence Design Systems, Inc. All rights reserved

## Conclusion

- At higher data-rates, crosstalk is becoming issue for differential buffers.

- Crosstalk induced jitter can be cancelled by crosstalk cancellation block

- Since crosstalk jitter is pattern dependent, it is important that crosstalk cancellation adapts itself based on data-induced jitter

20 © 2013 Cadence Design Systems, Inc. All rights reserved

21 © 2013 Cadence Design Systems, Inc. All rights reserved

cādence<sup>\*</sup>

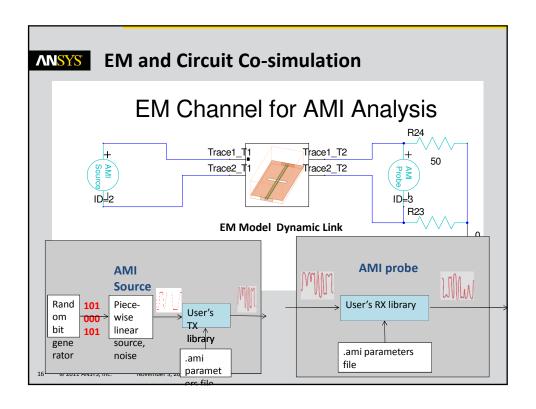

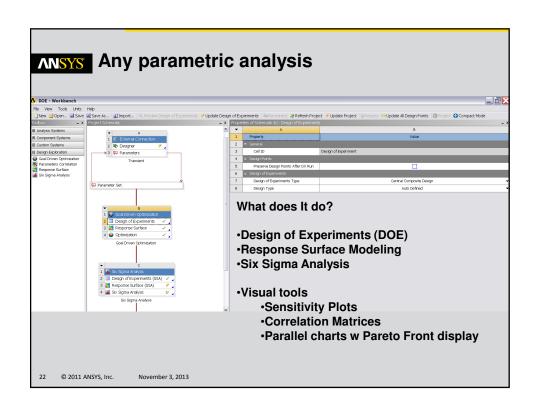

# ANSYS High speed Challenges Today

- (1) High Speed Data Rate Issue

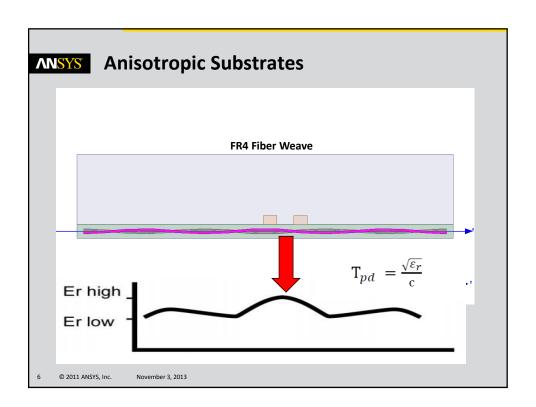

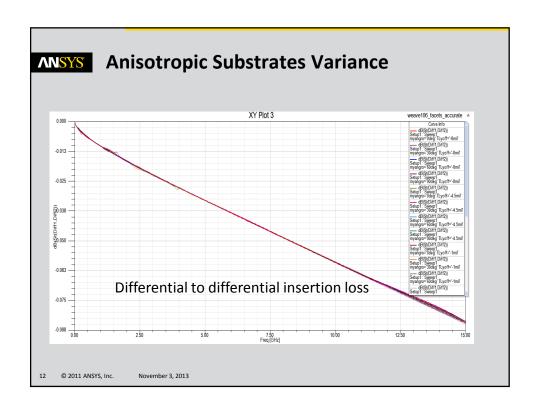

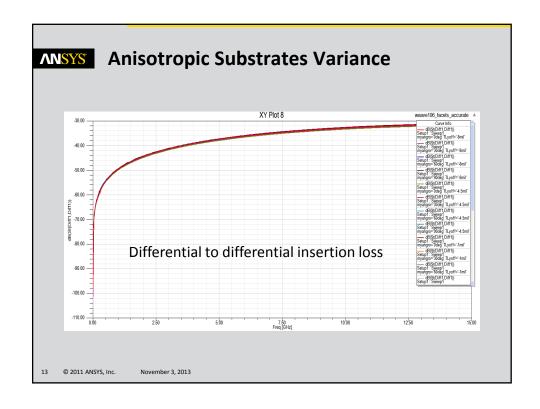

- (2) Anisotropic Substrates Variance

- (3) FEM solution to analysis Anisotropic Substrates Variance

- (4) Anisotropic Substrates Variance for IBIS-AMI Simulation

- (5) DOE Solution

© 2011 ANSYS, Inc.

November 3, 2013

### **ANSYS**

### **High speed IO Challenges Today**

As serial links become faster and more complex, it is ever more challenging to model the silicon in an accurate and efficient manner.

### Models/Simulator need to handle current challenges:

- Need to accurately handle very high data rates

- Simulate large number of bits to achieve low BER

- Non-linear, Time Variant Systems

- TX/RX equalization

- Specific Data patterns and coding schemes

- Non-convergence due to unstable models

- Channel Issue

© 2011 ANSYS, Inc.

November 3, 2013

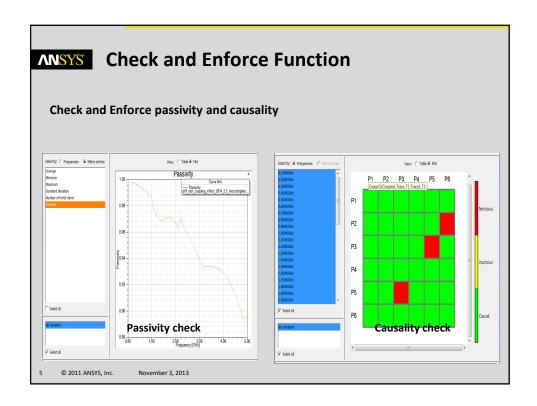

### **ANSYS** Circuit Simulation Issues with S-parameters

### **Passivity and Causality**

- Though S-parameters from a physics-based extraction tool should always be passive and causal, measured S-parameters often exhibit problems due to noise

- State-space model for S-parameter data guarantees causality of the circuit simulator model

- Two passivity enforcement algorithms

- Convex programming

- Perturbation

© 2011 ANSYS, Inc.

November 3, 2013

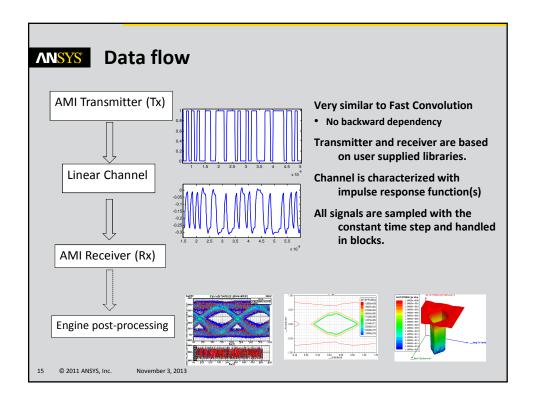

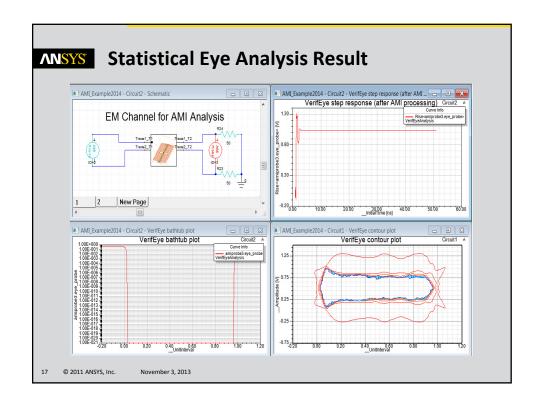

# Use the final impulse response from AMI analysis to run statistical eye analysis Linear modifications (AMI Init) from Tx and Rx AMI models taken into account AMI GetWave functionality cannot be used for statistical analysis as it is a purely time domain function November 3, 2013

### ANSYS Ho

### How to do that?

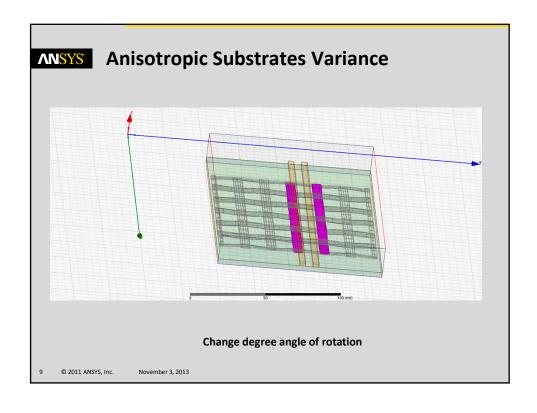

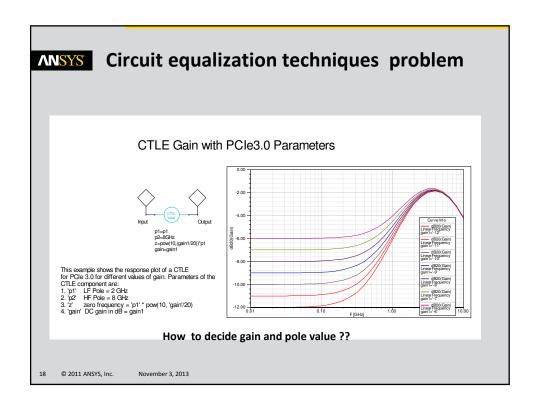

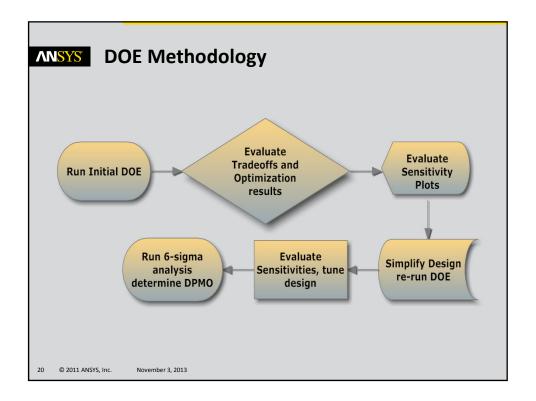

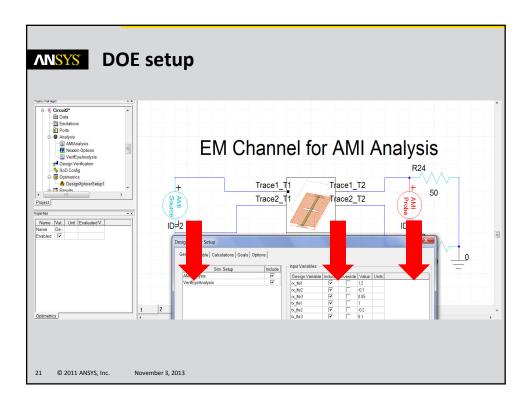

- Set up the DOE to sweep through the models to calculate the eye height and eye width for these cases

- The portions of the channel containing the PCB was modeled using a fullwave 3D electromagnetic extraction tool. A dynamic EM file was used to capture the channel's behavior. There are several variations of this structure that we want to include in the sensitivity analysis.

- To illustrate the results of this sensitivity analysis, we present sweeping of two of the variables: Change degree angle of rotation and equalization parameters

19 © 2011 ANSYS, Inc.

November 3, 2013

### **ANSYS**

### Why Response Surface Modeling?

- Response Surface Modeling enables the designer to model and consider all

aspects of a high speed channel design. Fit a statistical model to outputs of the

design as a function of the change in input variables. A DOE table is used to

select design points to solve explicitly for and the statistical model so to speak,

"fills in the gaps"

- Optimized conditions and worst case scenarios are obtainable within the set of all

possible design combinations within a realistic simulation timeframe.

- For example, this case, consider 8 variables or "factors", if each variable has only 5 variations or "levels" we are looking at a huge number of possible combinations in order to find optimal solutions and or worst case scenarios.

$$Combinations = Levels^{Factors} = 5^{8}!!!!$$

23 © 2011 ANSYS, Inc.

November 3, 2013

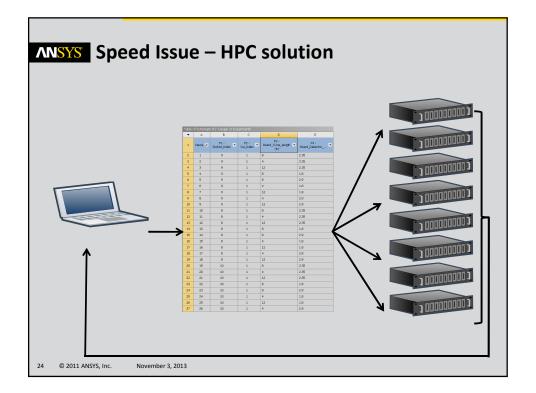

## **ANSYS** Summary

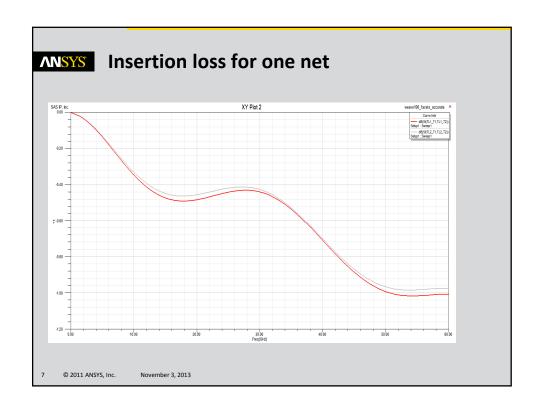

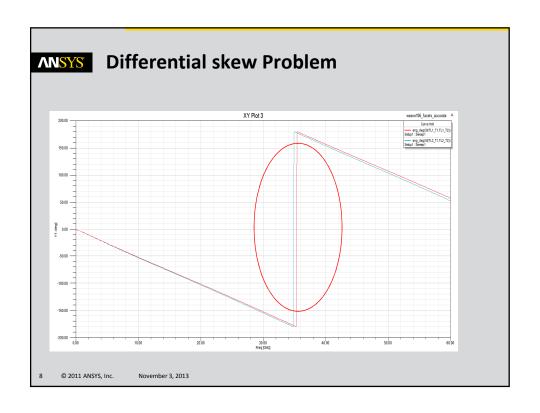

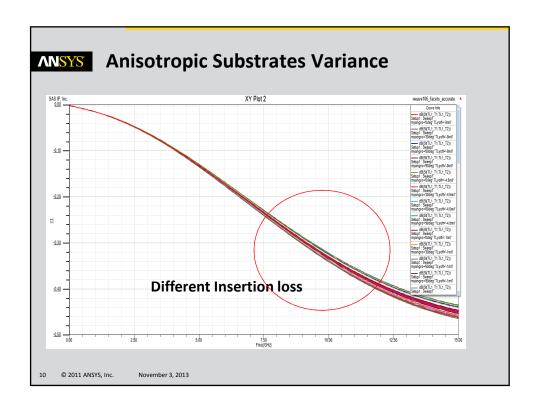

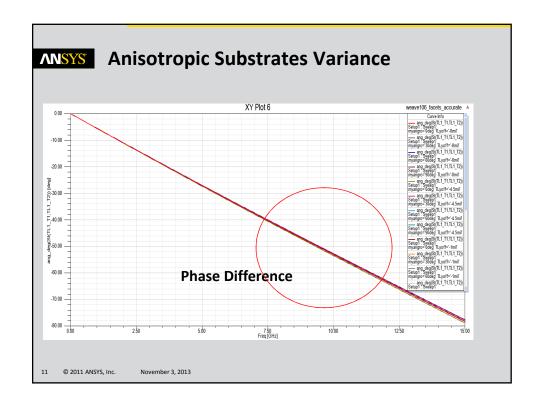

- In this presentation, we can see the anisotropic substrates variance of PCBs, it effects phase difference between the differential pair

- Simulations on both EM dynamic models and IBIS-AMI models are applied to produce eye diagrams to check channel variance performance

- Circuit equalization techniques are applied at the Tx and Rx receiver to improve channel performance

- It is more efficient to get best channel performance by DOE and HPC solution

25 © 2011 ANSYS, Inc. November 3, 2013