# DDR3 SI/PI Analysis using IBIS5.0

#### Shintaro Ohtani FUJITSU SEMICONDUCTOR LIMITED

Asian IBIS Summit Yokohama, Japan November 18, 2011

Copyright 2011 FUJITSU SEMICONDUCTOR LIMITED

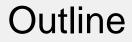

- Problems of DDR3 SI/PI Analysis

- DDR3 SI/PI Analysis using IBIS5.0

- Summary

- Expecting of IBIS

### DDR3 SI/PI Analysis using IBIS5.0

Summary

#### Expecting of IBIS

#### Contents

| IO Transistor Netlist                                | IBIS                               |  |

|------------------------------------------------------|------------------------------------|--|

| Detailed circuits and netlists<br>(transistor level) | I-V/V-T tables for IO final buffer |  |

#### **Trade-off**

|                          | IO Transistor Netlist                                            | IBIS                               |  |

|--------------------------|------------------------------------------------------------------|------------------------------------|--|

| Simulation<br>Time       | Slow<br>(Several to 10 times slower than IBIS)                   | Fast                               |  |

| Format                   | Bad<br>(Encryption and NDA are necessary)                        | Good<br>(Open format)              |  |

| EDA Tools<br>Utilization | Bad<br>(Specific simulator is necessary for<br>encrypted models) | Good<br>(Many SI/PI tools support) |  |

| Accuracy (SI)            | Good                                                             | Reasonably good                    |  |

| Accuracy (PI)            | Good                                                             | ?<br>(Supported SSO from Ver.5.0)  |  |

#### We have evaluated an ability of IBIS5.0 in terms of SI/PI.

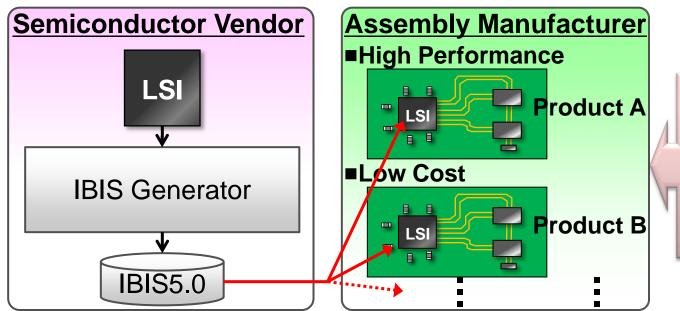

#### **IBIS5.0** Generation

# DDR3 SI/PI Analysis using IBIS5.0

#### Summary

#### Expecting of IBIS

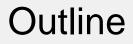

#### **Evaluation Environment**

| Item                                             | Explanation                            |  |

|--------------------------------------------------|----------------------------------------|--|

| CHIP                                             | 65nm DDR3 Interface Test Chip 16bit    |  |

| (mounted on Socket)                              | Data Rate : 1333Mbps                   |  |

| PKG                                              | Wire Bond BGA 4Layer 900ball 31mmx31mm |  |

| PCB                                              | 6Layer                                 |  |

| DRAM                                             | DDR3 SDRAM 8bitx2 on Board             |  |

| (mounted on Probe Adapter) (Fly-by architecture) |                                        |  |

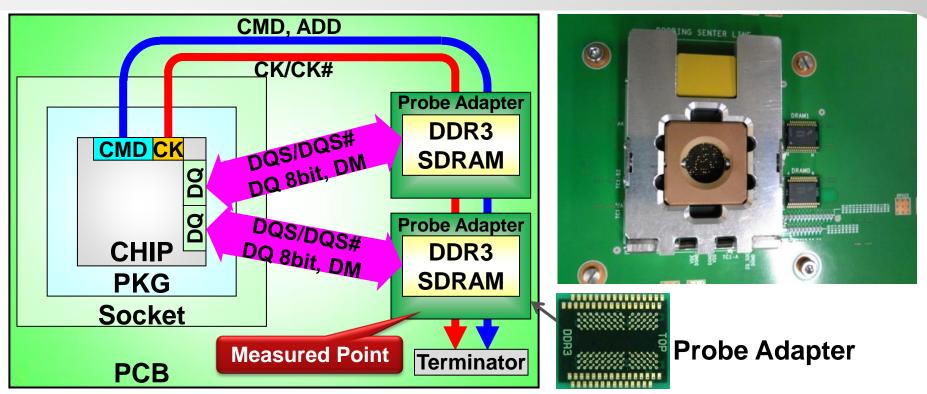

#### Validity of Simulation Model

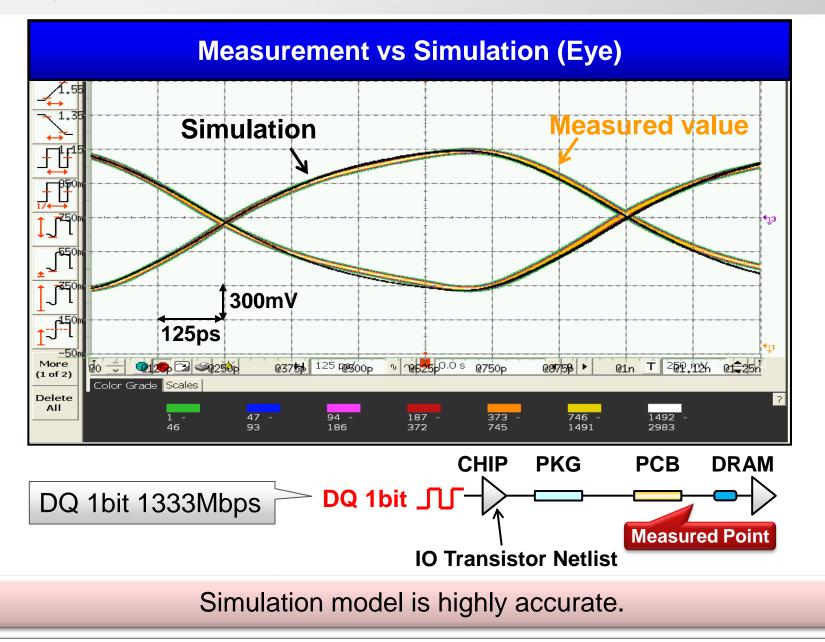

#### IBIS4.2 vs IBIS5.0

Characterizes currents from the supply rail through the buffer, as the buffer switches into a known load. It can show accurately driving current of IO.

#### ISSO PU / ISSO PD (BIRD98)

Characterizes buffer current modulation due to supply variation. It can show a change of driving current by voltage fluctuation.

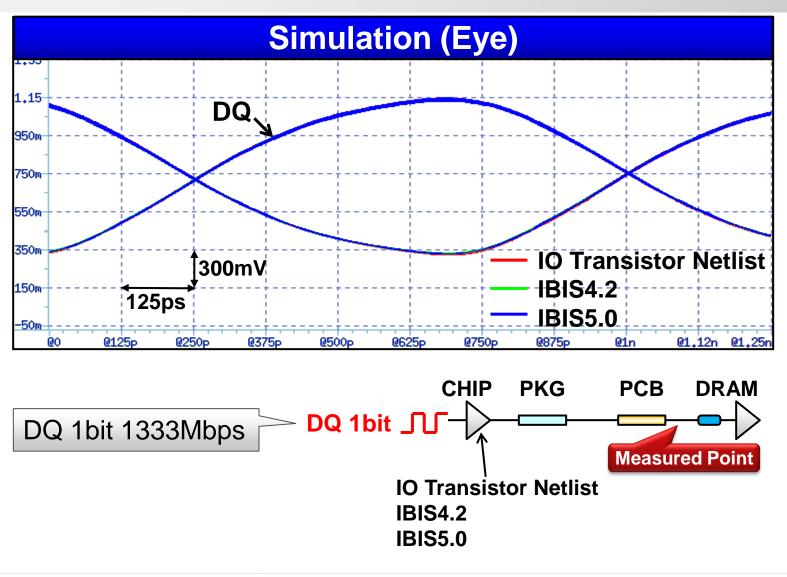

#### DDR3 SI Analysis using IBIS5.0

Both IBIS4.2 and IBIS5.0 are highly accurate.(in case SI analysis)

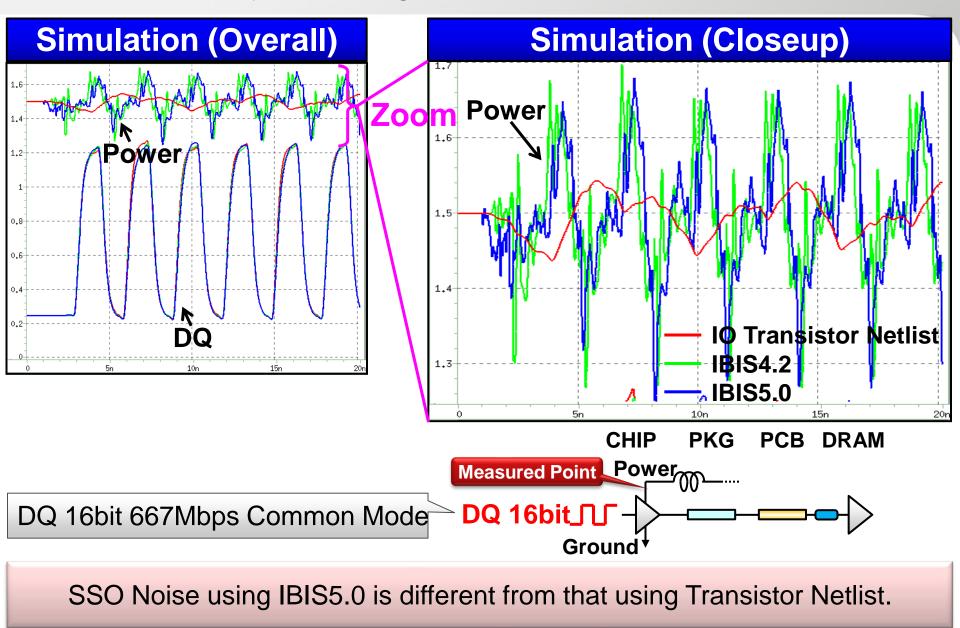

DDR3 PI Analysis using IBIS5.0 (SSO Noise)

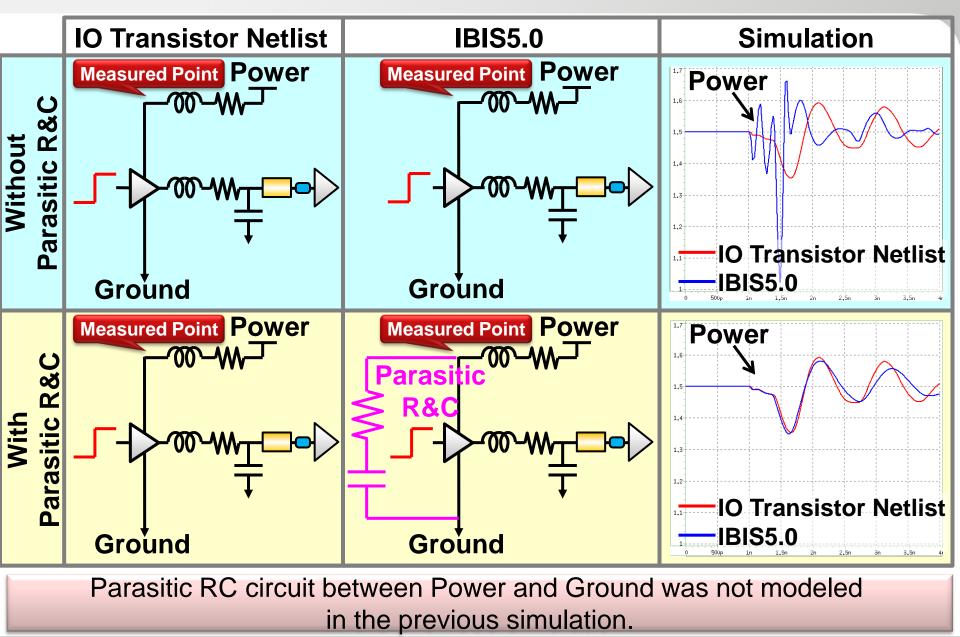

#### Reason that SSO Noise is different

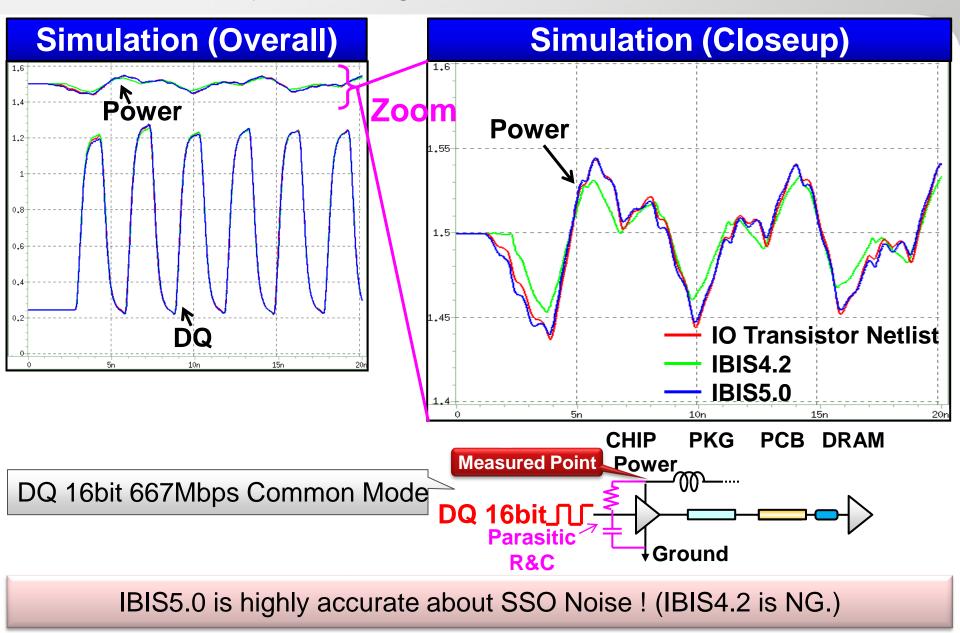

DDR3 PI Analysis using IBIS5.0 (Improved)

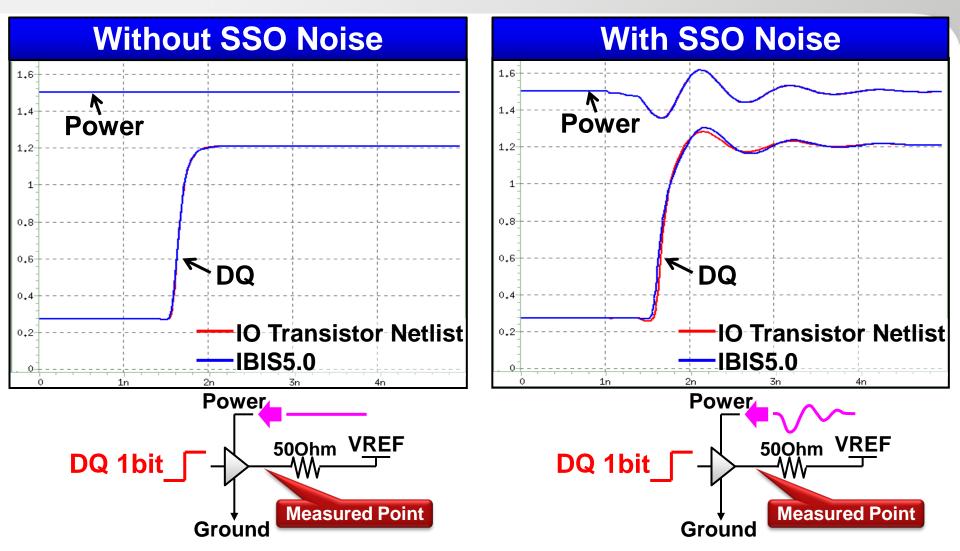

#### DDR3 PI Analysis using IBIS5.0 (Signal)

IBIS5.0 can show signal distortion related to SSO Noise.

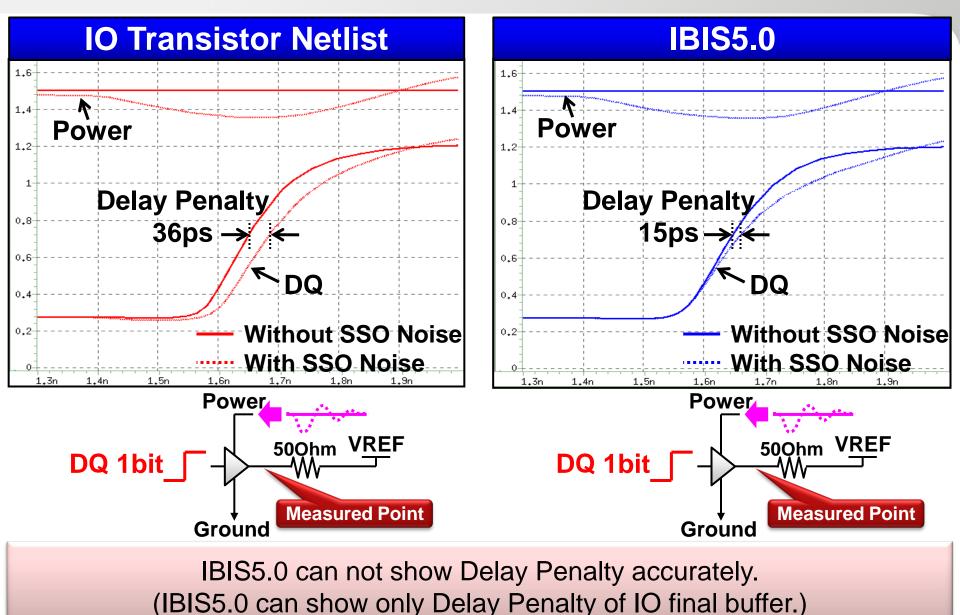

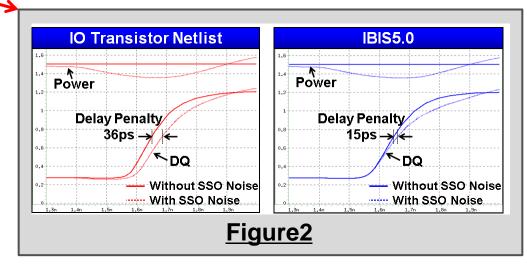

#### DDR3 PI Analysis using IBIS5.0 (Delay Penalty)

# DDR3 SI/PI Analysis using IBIS5.0

### Summary

#### Expecting of IBIS

### Summary

| ltem                                | IO Transistor Netlist | IBIS5.0    | IBIS4.2    |  |  |

|-------------------------------------|-----------------------|------------|------------|--|--|

| SI (Ideal Power)                    | 0                     | 0          | 0          |  |  |

| PI (SSO Noise)                      | 0                     | 0          | ×          |  |  |

| PI (Signal)                         | 0                     | 0          | ×          |  |  |

| PI (Delay Penalty)                  | 0                     | Δ          | ×          |  |  |

| Sim. time %1                        | 1020 minutes          | 24 minutes | 24 minutes |  |  |

| %1. 50ns Transient Analysis97% Down |                       |            |            |  |  |

If we can show Delay Penalty accurately in IBIS5.0 ...

We can execute SI/Timing analysis that includes PI influence accurately and shortly !

- Problems of DDR3 SI/PI Analysis

- DDR3 SI/PI Analysis using IBIS5.0

- Summary

- Expecting of IBIS

# Expecting of IBIS

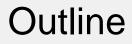

#### Problems in IBIS5.0

- It's impossible to define Power/Ground LCR of PKG in IBIS5.0

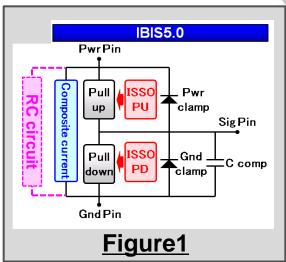

- Parasitic RC circuit doesn't exist in a circuit defined as IBIS5.0(Refer to Figure1) ——

- IBIS5.0 can not show IO Delay Penalty accurately (Refer to Figure2)

Please improve above-mentioned problems in IBIS5.0.

# FUJTSU

shaping tomorrow with you