Supporting External circuit as Spice or Sparameters in conjunction with I-V/V-T tables

Kent Dramstad, Adge Hawes IBM Microelectronics

Taranjit Kukal, Feras Al-Hawari, Ambrish Varma, Terry Jernberg Cadence Design Systems, Inc.

Presented by: Yukio Masuko, Cadence Design Systems, Inc. (Previously presented at Asian IBIS Summit on November 15, 2011)

Asian IBIS Summit Yokohama, Japan November 18, 2011

- Requirement

- Current Limitations of [External Circuit]

## Solution

- Supporting S-parameters in [External Circuit] (BIRD144)

- Simulating [External Circuit] in conjunction with I-V/V-T tables (BIRD145)

Summary

## Current Limitations of [External Circuit]

### Solution

- Supporting S-parameters in [External Circuit]

- Simulating [External Circuit] in conjunction with I-V/V-T tables

# cādence<sup>®</sup>

- At high frequencies, we need ways over and above I-V, V-T tables and AMI to model the buffer.

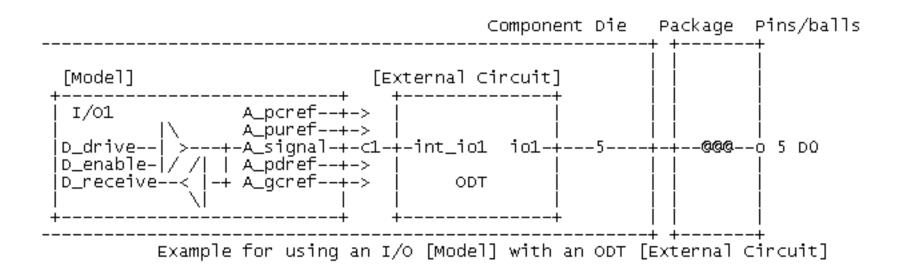

- On DIE Terminations (ODT) that vary with frequencies need to be expressed as S-parameters or RLGC Spice files

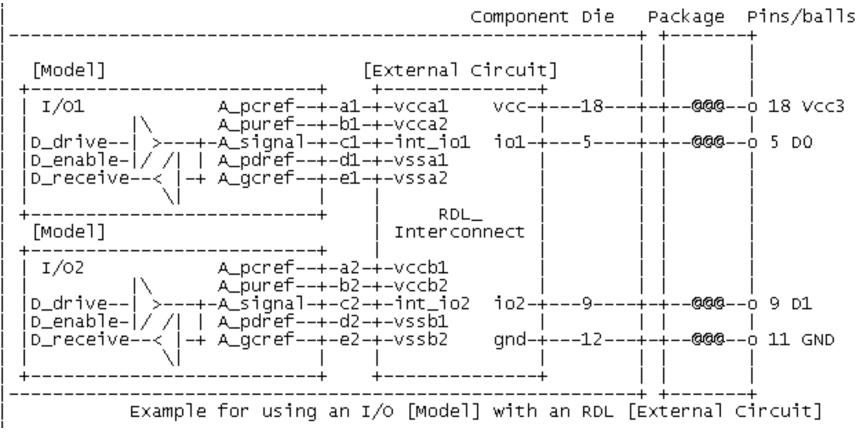

- On DIE Re-distribution layer (RDL) parasitics become significant and vary with frequencies and hence have to be expressed as S-parameters

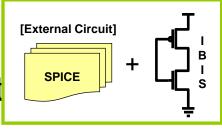

- Analog portion of IO-buffer get expressed as Spice as against I-V/V-T curve; S-parameters get used to describe transfer characteristics of linear IO-buffer amplifiers.

- At high frequencies, we need ways over and above I-V, V-T tables and AMI to model the buffer.

- Some algorithmic portion of IO-buffer model could be expressed as behavioral Spice to augment AMI code

- Example: 'if-then-else kind of spice' to pick right sub-circuit based on parameter values/processes

- Example: Modeling continuous filters as behavioral spice to augment digital filters in AMI code

# - Various Cases that need to be covered

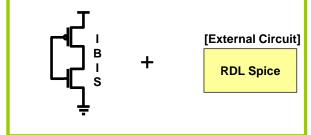

Case 1

Simulating RDL parasitics in conjunction with I-V/V-T tables

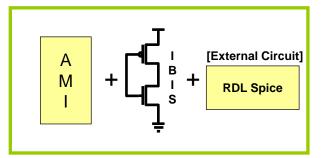

Simulating RDL parasitics in conjunction with I-V/V-T tables and AMI

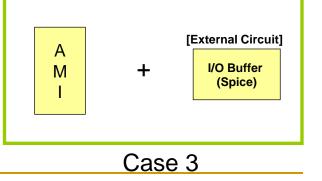

Simulating AMI with IO-buffer expressed as Spice

## Current Limitations of [External Circuit]

### Solution

- Supporting S-parameters in [External Circuit]

- Simulating [External Circuit] in conjunction with I-V/V-T tables

## Current Limitations

- [External Circuit]

- Today, S-parameters have to be wrapped into Spice models (vendor specific) and then used under [External Model/Circuit] Keyword.

- On similar lines, BIRDs 116-118 propose that Touchstone file name can be parameterized for the IBIS-ISS sub-circuit, which means that IBIS-ISS wrapper could be written for the S-parameter element.

NEED: Extend support for direct usage of Sparameters

# Current Limitations

- [External Circuit]

- The current [External Circuit] and [Circuit Call] usage rules do not allow the direct interconnection and instantiation of existing IBIS I/O models with the rest of the [External Circuit] blocks. Traditionally, users either use Spice or I-V/V-T tables.

- NEED: Extend use of [External Circuit] keyword to point to Spice sub-circuits that augment I-V/V-T data for complete characterization of IO-buffer.

## Current Limitations

# - [External Circuit]

- In order for a model developer to use an IBIS I/O model in an [External Circuit] the following steps need to be followed:

- Develop SPICE like wrappers in which the corresponding typ, min, and max IBIS I/O sub-circuits are instantiated

- Develop an [External Circuit] to point to the wrapper subcircuits

- □ Use the [Circuit Call] keyword to call the [External Circuit].

- These usage rules are cumbersome especially when the developer can just directly call the desired IBIS I/O model without the need to develop a SPICE like wrapper as well as an [External Circuit] section.

### Current Limitations of [External Circuit]

## Solution

Supporting S-parameters in [External Circuit] (BIRD144)

Simulating [External Circuit] in conjunction with I-V/V-T tables

Summary

# Solution: Leveraging [External Model/Circuit] to Support Package S-parameters

- For support of package S-parameters:

- IBIS model should have Keywords to support Touchstone

S-parameters under Package section, with fields to

- Point to Touchstone file from the Package section

- Provide port-mapping of IO-buffer pins to S-parameter ports

- R/L/C values should be ignored by SI tools if S-parameter file is used

- For support of S-parameters when representing elements beyond package parasitics: This can be achieved through use of [External Model] keyword that directly instantiates Touchstone file

- Positioning S-parameters as a method to completely define IO-buffer model or portions of IO-buffer requires support for:

- Direct support of S-parameters without the need for wrapping

- Port mapping of S-parameters

- Corners beyond typ/min/max to provide flexibility of choosing various S-parameter files under different conditions

#### Support for Language 'Touchstone' with port-map

Example of True Differential [External Model] using TOUCHSTONE: [Model] Ext\_TOUCHSTONE,\_Diff\_Buff Model\_type I/o\_diff Rref\_diff = 100 Other model subparameters are optional min  $ma \times$ typ 3.3 [Voltage Range] 3.0 3.6 [Ramp] dv/dt\_r 1.57/0.36n 1.44/0.57n 1.73/0.28n dv∕/dt\_f 1.57/0.35n 1.46/0.44n 1.68/0.28n [External Model] anguage TOUCHSTONE Corner corner\_name file\_name circuit\_name (.subckt name) тур Min diffio.s8p corner NA corner diffio.s8p NA Corner мах diffio.s8p NA Ports List of port names (in same order as in TOUCHSTONE) Ports A\_signal\_pos A\_signal\_neg my\_receive my\_drive my\_enable Ports A\_puref A\_pdref A\_pcref A\_gcref A\_extref my\_ref A\_gnd vlow vhigh trise tfall corner\_name D\_to\_A d\_port port1 port2 з. 3 0.5n Didrive my\_drive my\_ref 0.0 0.3n тур Min D\_to\_A my\_drive 0.0 D\_to\_A D\_drive my\_ref 3.0 0.6n 0.3n mý\_ref D\_drive my\_drive 0.0 3.6 0.4n 0.3n D\_to\_A Max D\_enable my\_enable my\_ref 0.0 3.3 0.5n 0.3n D\_to\_A тур D\_enable my\_enable D\_to\_A my\_ref 0.0 3.0 0.6n 0.3n Min D\_to\_A D\_enable my\_enable my\_ref 0.0 3.6 0.4n 0.3n Ma× port1 vhiqh A\_to\_D d\_port port2 vlow. corner\_name D\_receive A\_signal\_neg A\_signal\_pos -200m 200m тур Min A\_to\_D -200m 200m A to D D\_receive A\_signal\_pos A\_signal\_neg A\_to\_D D\_receive A\_signal\_pos A\_signal\_neg -200m 200m Max [End External Model]

#### Picking different S-parameter files for different corners

Example of True Differential [External Model] using TOUCHSTONE: [Model] Ext\_TOUCHSTONE,\_Diff\_Buff Model\_type I/o\_diff Rref\_diff = 100 Other model subparameters are optional min  $ma \times$ typ 3.3 [Voltage Range] 3.0 3.6 [Ramp] dv/dt\_r 1.57/0.36n 1.44/0.57n 1.73/0.28n dv⁄/dt\_f 1.57/0.35n 1.68/0.28n 1.46/0.44n [External Model] Language TOUCHSTONE circuit\_name (.subckt name) Corner corner\_name file\_name Corner тур Min diffio.s8p NA Corner diffio.s8p NA Corner Max diffio.s8p NA PORTS LIST OF PORT names (IN same order as IN TOUCHSTONE) Ports A\_signal\_pos A\_signal\_neg my\_receive my\_drive my\_enable Ports A puref A pdref A pcref A gcref A extref my ref A gnd vlow vhigh trise tfall corner\_name D\_to\_A d\_port port1 port2 з.з 0.5n Didrive my\_drive my\_ref 0.0 0.3n тур Min D\_to\_A 0.6n D\_to\_A D\_drive my\_drive my\_ref 0.0 3.0 0.3n mý\_ref 0.4n D\_to\_A D\_drive my\_drive 0.0 3.6 0.3n Ma× D\_enable my\_enable my\_ref 0.0 3.3 0.5n 0.3n D\_to\_A тур D\_enable my\_enable 3.0 0.3n D\_to\_A my\_ref 0.0 0.6n Min D\_to\_A D\_enable my\_enable my\_ref 0.0 3.6 0.4n 0.3n Ma× port1 vhiqh A\_to\_D d\_port port2 vlow. corner\_name 'A\_signal\_neg D\_receive A\_signal\_pos -200m 200m тур Min A\_to\_D A\_signal\_pos A\_signal\_neg -200m 200m A\_to\_D D\_receive A\_to\_D D\_receive A\_signal\_pos A\_signal\_neg -200m 200m Max [End External Model]

Supporting user-defined corners – each user-defined corner maps to typ/min/max IBIS corners

```

Example [External Model] using TOUCHSTONE with 2 userdef corners:

```

```

[Model] ExLinearBufferTouchstoneWithTwoUserDefCorners

Model_type Output

Other model subparameters are optional

min

typ

3.3

max.

.

Voltage Rangel

3.0

3.6

[Ramp]

dv/dt_r

1.57/0.36n

1.44/0.57n

1.73/0.28n

dv/dt_f

1.57/0.35n

1.46/0.44n

1.68/0.28n

[External Model]

Language TOUCHSTONE

Corner corner_name file_name

circuit_name

buffer_typ.s2p

Corner

тур

NA

Min

buffer_min.s2p

Corner

NA

Corner

Max.

buffer max.s2p

NA

Parameters List of parameters

Parameters MinNumber MaxNumber

User_defined_corner user_defined_corner_name parameter_name parameter_value file_name corner_name

-User_defined_corner

buffer_min1.s2p

Min1

MinNumber

1

Min

User_defined_corner

buffer_max1.s2p

MaxNumber

Max1

1

Мах

```

#### Use in [External Model] and [External Circuit]

Example [External Model] using /OUCHSTONE: Example [External Circuit] using TOUCHSTONE: [Model] EXBufferTOUCHSTONE [External Circuit] BUFF-TOUCHSTONE Model\_type I/O Language TOUCHSTONE lvinh = 2.0 ∨inl = 0.8 Corner corner\_name file\_name circuit\_name (.subckt name) buffer\_typ.s9p NA тур Corner Other model subparameters are optional Min buffer\_min.s9p NA Corner buffer\_max.s9p NA Corner мах min typ, max [Voltage Range] 3.0 3.6 Ports List of port names (in same order as in TOUCHSTONE) Ports A\_signal int\_in int\_en int\_out A\_control [Ramp] Ports A\_puref A\_pdref A\_pcref A\_qcref 1.57/0.36n 1.44/0.57n 1.73/0.28n ldv/dt\_r 1.46/0.44n dv/dt\_f 1.57/0.35n 1.68/0.28n D\_to\_A d\_port port1 port2 vlow vhigh trise tfall corner\_name D\_drive int\_in my\_qcref 0.0 3.3 0.5n 0.3n Typ D\_to\_A [External Model] D\_drive int\_in my\_gcref 0.0 3.0 D\_to\_A 0.6n 0.3n Min Language TOUCHSTONE D\_drive int\_in my\_gcref 0.0 3.6 0.4n 0.3n Max D\_to\_A D\_to\_A D\_enable int\_en my\_qnd 0.0 3.3 0.5n 0.3n тур Corner corner\_name file\_name circuit\_name (.subckt D\_enable int\_en mý\_qnd 0.0 3.0 0.6n 0.3n D\_to\_A Min buffer\_typ.s7p NA тур ICorner D\_to\_A D\_enable int\_en my\_gnd 0.0 3.6 0.4n 0.3n Max buffer\_min.s7p NA lcorner Min. Corner Max. buffer\_max.s7p NA A\_to\_D d\_port port1 port2 vlow vhigh corner\_name D\_receive int\_out my\_acref 0.8 2.0 | Ports List of port names (in same order as in TOUCHSTONE)<sup>A\_to\_D</sup> тур D\_receive int\_out my\_gcref 0.8 2.0 Mìn A\_to\_D Ports A\_signal my\_drive my\_enable my\_receive my\_ref D\_receive int\_out my\_gcref 0.8 2.0 A\_to\_D Мах Ports A\_puref A\_pdref A\_pcref A\_qcref A\_extref vlow vhigh trise tfall[End External Circuit] D\_to\_A d\_port port1 port2 D\_drive my\_drive my\_ref 0.0 3.3 0.5n 0.3n D\_to\_A тум D\_to\_A D\_enable my\_enable A\_gcref 0.0 3.3 0.5n 0.3n тур vlow vhigh corner\_name A\_to\_D d\_port port2 port1 A\_to\_D D\_receive my\_receive my\_ref 0.8 2.0 TVP Note: A\_signal might also be used instead of a user-defined interface port for measurements taken at the die pads [End External Model]|

Current Limitations of [External Circuit]

## Solution

Supporting S-parameters in [External Circuit]

Simulating [External Circuit] in conjunction with I-V/V-T tables(BIRD145)

Summary cādence<sup>®</sup>

Ability to connect External Circuit to IBIS I/O model. The External Circuit could represent RDL parasitics, portion of active I/O buffer, some algorithmic part of I/O buffer.

[Pin] signal\_name model\_name R\_pin L\_pin C\_pin

|   | 1  | RAS0#     | Buffer1 | 200.0m 5.0nH 2.0pF |

|---|----|-----------|---------|--------------------|

|   | 2  | RAS1#     | Buffer2 | 209.0m NA 2.5pF    |

|   | 3  | EN1#      | Input1  | NA 6.3nH NA        |

| • | 4  | A0        | 3-state |                    |

|   | 5  | <b>D0</b> | I/O1    |                    |

|   | 6  | RD#       | Input2  | 310.0m 3.0nH 2.0pF |

| • | 7  | WR#       | Input2  |                    |

| • | 8  | A1        | I/O2    |                    |

| • | 9  | D1        | I/O2    |                    |

|   | 10 | GND       | GND     | 297.0m 6.7nH 3.4pF |

|   | 11 | RDY#      | Input2  |                    |

| • | 12 | GND       | GND     | 270.0m 5.3nH 4.0pF |

HERE DO, D1 are to be modeled as I/O1, I/O2 buffers followed by RDL Spice and represent a differential buffer

I/O1 and I/O2 are followed by RDL Spice model

| [Node Declarations]                                 | Must appear before any [Circuit Call] or [Model Call] keyword                                                                                                          |  |  |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <br>  Die nodes<br>a1 b1 c1 d1 e1<br>a2 b2 c2 d2 e2 | List of die nodes representing signals that connect models                                                                                                             |  |  |

| l<br>[End Node Declaratio                           | ons]                                                                                                                                                                   |  |  |

| the tool to instantiate                             | 01" must be present in the IBIS file in order to enable<br>and connect the called model "as usual" based on<br>es as well as the subparameters under the corresponding |  |  |

| [Model Call] I/O1                                   | Instantiates [Model] named "I/O1"                                                                                                                                      |  |  |

| ا<br>  mapping port د<br>ا                          | oad/node                                                                                                                                                               |  |  |

| Port_map A_pcref                                    | a1   Port to internal node connection                                                                                                                                  |  |  |

| Port_map A_puref                                    | b1   Port to internal node connection                                                                                                                                  |  |  |

| Port_map A_signal                                   | c1   Port to internal node connection                                                                                                                                  |  |  |

| Port_map A_pdref                                    | d1   Port to internal node connection                                                                                                                                  |  |  |

| Port_map A_gcref                                    | e1   Port to internal node connection                                                                                                                                  |  |  |

| <br>[End Model Call]                                |                                                                                                                                                                        |  |  |

|                                                     |                                                                                                                                                                        |  |  |

- INOTE:

- A [Model] named "I/O2" must be present in the IBIS file in order to enable

- I the tool to instantiate and connect the called model "as usual" based on

- I the I-V and T-V curves as well as the subparameters under the corresponding

- [Model] section.

- [Model Call] I/O2

#### | Instantiates [Model] named "I/O2"

| Port to internal node connection

I mapping port

pad/node

a2

e2

- Port

- Port\_map A\_pcref

- Port\_map A\_puref b2

- Port\_map A\_signal c2

- Port\_map A\_pdref d2

- Port\_map A\_gcref

- - [End Model Call]

- [Circuit Call] RDL\_Interconnect | Instantiates [External Circuit] named "RDL\_Interconnect"

mapping port pad/node

18

5

9

b1

c1

a2

d2

e2

- Port\_map vcc

- Port map gnd

- Port map io1

- io2 Port map

- Port map vcca1 Port\_map vcca2

- Port\_map int\_io1

- Port\_map vssa1

- Port map vssa2

- Port map vccb1

- Port\_map vccb2

- Port\_map int\_io2

- Port\_map vssb1

- Port map vssb2

- - [End Circuit Call]

- | Port to implicit pad connection

- 12 | Port to implicit pad connection

- Port to implicit pad connection

- Port to implicit pad connection

- Port to internal node connection a1

- Port to internal node connection

- Port to internal node connection

- d1 Port to internal node connection e1

- Port to internal node connection

- Port to internal node connection

- b2 Port to internal node connection c2

- Port to internal node connection

- Port to internal node connection

- Port to internal node connection

# Agenda

## Requirement

## Current Limitations of [External Circuit]

### Solution

- Supporting S-parameters in [External Circuit]

- Simulating [External Circuit] in conjunction with I-V/V-T tables

Summary

cādence<sup>®</sup>

# Summary

- With increase in frequencies, we need enhanced usage of External Model / Circuit

- S-parameters are becoming common way to model portions of I/O buffers and package parasitics; Hence need to have direct support of S-parameter model under [External Model/Circuit]. This has been proposed as BIRD144

- Significant portion of I/O buffer gets modeled as Spice/Sparameters to augment the main analog buffer to capture the high frequency behavior; Hence need to have easy way to connect External Circuit to I-V/V-T table-model. *This has been proposed as BIRD145*

## BIRD144 and BIRD145 can be accessed at <u>http://www.eda.org/pub/ibis/birds/</u>

- The BIRDs would be considered and discussed by the IBIS open forum

- Other BIRDs will also be considered that might be alternatives or add-on to this proposal

# cādence<sup>®</sup>