Asian IBIS Summit Yokohama, Japan November 18, 2011

Brad Brim / Sigrity, Inc. Yutaka Honda / ATE Service Corp.

#### Outline

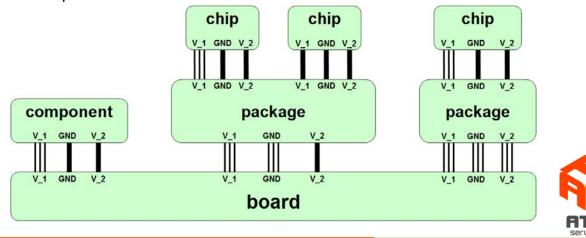

3D-SiP PDN analysis

Interference issues in PDN

PDN modeling strategy

- Model connectivity

- Case studies

## PDN in 3D-SiP

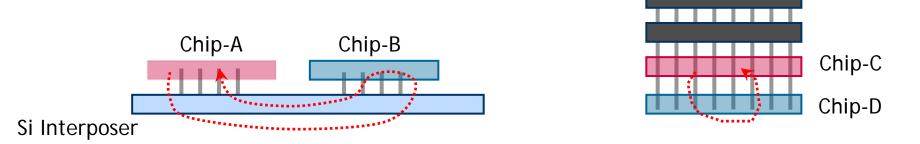

#### Distributed dies

Stacked dies

Shared/isolated PG mesh on Silicon Interposer

Vertical PG paths by TSV

Wirebond connections from package

## **Power Integrity Assessment**

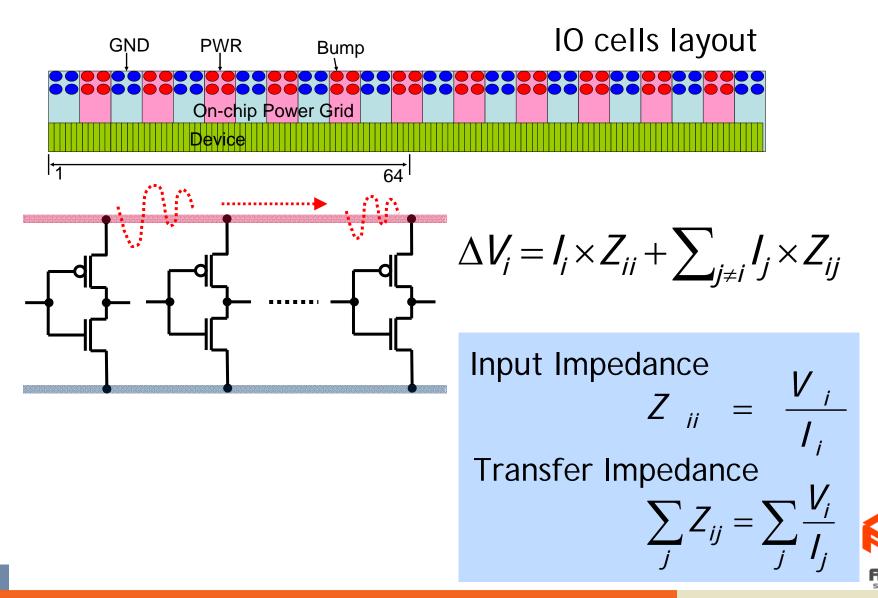

## Interference Issues in PDN

- Influence from adjacent circuits

- Die location dependency

- Coupling through Package

- Simulation needs to efficiently reflect conjunctions between those "elements."

# **Influence from Adjacent Circuits**

# **Die Location Dependency**

#### Transfer Impedance : ZBA < ZDC

#### **3D-SiP structure trade-off**

→ Wide IO band width with less power consumption

→ Tighter interaction between dies in a localized PDN

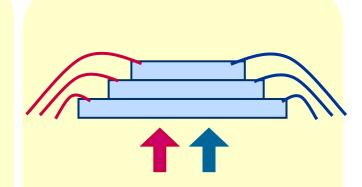

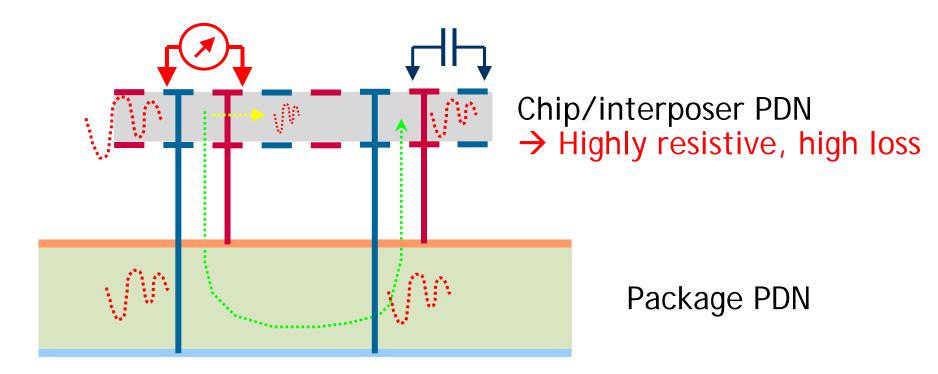

#### **Coupling through Package**

#### High loss chip PDN

- $\rightarrow$  Power rail noise is spread out thru package.

- $\rightarrow$  Effective area of on-chip decap is limited.

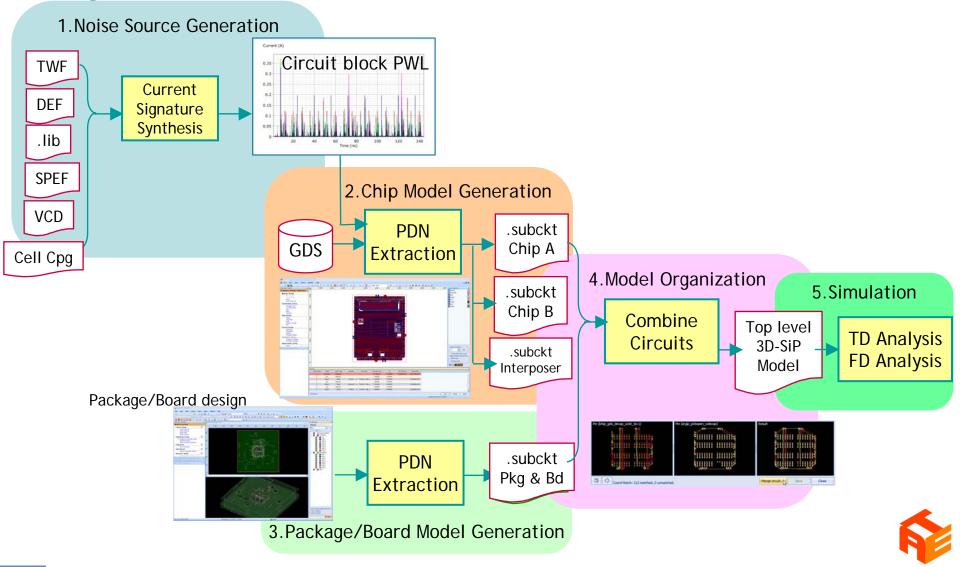

# **System-level Co-simulation Workflow**

SIGRITY

# **PDN Modeling Strategy**

#### Model resolution

## Chip-centric observation

# Model connectivity

#### **Model Resolution**

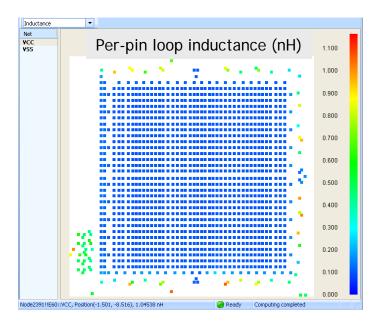

#### Pin location resolution

# Circuit (cell/block) placement resolution

Power/ground pin characteristics are sensitive to the structure.

- Simulation priority

- $\rightarrow$  accuracy with detailed placement

- → faster run time with rough floor plan

#### **Chip-centric Observation**

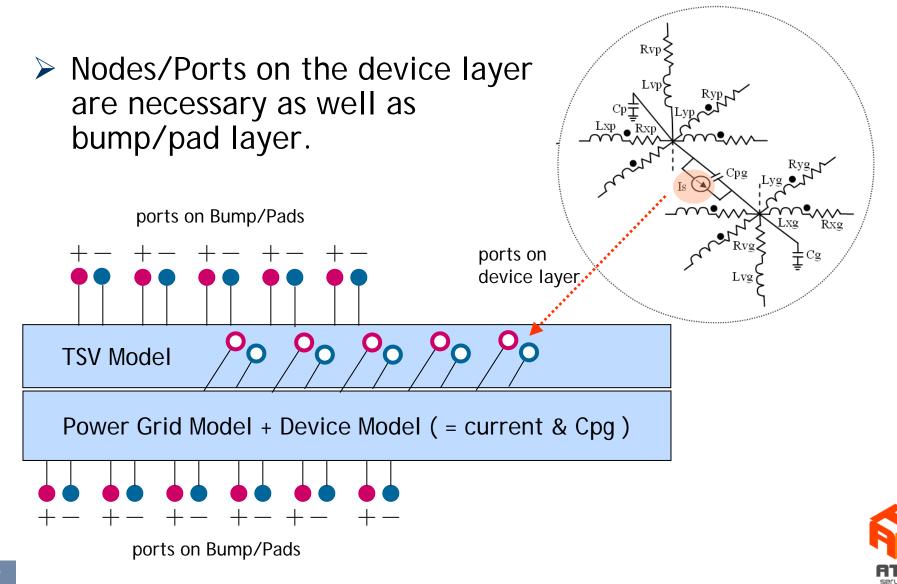

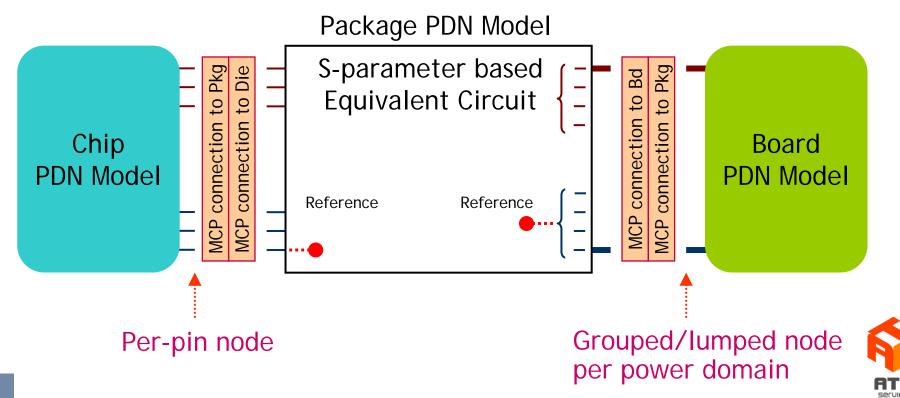

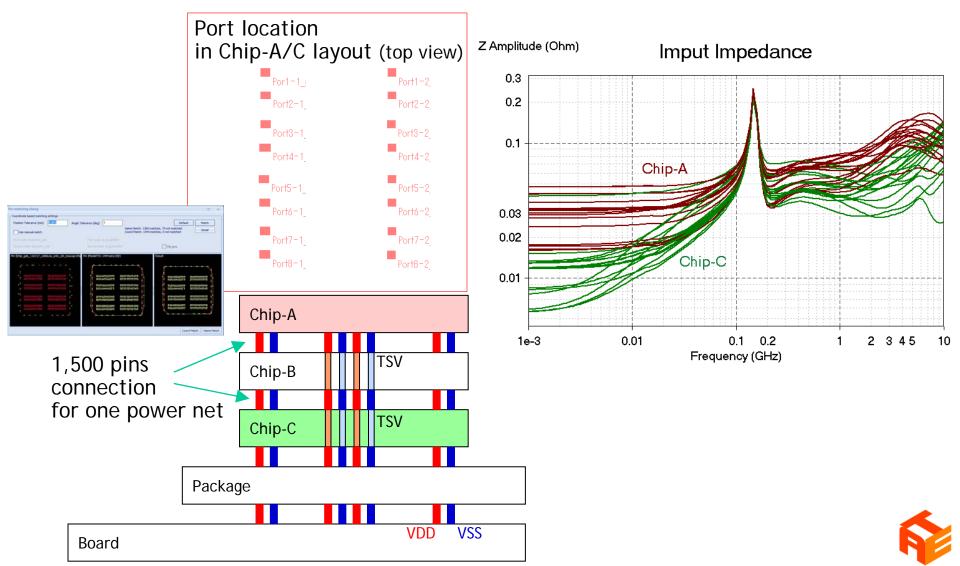

# Model Connectivity

- The model connection scheme affects simulation resolution and accuracy.

- Per-pin connection is important in order to predict localized propagation/distribution of PDN behavior of 3D-SiP.

|                               | MCP Editor (D:¥Y_)                                     | 2nd_Drive¥Sig | prity¥Invest | igation¥11 | 212 Large    | Pin Count M       | 1CP & CPM¥sig_CoD  | esign                               | TE2_die_M                        | ICP 🗆       | ×        |

|-------------------------------|--------------------------------------------------------|---------------|--------------|------------|--------------|-------------------|--------------------|-------------------------------------|----------------------------------|-------------|----------|

|                               | Internal Circuit: sig_CoDesign_WTEG_ATE2_die_MCP_sig_l |               |              |            |              |                   | Internal Circuit   | uit: sig_CoDesign_WTEG_ATE2_pkg_rec |                                  |             |          |

|                               | Connection: FSB                                        |               | 🔻 Туре       | : PCB      | Del          | Connection: die_t |                    | p                                   | ▼ Type:                          | ▼ Type: DIE |          |

|                               | Ckt Node(*)                                            | Net(*)        | X (mm)       | Y (mm)     | F            | in(*)             | Ckt Node(*)        | Net(*)                              | X (mm)                           | Y (mm)      |          |

|                               | FSB_0C04                                               | VDD_RX        | 29.7856      | 29.292     | ←            | 0C04              | die_top_0C04       | VDD_RX                              | 29.7856                          | 29.292      |          |

|                               | NodeGND                                                | GND_1         | 29.7856      | 29.4744    | ←            | 0C05              | NodeGND            | GND                                 | 29.7856                          | 29.4744     |          |

|                               | FSB_0C04                                               | VDD_RX        | 29.7856      | 29.6568    |              | 0C06              | die_top_0C04       | VDD_RX                              | 29.7856                          | 29.6568     |          |

|                               | NodeGND                                                | GND_1         | 29.7856      | 29.8392    | <del>~</del> | 0C07              | NodeGND            | GND                                 | 29.7856                          | 29.8392     |          |

|                               | FSB_0C04                                               | VDD_RX        | 29,7856      | 30.0216    | -            | 0C08              | die_top_0C04       | VDD_RX                              | 29,7856                          | 30.0216     |          |

|                               | NodeGND                                                | GND_1         | 29.7856      | 30.204     | <del>-</del> | 0C09              | NodeGND            | GND                                 | 29.7856                          | 30.204      |          |

|                               | FSB_0C04                                               | VDD_RX        | 29.7856      | 30.3864    | ←            | 0C10              | die_top_0C04       | VDD_RX                              | 29.7856                          | 30.3864     |          |

|                               | Node_GND                                               | GND_1         | 29.7856      | 30.5688    | -            | 0C11              | → Node_GND         | GND                                 | 29.7856                          | 30.5688     |          |

|                               | FS8_0C04                                               | VDD_RX        | 29.7856      | 30.7512    | ←            | 0C12              | die_top_0C04       | VDD_RX                              | 29.7856                          | 30.7512     | <b>T</b> |

| Example : Automat<br>for wrar |                                                        |               |              |            |              |                   |                    |                                     | Default<br>Detail<br>Coord Match |             |          |

|                               | Pin (sig_CoDesign_                                     | _ATE2_die_    | MCP_sig_CoE  |            | CoDesign     | _ATE2             | kg_reduced_sig_CoD | Result                              | Save                             |             | se       |

**Unified Protocol for Model Connections**

In order to achieve ...

- Automation in simulation setup.

→ ease of use, reduction of engineering time.

- Mixed simulation environment.

A various model resources and methodology.

#### **SIGRITY**

#### Example of Proposed MCP<sup>TM</sup> (Model Connection Protocol)

# **Connection Density Control**

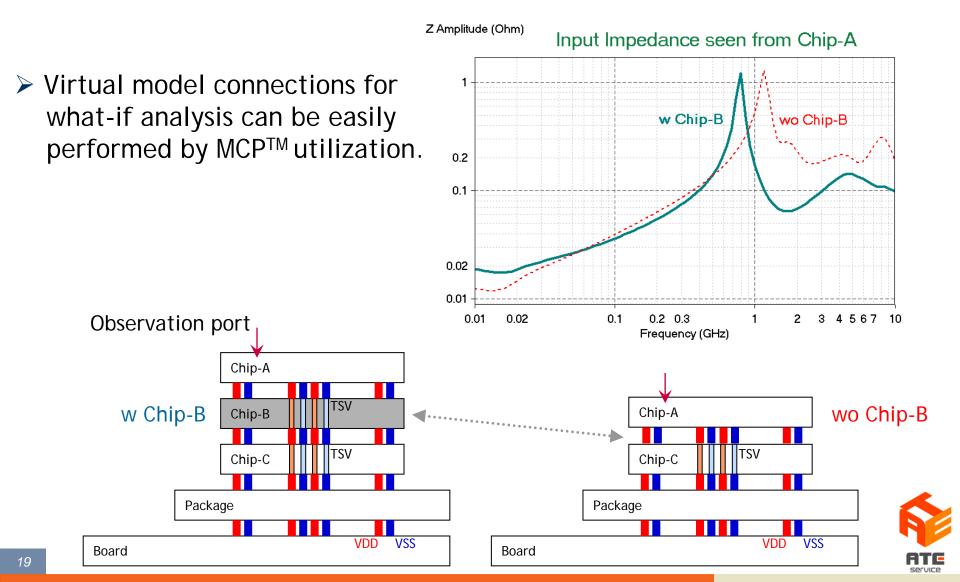

- ➤ The difference of node resolution between the models can be handled in MCP<sup>TM</sup>.

- But it is desired that a model have the the same pin resolution as the destination circuit.

# **Previous Discussions**

- *"Model Connection Protocols for Chip-Package-Board System-level Analysis"* Sigrity, Inc. IBIS Summit, DAC / July.28, 2009

- *"An Introduction to Model Connection Protocols"* Sigrity, Inc. IBIS Summit, DesignCon / Feb. 4, 2010

- <u>"Model Connection Protocol extensions for Mixed Signal SiP</u>" Cadence Design Systems, Inc. IBIS Summit, Tokyo / Nov. 15, 2010

#### **3D-SiP Case Studies :** Location dependency

SIGRI

#### **3D-SiP Case Studies :** Die stacking scheme

SIGR

# Thank You!