# DDR3 System Timing Budget Analysis by SI&PI Co-Simulation

Yi Bi, yi.bi@zte.com.cn Wang Ping, <u>wang.ping@zte.com.cn</u> Zhu Shunlin, <u>zhu.shunlin@zte.com.cn</u> *Buinaina you closer*

Asian IBIS Summit Shanghai, China November 15, 2011

Traditional Timing Design for DDRx System

Methods for DDR3 System Timing Budget Analysis

Comparison of Two Simulation Results

Summary

# Traditional Timing Design for DDRx System

#### Using Tables

| TOP NAME        | DDR3_DATA_WRITE | DDR3_DATA_READ | DDR3_ADDR_CK |

|-----------------|-----------------|----------------|--------------|

| Timing          | NODES NAME1     | NODES NAME1    | NODES NAME3  |

| From:           | CPU             | DDR3 (HYNIX)   | CPU          |

| То:             | DDR3 (HYNIX)    | CPU            | DDR3 (HYNIX) |

| Vil/Vih         | 0.925/0.575     | 0.925/0.575    |              |

| Tsetup          | 0.2             | 0.3            | 0.3          |

| Thold           | 0.2             | 0.15           | 0. 3         |

| Vmeas           | 0.75            | 0.75           | 0.75         |

| Tva_min         | 0.3             | 0.36           | 0.95         |

| Testload@Tcomin |                 |                |              |

| Tvb_min         | 0.3             | 0.36           | 0.95         |

### Traditional Timing Design for DDRx System

#### Using Simulations

#### Traditional Timing Design for DDRx System

Disadvantages of Traditional Methods:

- It doesn't consider the influences of follow list:

- SSN of PDN

- Many Kinds of Jitter, Such as DQS Jitter...

- Xtalk of Package and PCB

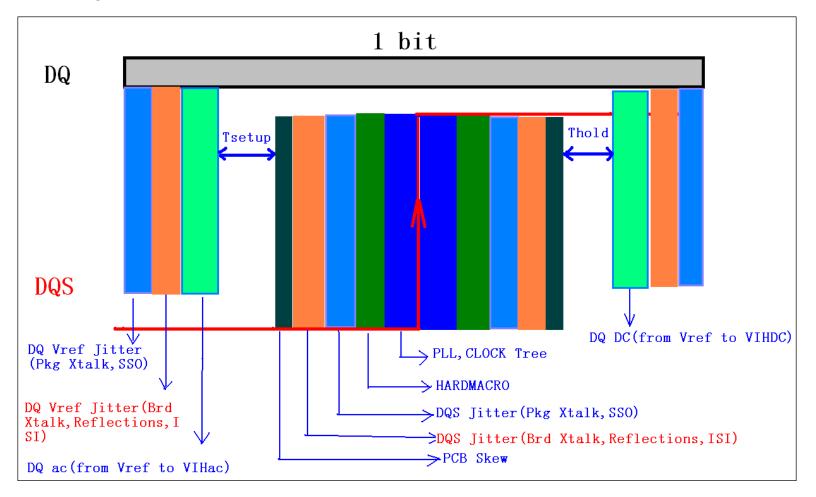

- The DDR3 timing budget consists of observing timing margins and signal integrity of the entire interconnect

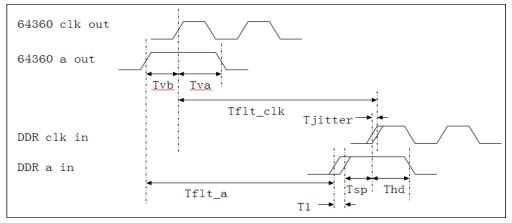

- Summarized as follows in the diagram below:

#### Timing Calculation method:

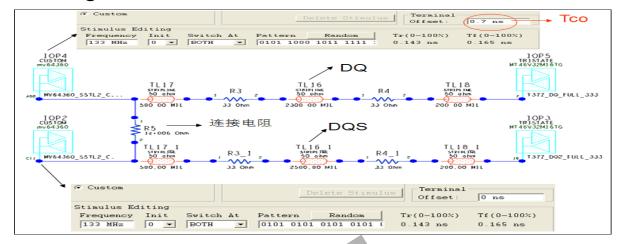

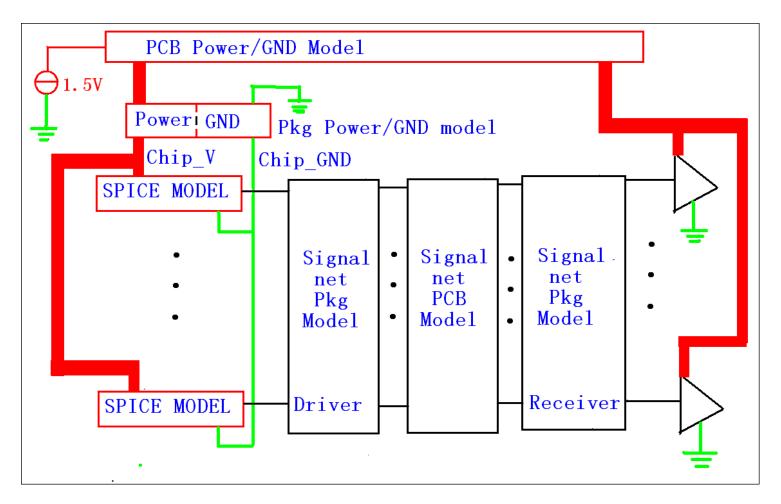

The Topology of DDR3 System Timing Simulation Using SPICE Models

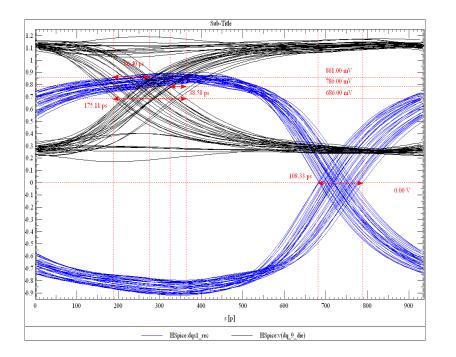

- An Example of DDR3 Simulation

- Twc\_io\_dqs\_jitter+Tbrd\_io\_dqs\_jitter= 108.33 ps

- Twc\_io\_dq\_jitter\_vref+Tbrd\_io\_dq\_jitt er\_vref=175.11 ps

- Tbrd\_io\_dq\_jitter\_ac=86.40 ps

- Tbrd\_io\_dq\_jitter\_dc=38.58 ps

- Cuting all Timing Uncertainties:

- Tsetup\_min\_margin=21ps

- Thold\_min\_margin=32ps

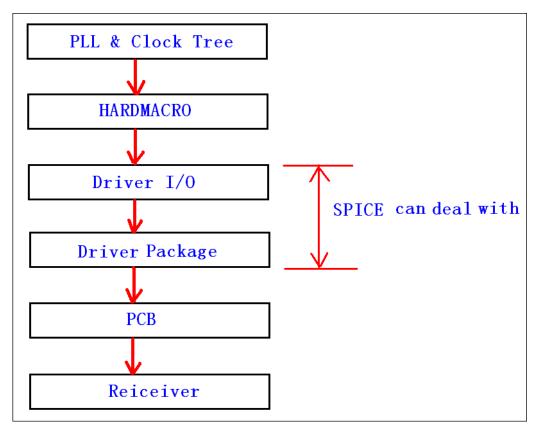

#### Analysis sources of uncertainties

| Uncertainty                            | Source                       |  |

|----------------------------------------|------------------------------|--|

| PLL, CLOCK Tree                        | IC Manufacturer              |  |

| HARDMACRO                              | IC Manufacturer              |  |

| DQS Jitter(Pkg Xtalk, SSO)             | IC Manufacturer              |  |

| DQS Jitter(Brd Xtalk, Reflection, ISI) | Simulation Using SPICE model |  |

| DQ Vref Jitter(Pkg Xtalk, SSO)         | IC Manufacturer              |  |

| DQ Vref Jitter(Brd Xtalk,              | Simulation Using SPICE model |  |

| Reflection, ISI)                       |                              |  |

| PCB Skew                               | PCB file                     |  |

| DQ ac(from Vref to VIHac)              | Simulation Using SPICE model |  |

| DQ DC(from Vref to VIHDC)              | Simulation Using SPICE model |  |

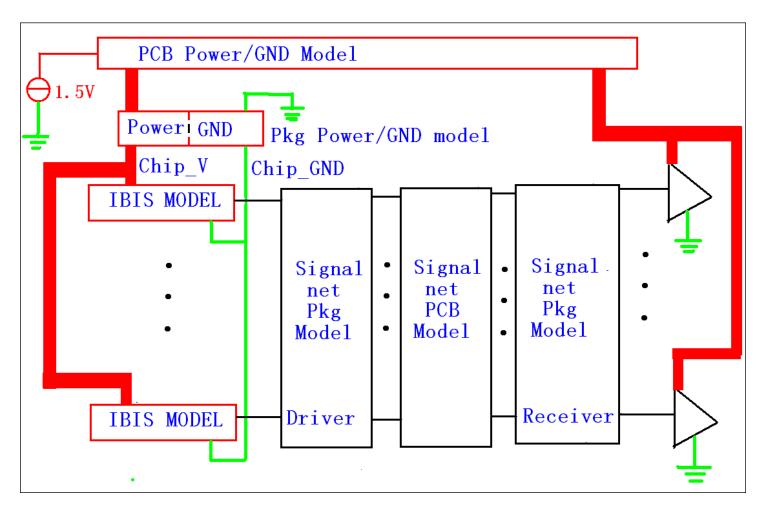

The Topology of DDR3 System Timing Simulation Using IBIS Models

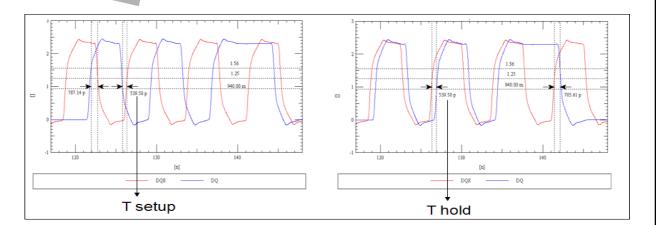

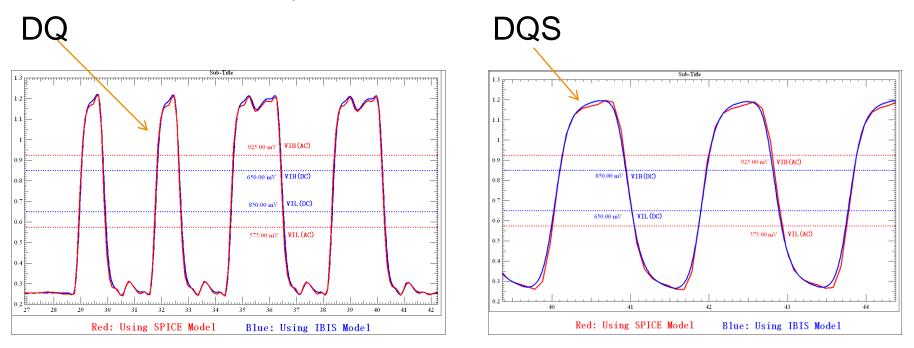

#### **Comparison of Two Simulation Results**

#### Analysis Precision

• Waveforms comparison

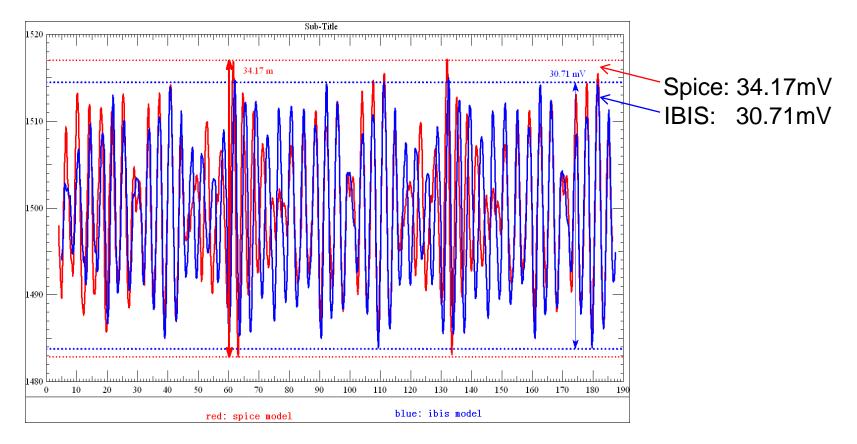

### **Comparison of Two Simulation Results**

#### Analysis Precision

•  $\triangle Vpp$  comparison

#### **Comparison of Two Simulation Results**

#### Comparison Time Consuming

| Workstation |         | Intel Core™ 2 Duo CPU<br>3.00GHz 3.37GB |

|-------------|---------|-----------------------------------------|

| Simulation  | 40 h    | 1 min                                   |

| Time        | 128bits | 128bits                                 |

Using IBIS model is very effective in DDR3 system timing simulation.

### Summary

- Choosing an appropriate modeling method is critical for simulation. Otherwise simulation may not be accurate enough or too complex and time consuming.

- The traditional way to simulate DDR3 system timing is not precise enough, because DDR3 Timing simulations need to consider all the uncertainties.

- Using the SPICE model in DDR3 timing simulation is precise, but time consuming. It's not a very effective way to work.

- IBIS model is appropriate for what-if analysis due to its relative short run time and sufficient accuracy.

Bringing you closer

© ZTE Corporation. All rights reserved.