Supporting External circuit as Spice or Sparameters in conjunction with I-V/V-T tables

**Kent Dramstad, Adge Hawes IBM Microelectronics**

Taranjit Kukal, Feras Al-Hawari, Ambrish Varma, Terry Jernberg Cadence Design Systems, Inc.

Presented by: ZhangMin Zhong, Cadence Design Systems, Inc.

Asian IBIS Summit Shanghai, China November 15, 2011

cādence°

- Requirement

- Current Limitations of [External Circuit]

- Solution

- Supporting S-parameters in [External Circuit] (BIRD144)

- Simulating [External Circuit] in conjunction with I-V/V-T tables (BIRD145)

cādence°

Summary

- Requirement

- Current Limitations of [External Circuit]

- Solution

- Supporting S-parameters in [External Circuit]

- Simulating [External Circuit] in conjunction with I-V/V-T tables

- Summary

cādence°

#### Requirement

- At high frequencies, we need ways over and above I-V, V-T tables and AMI to model the buffer.

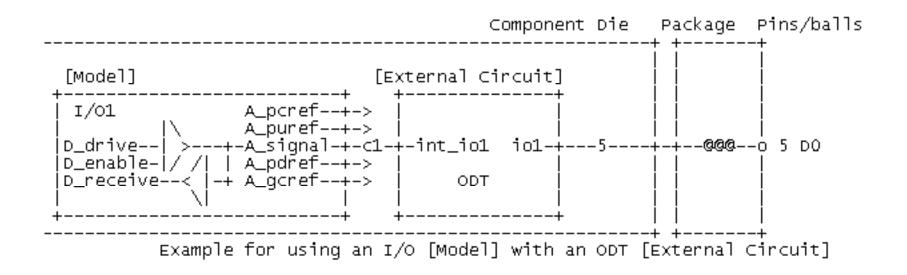

- On DIE Terminations (ODT) that vary with frequencies need to be expressed as S-parameters or RLGC Spice files

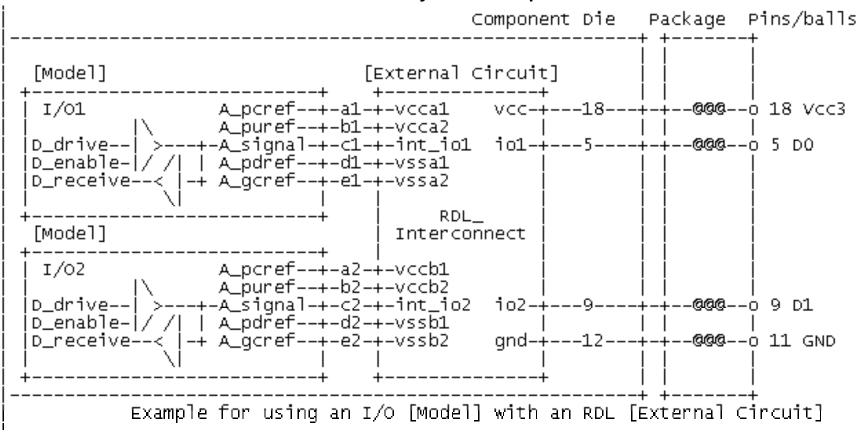

- On DIE Re-distribution layer (RDL) parasitics become significant and vary with frequencies and hence have to be expressed as S-parameters

- Analog portion of IO-buffer get expressed as Spice as against I-V/V-T curve; S-parameters get used to describe transfer characteristics of linear IO-buffer amplifiers.

#### Requirement

- At high frequencies, we need ways over and above I-V, V-T tables and AMI to model the buffer.

- Some algorithmic portion of IO-buffer model could be expressed as behavioral Spice to augment AMI code

- Example: 'if-then-else kind of spice' to pick right sub-circuit based on parameter values/processes

- Example: Modeling continuous filters as behavioral spice to augment digital filters in AMI code

#### Requirement

#### - Various Cases that need to be covered

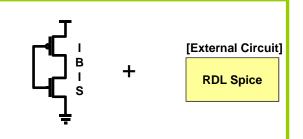

Simulating RDL parasitics in conjunction with I-V/V-T tables

Case 1

Case 2

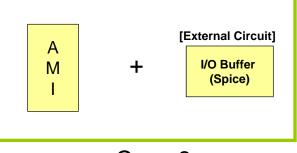

Simulating AMI with IO-buffer expressed as Spice

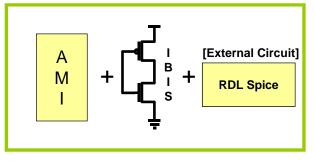

Simulating RDL parasitics in conjunction with I-V/V-T tables and AMI

Case 3

- Requirement

- Current Limitations of [External Circuit]

- Solution

- Supporting S-parameters in [External Circuit]

- Simulating [External Circuit] in conjunction with I-V/V-T tables

- Summary

cādence°

#### Current Limitations

- [External Circuit]

- Today, S-parameters have to be wrapped into Spice models (vendor specific) and then used under [External Model/Circuit] Keyword.

- On similar lines, BIRDs 116-118 propose that Touchstone file name can be parameterized for the IBIS-ISS sub-circuit, which means that IBIS-ISS wrapper could be written for the S-parameter element.

- NEED: Extend support for direct usage of Sparameters

#### Current Limitations

- [External Circuit]

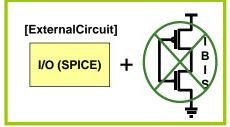

- The current [External Circuit] and [Circuit Call] usage rules do not allow the direct interconnection and instantiation of existing IBIS I/O models with the rest of the [External Circuit] blocks. Traditionally, users either use Spice or I-V/V-T tables.

NEED: Extend use of [External Circuit] keyword to point to Spice sub-circuits that augment I-V/V-T data for complete characterization of IO-buffer.

#### Current Limitations

- [External Circuit]

- In order for a model developer to use an IBIS I/O model in an [External Circuit] the following steps need to be followed:

- Develop SPICE like wrappers in which the corresponding typ, min, and max IBIS I/O sub-circuits are instantiated

- Develop an [External Circuit] to point to the wrapper subcircuits

- Use the [Circuit Call] keyword to call the [External Circuit].

- These usage rules are cumbersome especially when the developer can just directly call the desired IBIS I/O model without the need to develop a SPICE like wrapper as well as an [External Circuit] section.

- Requirement

- Current Limitations of [External Circuit]

- Solution

- Supporting S-parameters in [External Circuit] (BIRD144)

- Simulating [External Circuit] in conjunction with I-V/V-T tables

cādence°

Summary

## Solution: Leveraging [External Model/Circuit] to Support Package S-parameters

- For support of package S-parameters:

- IBIS model should have Keywords to support Touchstone

S-parameters under Package section, with fields to

- Point to Touchstone file from the Package section

- Provide port-mapping of IO-buffer pins to S-parameter ports

- R/L/C values should be ignored by SI tools if S-parameter file is used

- For support of S-parameters when representing elements beyond package parasitics: This can be achieved through use of [External Model] keyword that directly instantiates Touchstone file

- Positioning S-parameters as a method to completely define IO-buffer model or portions of IO-buffer requires support for:

- Direct support of S-parameters without the need for wrapping

- Port mapping of S-parameters

- Corners beyond typ/min/max to provide flexibility of choosing various S-parameter files under different conditions

Support for Language 'Touchstone' with port-map

```

Example of True Differential [External Model] using TOUCHSTONE:

[Model] Ext_TOUCHSTONE,_Diff_Buff

Model_type I/O_diff

Rref_diff = 100

Other model subparameters are optional

min

max

[Voltage Range]

[Ramp]

dv/dt_r

1.57/0.36n

1.44/0.57n

1.73/0.28n

dv/dt_f

1.57/0.35n

1.46/0.44n

1.68/0.28n

[External Modell

anquage TOUCHSTONE

circuit_name (.subckt name)

| Corner corner_name file_name

diffio.s8p

corner

Typ

Min

Corner

diffio.s8p

NA

diffio.s8p

Corner

NA

| Ports List of port names (in same order as in TOUCHSTONE)

Ports A_signal_pos A_signal_neg my_receive my_drive my_enable

Ports A_puref A_pdref A_pcref A_gcref A_extref my_ref A_gnd

port1

vlow vhigh trise tfall

| D_to_A d_port

port2

corner_name

D_drive

my_ref

D_to_A

my_drive

0.0

3.3

0.5n

0.3n

тур

D_drive my_drive

D_drive my_drive

D_enable my_enable

D_enable my_enable

my_ref

0.0

3.0

0.6n

0.3n

D_to_A

my_ref

D_to_A

0.0

0.4n

0.3n

Max

my_ref

3.3

0.5n

D_to_A

\circ. \circ

0.3n

my_ref

D_to_A

0.0

3.0

0.6n

0.3n

D_to_A

D_enable my_enable

my_ref

0.0

0.4n

0.3n

Max

A_to_D d_port

port1

port2

vlow

vhigh corner_name

A_to_D

D_receive

'A_signal_pos

`A_signa]_neg

-200m

200m

Тур

A_to_D

A_signal_pos

A_signal_neg

-200m

200m

D_receive

A_to_D

A_signal_pos A_signal_neg

D_receive

-200m

200m

Max

[End External Model]

```

Picking different S-parameter files for different corners

```

Example of True Differential [External Model] using TOUCHSTONE:

[Model] Ext_TOUCHSTONE,_Diff_Buff

Model_type I/O_diff

Rref_diff = 100

Other model subparameters are optional

min

max

[Voltage Range]

[Ramp]

d∨/dt_r

1.57/0.36n

1.44/0.57n

1.73/0.28n

dv/dt_f

1.57/0.35n

1.46/0.44n

1.68/0.28n

[External Modell

Language TOUCHSTONE

Corner corner_name file_name

circuit_name (.subckt name)

diffio.s8p

Corner

Typ

Min

Corner

diffio.s8p

NA

diffio.s8p

Corner

NA

I Ponts List of pont names (in same order as in joochstoke,

Ports A_signal_pos A_signal_neg my_receive my_drive my_enable

Ports A_puref A_pdref A_pcref A_gcref A_extref my_ref A_gnd

port1

D_to_A d_port

port2

vlow vhigh trise tfall corner_name

D_drive

my_ref

D_to_A

my_drive

0.0

3.3

0.5n

0.3n

тур

D_drive my_drive

D_drive my_drive

D_enable my_enable

D_enable my_enable

D_enable my_enable

D_to_A

my_ref

0.0

3.0

0.6n

0.3n

mý_ref

D_to_A

0.0

3.6

0.4n

0.3n

Max

3.3

my_ref

0.5n

D_to_A

\circ. \circ

0.3n

my_ref

D_to_A

0.0

3.0

0.6n

0.3n

D_to_A

my_ref

0.0

0.4n

0.3n

voor.

A_to_D d_port

port1

vhigh corner_name

'A_signa]_neg

A_to_D

D_receive A_signal_pos

-200m

200m

Тур

A_to_D

A_signal_pos

A_signal_neg

-200m

200m

D_receive

A_to_D

D_receive A_signal_pos A_signal_neg

-200m

200m

Max

[End External Model]

```

Supporting user-defined corners – each user-defined corner maps to typ/min/max IBIS corners

```

Example [External Model] using TOUCHSTONE with 2 userdef corners:

[Model] ExLinearBufferTouchstoneWithTwoUserDefCorners

Model_type Output

Other model subparameters are optional

max

.

[Voltage Range]

3.6

[Ramp]

1.57/0.36n 1.44/0.57n

ďv/dt⁻r

1.73/0.28n

dV/dt_f

1.57/0.35n 1.46/0.44n

1.68/0.28n

[External Model]

Language TOUCHSTONE

Corner corner_name file_name

circuit_name

Corner

buffer_typ.s2p

NA

buffer_min.s2p

Corner

Min

NA

buffer max.s2b

Corner

NA

Parameters List of parameters

Parameters MinNumber MaxNumber

User_defined_corner user_defined_corner_name parameter_name parameter_value file_name corner_name

buffer_min1.s2p Min

-User_defined_corner

Min1

MinNumber

User_defined_corner

Max1

MaxNumber

buffer_max1.s2p Max

```

Use in [External Model] and [External Circuit]

```

Example [External Model] using #OUCHSTONE:

Example [External Circuit] using TOUCHSTONE:

[Model] ExBufferTouCHSTONE

[External Circuit] BUFF-TOUCHSTONE

Model_type I/O

Language TOUCHSTONE

Vinh = 2.0

|Vinl = 0.8

Corner corner_name file_name

circuit_name (.subckt name)

buffer_typ.s9p

Corner

Other model subparameters are optional

Min

buffer_min.s9p

Corner

Corner

buffer_max.s9p NA

min

max

[Voltage Range]

3.0

3.6

Ports List of port names (in same order as in TOUCHSTONE)

Ports A_signal int_in int_en int_out A_control

[Ramp]

Ports A_puref A_pdref A_pcref A_qcref

ďv/dt≟r

1.⁄57/0.36n

1.44/0.57n

1.73/0.28n

dv/dt_f

1.57/0.35n

1.68/0.28n

1.46/0.44n

D_to_A d_port

vlow vhigh trise tfall corner_name

port1 port2

D_drive int_in my_gcref 0.0 3.3

0.5n 0.3n Typ

D_to_A

[External Model]

D_to_A

D_drive int_in my_gcref 0.0

3.0

0.6n 0.3n Min

Language TOUCHSTONE

D_drive int_in my_gcref 0.0

D_to_A

3.6

0.4n

D_enable int_en my_gnd

0.0 3.3

0.5n

D_to_A

Corner corner_name file_name

circuit_name (.subckt

D_to_A

D_enable int_en my_qnd

0.0 3.0

Corner

buffer_typ.s7p NA

0.0 3.6

D_to_A

D_enable int_en my_qnd

buffer_min.s7p NA

Corner

buffer_max.s7p NA

Corner

A_to_D d_port

vlow vhigh corner_name

port1

port2

υ_receive int_out my_gcref 0.8 2.0

| Ports List of port names (in same order as in TOUCHSTONE)A_TO_U

D_receive int_out my_gcref 0.8

A_to_D

Min

Ports A_signal my_drive my_enable my_receive my_ref

A to D

D_receive int_out my_gcref 0.8

Ports A_puref A_pdref A_pcref A_qcref A_extref

vlow vhigh trise tfall[End External Circuit]

D_to_A d_port

port1

port2

D_to_A D_drive my_drive my_ref 0.0 3.3 0.5n 0.3n

D_to_A D_enable my_enable A_gcref 0.0 3.3 0.5n 0.3n

A_to_D d_port

port1

port2

vlow vhigh corner_name

A_to_D D_receive my_receive my_ref 0.8 2.0

Note: A_signal might also be used instead of a user-defined interface port

for measurements taken at the die pads

[End External Model]|

```

- Requirement

- Current Limitations of [External Circuit]

- Solution

- Supporting S-parameters in [External Circuit]

- Simulating [External Circuit] in conjunction with I-V/V-T tables(BIRD145)

- Summary

cādence°

Ability to connect External Circuit to IBIS I/O model. The External Circuit could represent RDL parasitics, portion of active I/O buffer, some algorithmic part of I/O buffer.

```

[Pin] signal_name

model name

R_pin L_pin C_pin

RAS0#

Buffer1

200.0m 5.0nH 2.0pF

RAS1#

Buffer2

209.0m NA

2.5pF

EN1#

6.3nH NA

Input1

NA

A0

3-state

I/O1

D0

RD#

Input2

310.0m 3.0nH 2.0pF

WR#

Input2

1/02

8

Α1

I/O2

D1

GND

GND

297.0m 6.7nH 3.4pF

10

RDY#

11

Input2

12

GND

GND

270.0m 5.3nH 4.0pF

```

HERE DO, D1 are to be modeled as I/O1, I/O2 buffers followed by RDL Spice and represent a differential buffer

I/O1 and I/O2 are followed by RDL Spice model

```

[Node Declarations]

| Must appear before any [Circuit Call] or [Model Call] keyword

I Die nodes

a1 b1 c1 d1 e1

List of die nodes representing signals that connect models

a2 b2 c2 d2 e2

[End Node Declarations]

NOTE:

A [Model] named "I/O1" must be present in the IBIS file in order to enable

the tool to instantiate and connect the called model "as usual" based on

the I-V and T-V curves as well as the subparameters under the corresponding

[Model] section.

[Model Call] I/O1

| Instantiates [Model] named "I/O1"

pad/node

mapping port

Port map A pcref

a1

Port to internal node connection

Port_map A_puref

b1

Port to internal node connection

Port_map A_signal

c1

Port to internal node connection

Port_map A_pdref

d1

Port to internal node connection

Port map A gcref

Port to internal node connection

e1

[End Model Call]

```

```

NOTE:

A [Model] named "I/O2" must be present in the IBIS file in order to enable

the tool to instantiate and connect the called model "as usual" based on

the I-V and T-V curves as well as the subparameters under the corresponding

[Model] section.

[Model Call] I/O2

| Instantiates [Model] named "I/O2"

pad/node

mapping port

Port map A pcref

a2

Port to internal node connection

Port_map A_puref

b2

Port to internal node connection

Port map A signal

c2

| Port to internal node connection

Port map A pdref

d2

Port to internal node connection

Port map A gcref

e2

Port to internal node connection

[End Model Call]

```

```

[Circuit Call] RDL_Interconnect | Instantiates [External Circuit] named "RDL_Interconnect"

pad/node

mapping port

Port_map vcc

18

| Port to implicit pad connection

12

Port_map gnd

Port to implicit pad connection

Port to implicit pad connection

Port map io1

5

Port to implicit pad connection

Port map io2

Port to internal node connection

Port map vcca1

a1

Port_map vcca2

b1

Port to internal node connection

Port_map int_io1

c1

Port to internal node connection

Port to internal node connection

Port map vssa1

d1

Port to internal node connection

Port map vssa2

e1

Port map vccb1

Port to internal node connection

a2

Port_map vccb2

b2

Port to internal node connection

Port_map int_io2

c2

Port to internal node connection

Port map vssb1

d2

Port to internal node connection

Port map vssb2

e2

Port to internal node connection

[End Circuit Call]

```

- Requirement

- Current Limitations of [External Circuit]

- Solution

- Supporting S-parameters in [External Circuit]

- Simulating [External Circuit] in conjunction with I-V/V-T tables

- Summary

cādence°

#### Summary

- With increase in frequencies, we need enhanced usage of External Model / Circuit

- S-parameters are becoming common way to model portions of I/O buffers and package parasitics; Hence need to have direct support of S-parameter model under [External Model/Circuit]. This has been proposed as BIRD144

- Significant portion of I/O buffer gets modeled as Spice/S-parameters to augment the main analog buffer to capture the high frequency behavior; Hence need to have easy way to connect External Circuit to I-V/V-T table-model. This has been proposed as BIRD145

#### Summary

BIRD144 and BIRD145 can be accessed at

http://www.eda.org/pub/ibis/birds/

- The BIRDs would be considered and discussed by the IBIS open forum

- Other BIRDs will also be considered that might be alternatives or add-on to this proposal

### cādence®