### **Automated AMI Model Generation & Validation**

José Luis Pino Amolak Badesha

Manuel Luschas

Antonis Orphanou

Halil Civit

Asian IBIS Summit, Taipei, Taiwan November 12, 2010 (Presented previously at the IBIS Summits on June 15, 2010 and November 9, 2010)

## **Agenda**

- AMI Model Generation Barriers

- Automated AMI Model-generation flow

Example-1: 6.25 Gb/s

Example-2: 10.3125 Gb/s

- TX Model Correlation Study

- -with Transistor Simulations

- -with Measurements

- Benefits of Automated AMI flow

### **#1 AMI modeling barrier**

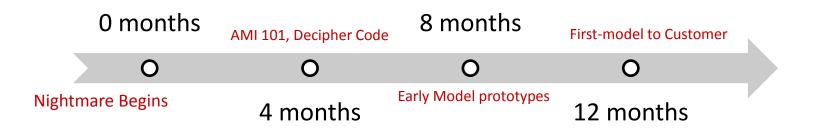

#### **Model Generation Time**

AMI Modeling suppose to Speed-up System Design Cycle,

BUT, Model-generation takes Significant Time & Resources

....System Vendors have to wait a LONG time before accurate AMI models become available

Note: Vendors with NO experience in AMI modeling are spending <u>6-12+ months</u> to come up with first-generation models

Models come very late in Design Cycle → used only for Validation, NOT Design

## Why AMI-model generation takes so long?

Typical Signal Integrity Engineers are NOT programmers

....they are having "Nightmares" in trying to develop AMI models

- Cryptic Matlab/C++ code passed from System-Architectures → AMI Modeler (if lucky)

- Challenge to Convert Algorithm design Code → AMI format

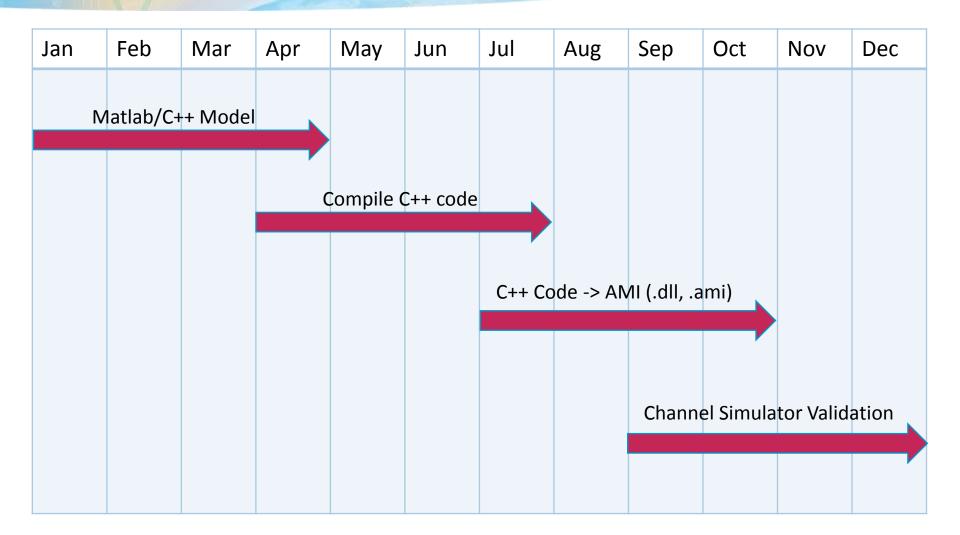

# Typical AMI model generation flow...

# **Automated AMI model generation flow...**

| Jan                | Feb                          | Mar      | Apr                               | May       | Jun | Jul | Aug | Sep | Oct | Nov | Dec |

|--------------------|------------------------------|----------|-----------------------------------|-----------|-----|-----|-----|-----|-----|-----|-----|

|                    | C++ Mod  Common ocks C Au Co |          | ++ code<br><u>n</u><br>>> AMI (.c |           |     | Jui | Aug | Sep | Oct | NOV | Dec |

|                    | <u> </u>                     | hannel S | imulator                          | Validatio | n   |     |     |     |     |     |     |

| Automated AMI Flow |                              |          |                                   |           |     |     |     |     |     |     |     |

## **ESL flow for Automated AMI Modeling**

**Electronic System Level (ESL)** design and verification is an emerging electronic design methodology that focuses on the <u>higher abstraction</u> level concerns first and foremost.

ESL flow facilitates utilization of appropriate abstractions in order to <u>increase</u> <u>comprehension about a system</u>, and to enhance the probability of a successful implementation of functionality in a <u>cost-effective</u> manner

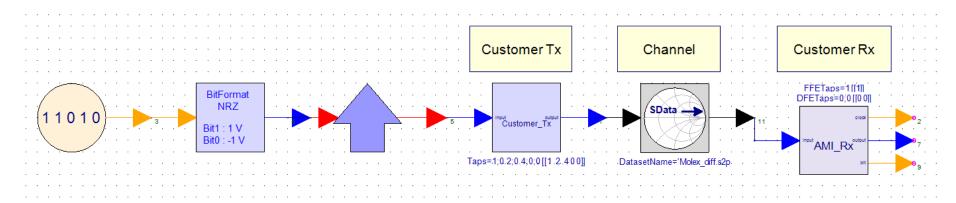

Here is an Example of SerDes modeling using ESL flow-

## **ESL flow: TX Modeling Example (1)**

**Step-1:** Starting Architecture Design with Generic Model

Different blocks represent high-level TX architecture

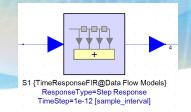

### More on FIR Filter...

How to bring in Spice or Measured data?

### **Challenges:**

1. Typical Simulation and Measured Data is not equally time-stepped

## **ESL flow: TX Modeling Example (2)**

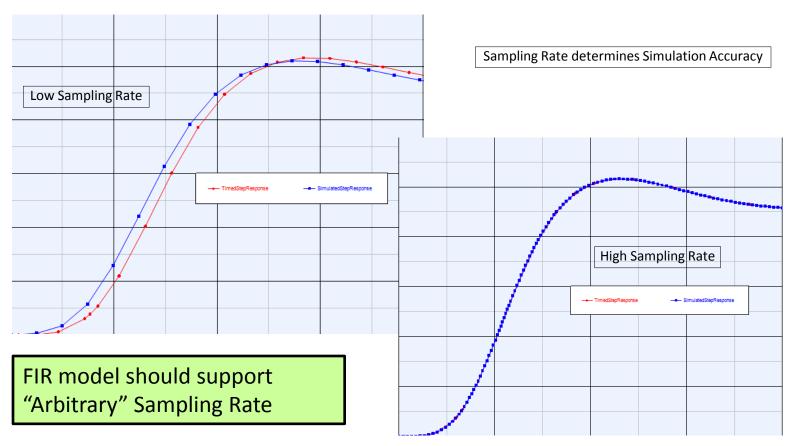

**Step-2:** Customize IP -> Bring in Math Lang or C++ Code

# **ESL flow: TX Modeling Example (3)**

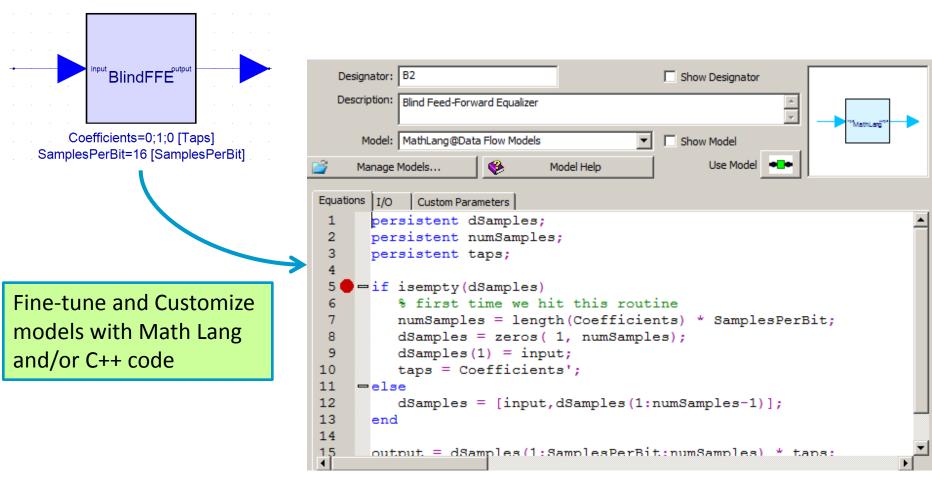

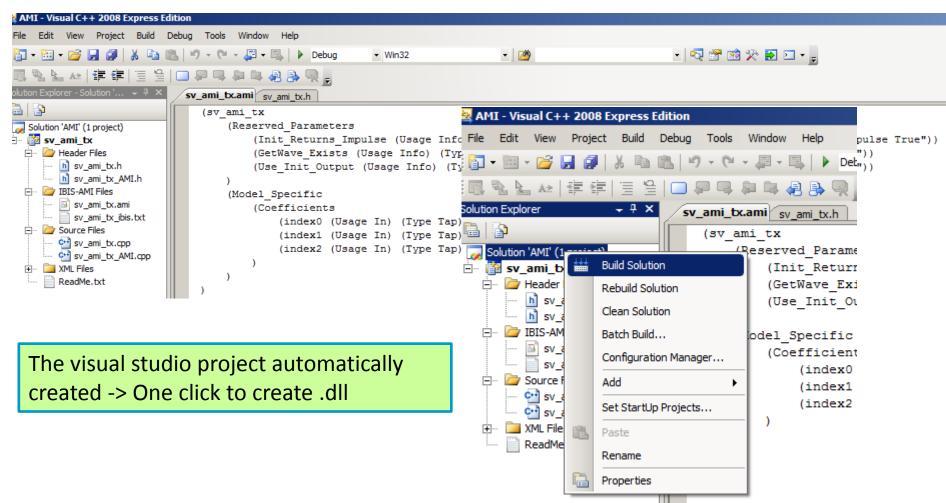

**Step-3:** One-click AMI Code-Generation

### **ESL flow: TX Modeling Example (4)**

#### **Step-4:** Automatically Generated .ami and Visual-Studio project

# Example #1 6.0 Gb/s (SATA 3.0)

#### 6.0 Gb/s SATA 3.0 SerDes Generate square bit CTLE & DFE wave, including AMI Rx modeling impairments **AMI TX** Data2 {AMI\_CTLE\_Rx} DFETaps=0;0;0;0 [[0 0 0 0]] BitRate=6e+9Hz [BitRate] 11010 AMI\_CTLE\_Rx<sub>6</sub> AMI\_Tx\_6 S2 {SData@Data Flow Models} DatasetName='Tyco\_Channel\_Diff.s2p {JitterGenerator@Data Flow Models Data3 {AMI\_Tx\_6} BitRate=6e9Hz Tyco Channel

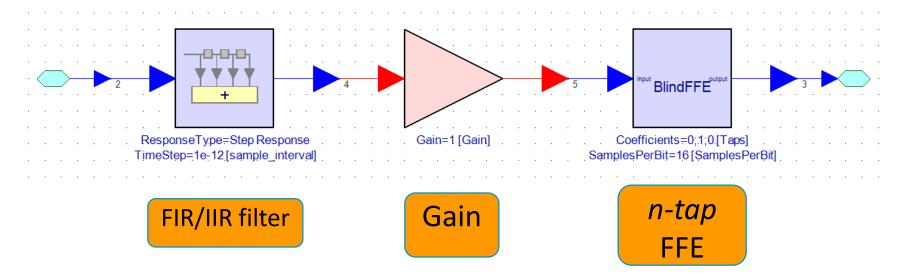

# TX Modeling 6.0 Gb/s (SATA 3.0)

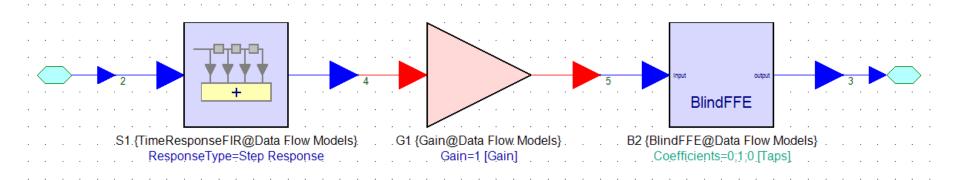

#### TX Architecture

FIR filter

3-tap FFE

# RX Modeling 6.0 Gb/s (SATA 3.0)

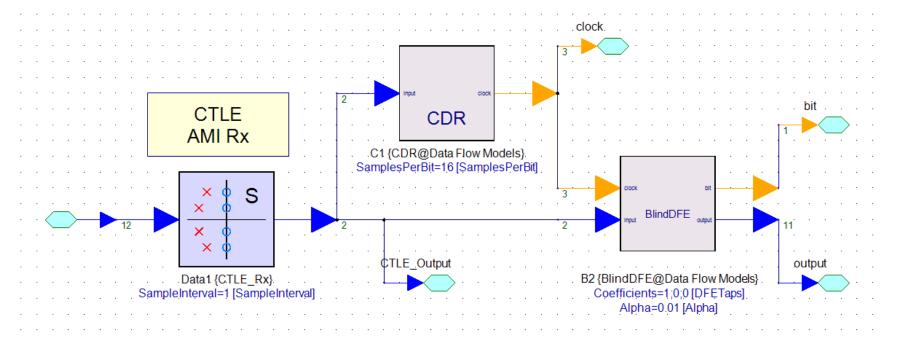

#### **RX** Architecture

S-domain filter 3-tap DFE

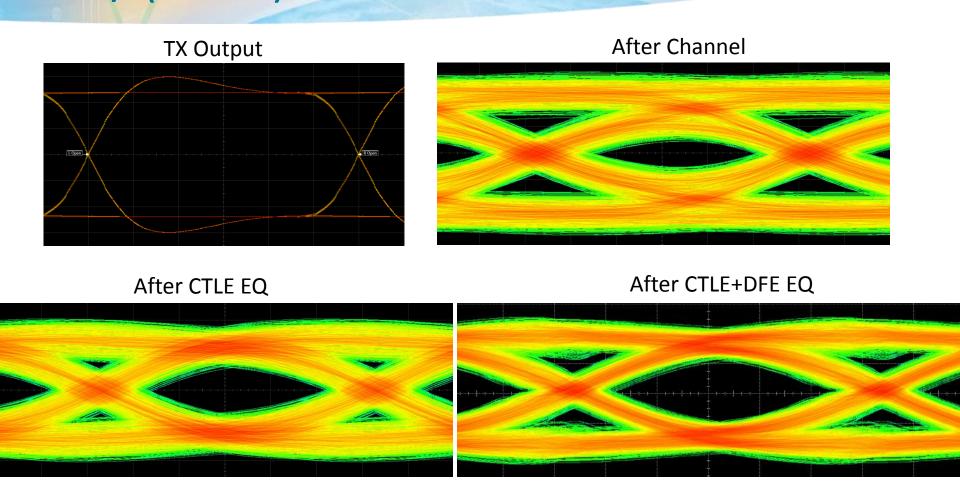

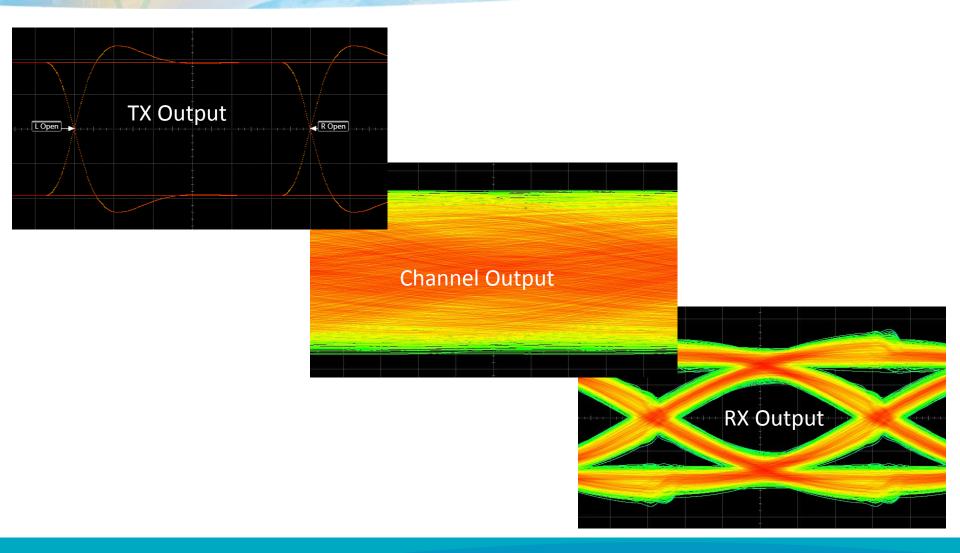

# Results 6.0 Gb/s (SATA 3.0)

\*Note: EQ taps not optimized for maximum eye

# Example #2 10.3125 Gb/s (10-GB Ethernet)

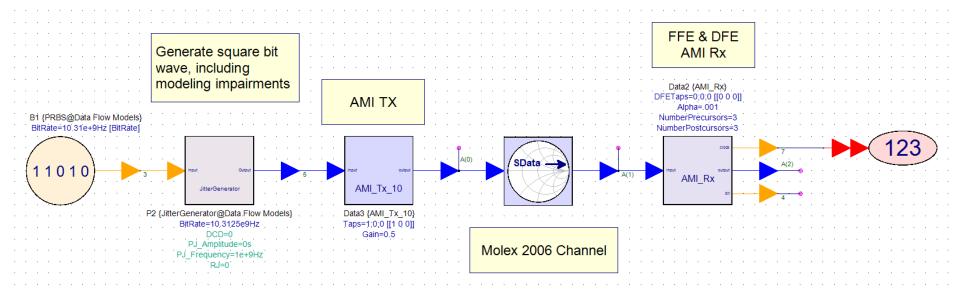

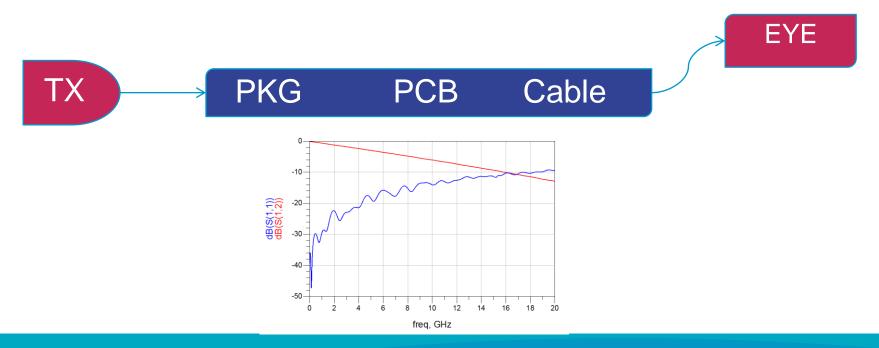

### 10.3125 Gb/s SerDes

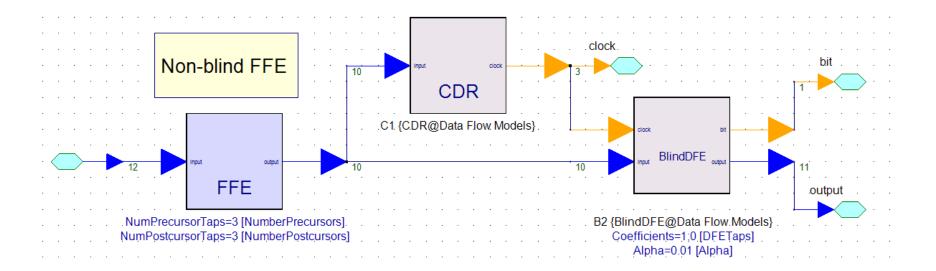

# RX Modeling 10.3125 Gb/s (10-GB Ethernet)

# Example #2 10.3125 Gb/s (10-GB Ethernet)

# TX 10.3125 Gb/s AMI model correlation study

### Strategy

- 1. Correlate Transistor Simulation vs. AMI model

- 2. Correlate Measured vs. AMI model

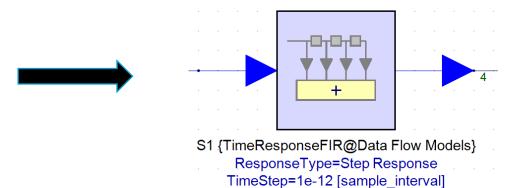

### **Transistor Simulation vs. AMI Model**

### Steps-

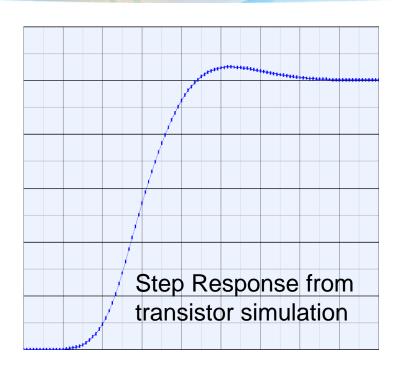

- 1.Generate Step Response from transistor simulation

- 2.Generate AMI model using EDA tool

- 3.Compare

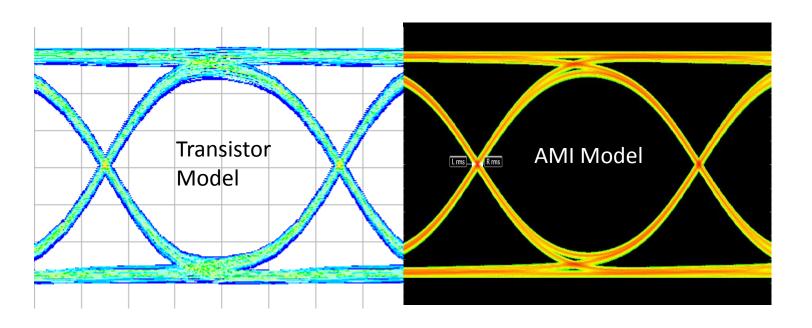

# **Step Response Model**

FIR filter with Step Response Input

### Correlation

### transistor model vs. AMI model

Excellent match between transistor simulation and AMI model

Good faith in model-generation methodology!

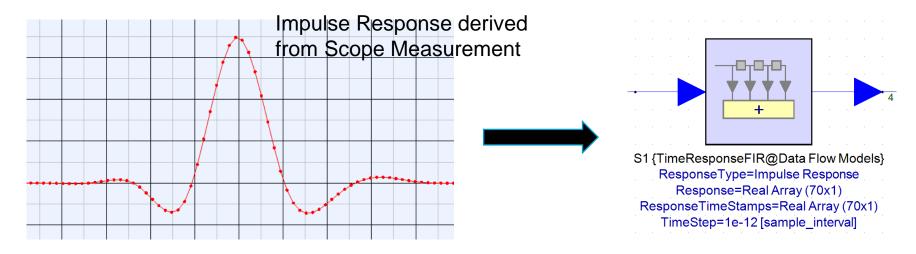

# Measurement vs. AMI Model

### Steps-

- 1. Measure waveform

- De-embed Channel

- 3. Output Impulse response

# **Impulse Response Model**

FIR filter with Impulse Response Input

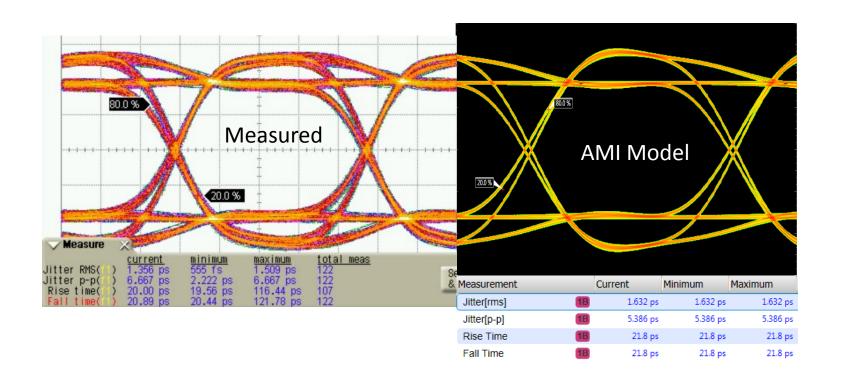

### **TX Correlation Measured**

emphasis #1: tap 0, 1, -0.2

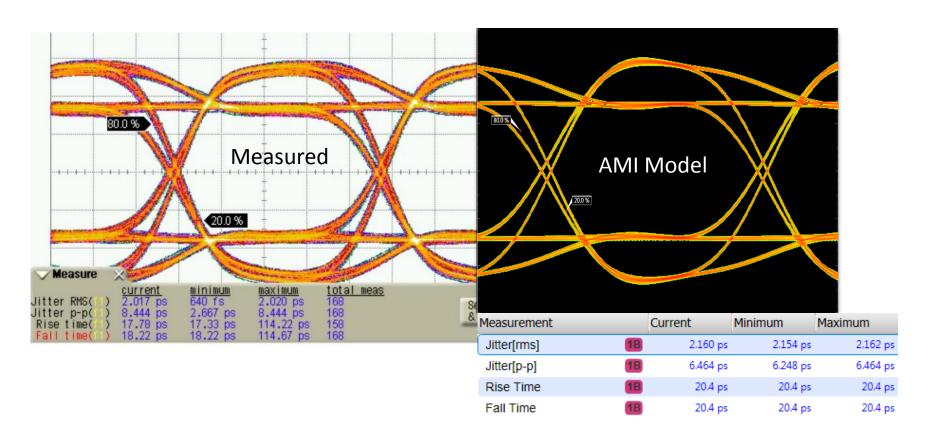

### **TX Correlation Measured**

emphasis #2: tap 0, 1, -0.25

# **Benefits of ESL Design Flow**

#### **Automated AMI-Model Generation**

- 1. Complete "Automation" of Code-generation and Model Compilation a task that routinely takes months because of its complexity

- 2. Basic building blocks that can used to start model development *FIR/IIR filters, FFE, DFE, CDR etc.*

- 3. Easily customize models to include custom IP Custom C++ and Math-Lang