### PDN design and analysis methodology in SI&PI codesign

www.huawei.com

Asian IBIS Summit, November 9, 2010, Shenzhen China

Luo Zipeng (luozipeng@huawei.com) Liu Shuyao (liushuyao@huawei.com)

- \* SI&PI co-design challenge

- \* Key parameters in PDN design

- Modeling the loop inductance of high frequency capacitor

- High frequency capacitor' global decouple effect

- Tight coupling Power-Gnd pair in board' PDN

- SSN analysis of PDN' SI&PI co-design via PDN' IBIS model

### SI&PI co-design challenge

♦As signal IO voltage level decreasing and signal speed constantly increasing, the effect of SSN become serious,.

♦SSN noise directly affect noise margin of low voltage level and time margin of high speed signal.

◆Traditional independent SI and PI analysis bring the limitation.

### Key parameters in PDN design

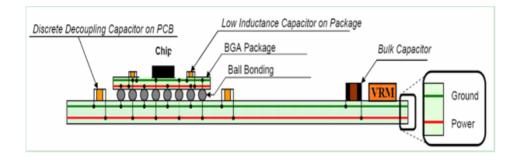

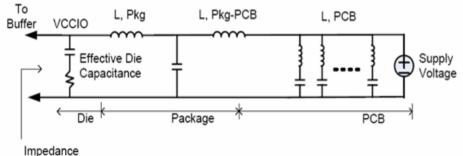

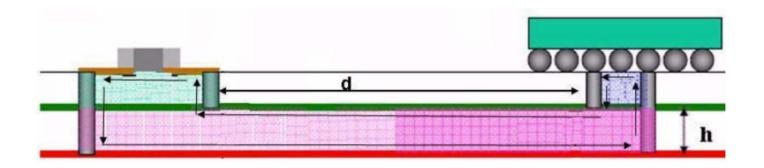

Board' PDN sketch map

From chip perspective

Equivalent circuit of board' PDN

#### PDN of Board:

♦VRM

- ♦Bulk capacitor

- ◆High frequency capacitor

- Power-Gnd plane capacitor

◆Chip' PDN

High frequency capacitor and Power-Gnd plane play an important role in PDN design;

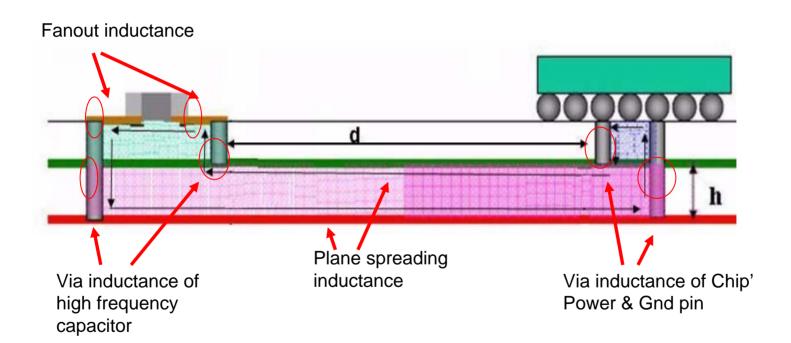

### Loop inductance of high frequency capacitor

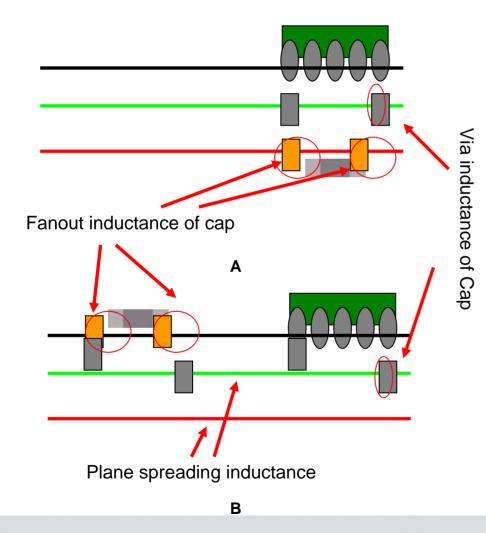

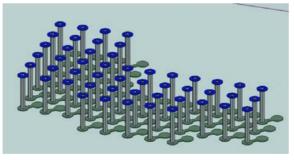

#### Via inductance effect in Loop inductance

◆Capacitor' ESL: 0.4~0.65nH;

- Special fanout inductance: 0.25~0.3nH;

- Plane spreading inductance: hundreds of pH;

- ◆Via inductance of Capacitor: 1nH~2.5nH, when in different stackup, The Value will be varied

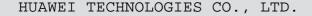

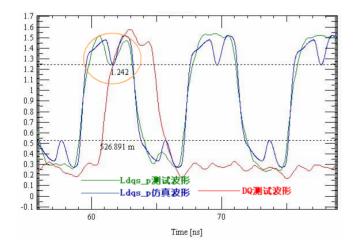

### Modeling the via inductance

| measurement | Simulation | precision |  |

|-------------|------------|-----------|--|

| 2.29nH      | 2.25nH     | 98%       |  |

◆Via inductance is about 75%~80% of the total loop inductance;

◆As the the Power-Gnd pair space and location changed, the via inductance of capacitor may varies;

◆Optimizing the design of Power-Gnd pair will decrease the via inductance, increase the decouple effect of high frequency capacitor;

◆Evaluate the value of via inductance by simulation, comparison between simulation and measurement validate the precision of via inductance model.

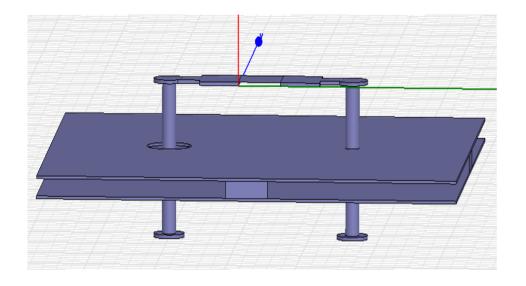

## Comparison of capacitor decouple effect with different via inductance

| Power-Gnd plane space                                                                                                        | Power-Gnd plane location | Via inductance of Caps                                 | Corresponding line |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------------------------|--------------------|

| S≪10mil                                                                                                                      | Above of the Stackup     | 0.3nH <l<0.55nh< td=""><td>Red line</td></l<0.55nh<>   | Red line           |

| 10mil <s<30mil< td=""><td>Above of the Stackup</td><td>0.55nH<l<1.5nh< td=""><td>Orange line</td></l<1.5nh<></td></s<30mil<> | Above of the Stackup     | 0.55nH <l<1.5nh< td=""><td>Orange line</td></l<1.5nh<> | Orange line        |

| S≪10mil                                                                                                                      | Center of the Stackup    | L≈2.5nH                                                | Green line         |

| 10mil <s<30mil< td=""><td>Center of the Stackup</td><td>2nH<l<2.5nh< td=""><td>Yellow line</td></l<2.5nh<></td></s<30mil<>   | Center of the Stackup    | 2nH <l<2.5nh< td=""><td>Yellow line</td></l<2.5nh<>    | Yellow line        |

| 30mil <s<65mil< td=""><td>Center of the Stackup</td><td>2.3nH<l<3nh< td=""><td>Blue line</td></l<3nh<></td></s<65mil<>       | Center of the Stackup    | 2.3nH <l<3nh< td=""><td>Blue line</td></l<3nh<>        | Blue line          |

| 10mil <s<30mil< td=""><td>Underside of the stackup</td><td>3nH≤L</td><td>Black line</td></s<30mil<>                          | Underside of the stackup | 3nH≤L                                                  | Black line         |

| S≪10mil                                                                                                                      | Underside of the stackup | 3.2nH <l< td=""><td>Purple line</td></l<>              | Purple line        |

## Plane spreading inductance affect high frequency cap decouple

◆Designing the PDN of PCB, in order to decrease loop inductance of capacitor, high frequency decoupling capacitor will be located as close as possible to chips' power pin;

◆High frequency decaps usually locate under the chip, close to the power pin;

◆In actual design, Both chips and decaps need to be located on top side of PCB, for the limitation of chip's dimension, decaps only can be near to the chips, not close to power pin,

◆as seen as left fig B, plane spreading inductance increase while both chip and decap be located on top side of PCB;

◆ Compared with fig A, the total loop inductance in fig B will increase, and High frequency capacitor' decouple effect obviously decrease;

### Global decouple effect of high frequency cap

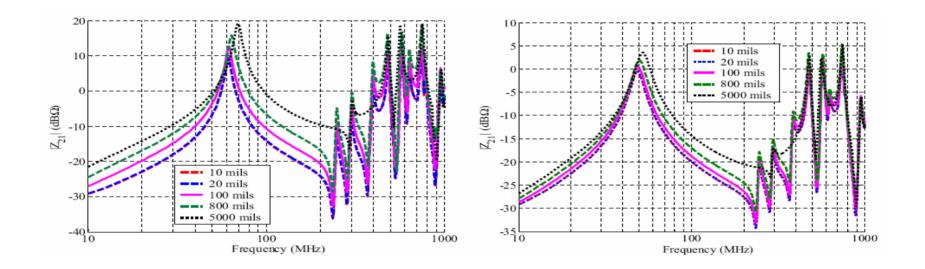

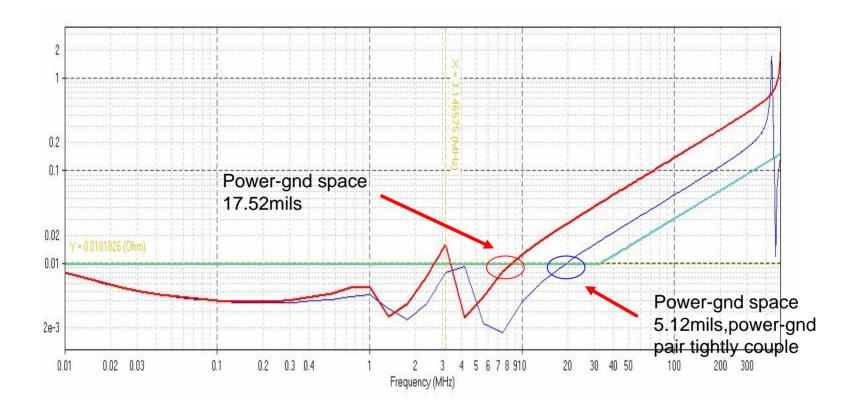

♦ As decreasing the space between the Power Ground plane, the total loop inductance also decrease, and high frequency caps will show an global decouple effect.

# Power-Gnd pair space more than 30mils, high frequency capacitor show an local effect

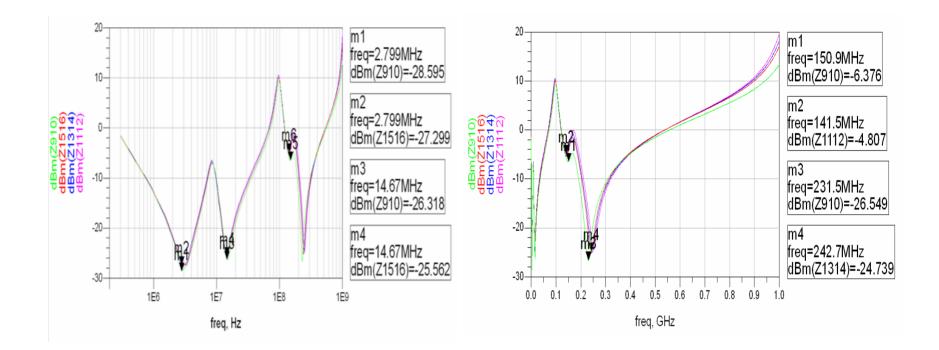

◆Power-Gnd pair space more than 30mils, distance between chip and capacitor varying from 500mils to 1000mils, the resonance frequency and anti-resonance frequency of high frequency capacitor will change.

# Power-Gnd pair space less than 10mils, high frequency capacitor show an global effect

◆Power-Gnd pair space less than 10mils, distance between chip and capacitor varying from 500mils to 1000mils, the resonance frequency and anti-resonance frequency of high frequency capacitor almost keep same.

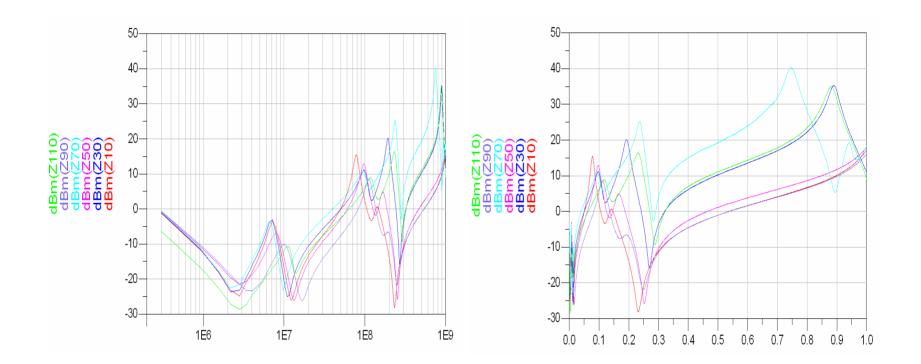

# Power-Gnd pair space effect analysis of PDN design

◆Distance between chip and capacitor keep constant, power-gnd pair space varying from 5.12mils to 56.2mils, the resonance frequency and anti-resonance frequency of high frequency capacitor change.

### Tight coupling Power-Gnd pair in PDN

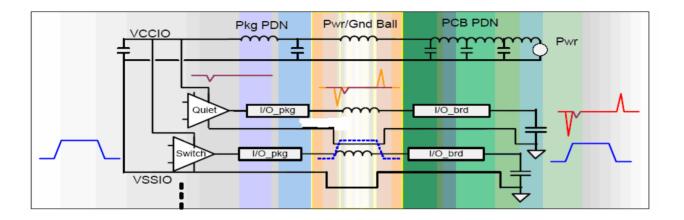

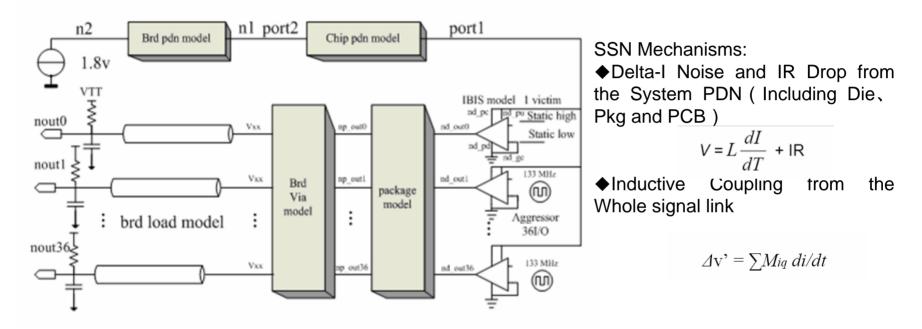

### SSN Mechanism and SI/PI Co-Design Challenges

SSN Influence :

- ◆Decrease the noise margin and timing margin

- Increase Power noise and EMI problem

SSN Simulation challenges :

- Multi signal and PDN co-design

- Whole PDN and Couping models

- Source active models

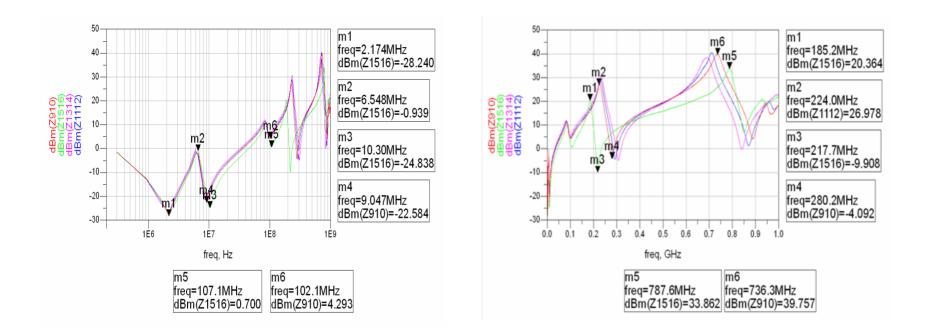

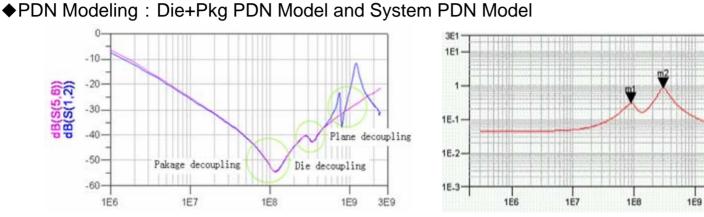

### PDN Modeling and ibis active

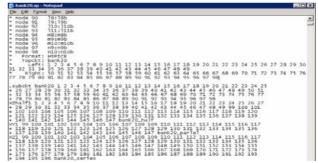

Coupling Modeling : Pkg Coupling Model and Via Coupling Model

♦ IBIS for the active model : IBIS buffer has some advantage and limitation for SSN simulation

6E9

### SSN Simulation using ibis models

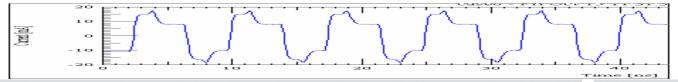

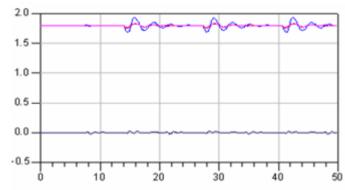

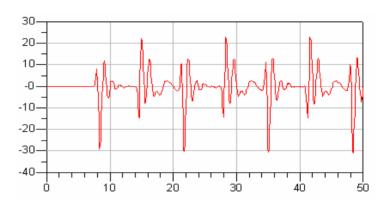

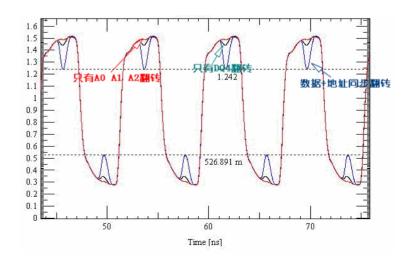

Delta-I Noise and Multi Crosstalk

♦SI+PI Co-simulation using ibis models

### Conclusion

PDN directly determine the board' power delivery system design quality, and in board' PDN high frequency capacitor and Power-Gnd plane play an important role;

◆The loop inductance of high frequency capacitor decrease as smaller as possible in a well designed PDN ,and capacitor show an global decouple effect;

◆The tight coupling PDN adequately consider power-gnd plane capacitor, expanding the efficiency frequency band;

SSN analysis via PDN' IBIS model enhance simulation efficiency and speed. Implementing SI&PI co-design.

### Thank you www.huawei.com