## Model Connection Protocol extensions for Mixed Signal SiP

Taranjit Kukal (<u>kukal@cadence.com</u>) Dr. Wenliang Dai (<u>wldai@cadence.com</u>) Brad Brim (<u>bradb@sigrity.com</u>) assisted by Eiji Fujine Fujitsu VLSI Limited

Presented by: Dr. Wenliang Dai - Cadence

Asian IBIS Summit Shenzhen China November 9, 2010

# Agenda

- Why Model Connection Protocol

- Model Connection Protocol overview

- Extensions required for Mixed Signal SiP

- MCP Applications

- Summary

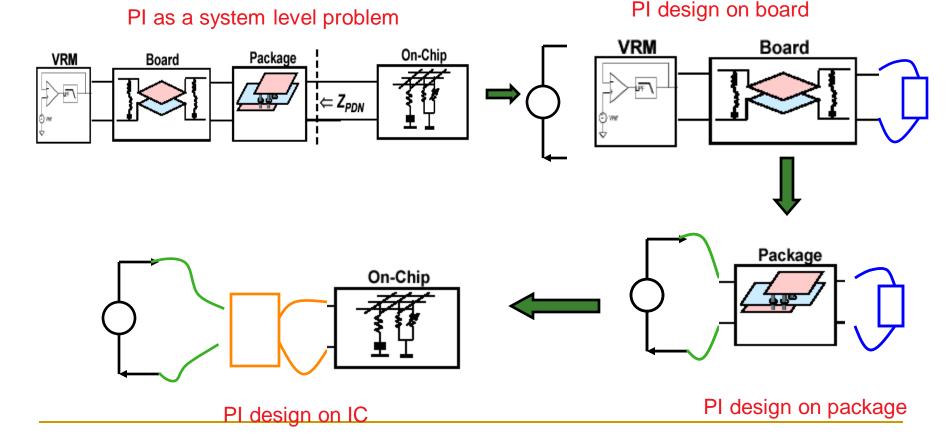

# Why Model Connection Protocol - IC/Pkg/Board PDN Co-design

#### Design low impedance path: supply to chip

## Why Model Connection Protocol - IC/Pkg/Board PDN Co-design

# Why Model Connection Protocol

- IC/Pkg/Board PDN Co-design

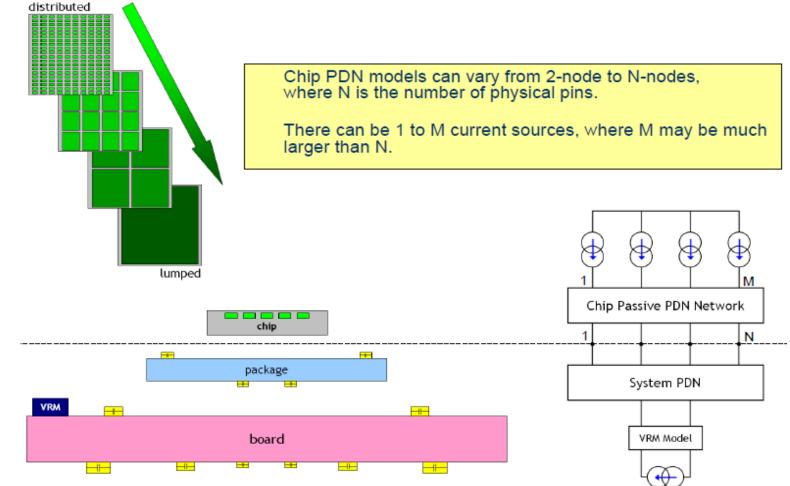

- Chip/Package/Board have many physical connections

- Chip-Package Boundary:100-6000

- Package-Board Boundary: 100-3000

- Not all electrical nodes can have per-pin resolution

- Models may become too large for computation, simulation

- Need way to group pins and auto-connect models across IC/Pkg/Board

#### **MCP** Overview

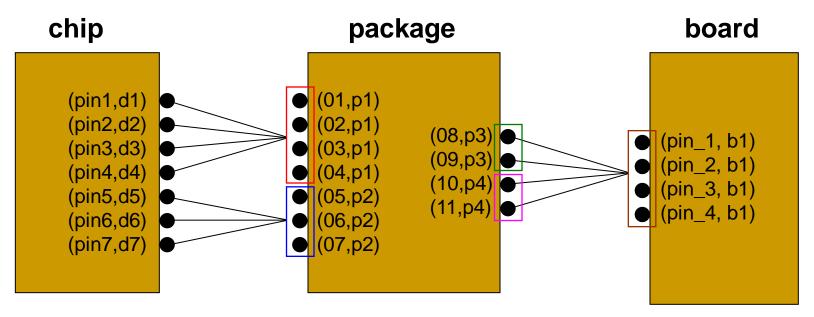

## - Establish mapping

- Pin grouping and mapping

- physical pin (of layout) to electrical node (of model) per Net

- Mapping to connecting structure using physical location

#### Example of VDD net across chip-pkg-board

| MCP Overview                                              |                                                                                                                     |  |  |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|

| - Establish                                               | mapping                                                                                                             |  |  |

|                                                           | .subckt <u>package</u> p1 p2 p3 p4<br>* [MCP Begin]                                                                 |  |  |

|                                                           | <ul> <li>* [MCP Ver] 1.1</li> <li>* [Structure Type] PKG</li> <li>* [MCP Source] package extraction tool</li> </ul> |  |  |

| .subckt <u>chip</u> d1 d2 d3 d4 d5 d6 d7<br>* [MCP Begin] | <pre>* [Coordinate Unit] um * [Connection] die1 myCPU 7</pre>                                                       |  |  |

| * [MCP Ver] 1.1                                           | * [Connection] diel mycro /<br>* [Connection Type] DIE                                                              |  |  |

| * [Structure Type] DIE                                    | * [Power Nets]                                                                                                      |  |  |

| * [MCP Source] chip extraction tool                       | * 01 p1 VDD 0 0                                                                                                     |  |  |

| * [Coordinate Unit] um                                    | * 02 p1 VDD 0 100                                                                                                   |  |  |

| * [Connection] pkg1 pkg bumps 7                           | * 03 p1 VDD 100 0                                                                                                   |  |  |

| * [Connection Type] PKG                                   | * 04 p1 VDD 100 100                                                                                                 |  |  |

| * [Power Nets]                                            | * 05 p2 VDD 50 0                                                                                                    |  |  |

| * pin1 d1 VDD 0 0                                         | * 06 p2 VDD 50 50                                                                                                   |  |  |

| * pin2 d2 VDD 0 100                                       | * 07 p2 VDD 50 100                                                                                                  |  |  |

| * pin3 d3 VDD 100 0                                       | * [Connection] board1 my_board 4                                                                                    |  |  |

| * pin4 d4 VDD 100 100                                     | * [Connection Type] PCB                                                                                             |  |  |

| * pin5 d5 VDD 50 0                                        | * [Power Nets]                                                                                                      |  |  |

| * pin6 d6 VDD 50 50                                       | * 08 p3 VDD 0 0                                                                                                     |  |  |

| * pin7 d7 VDD 50 100                                      | * 09 p3 VDD 0 200                                                                                                   |  |  |

| * [MCP End]                                               | * 10 p4 VDD 200 0                                                                                                   |  |  |

| SPICE elements                                            | * 11 p4 VDD 200 200                                                                                                 |  |  |

| .ends * [MCP End]                                         |                                                                                                                     |  |  |

|                                                           | SPICE elements                                                                                                      |  |  |

|                                                           | .ends                                                                                                               |  |  |

#### Pins of net **Electrical node** Netname

#### .subckt board bl

- \* [MCP Begin]

- \* [MCP Ver] 1.1

- \* [Structure Type] PCB

- \* [MCP Source] board extraction tool

- \* [Coordinate Unit] mm

- \* [Connection] pkg1 pkg balls 4

- [Connection Type] PKG \*

- [Power Nets]

- pin 1 b1 VDD 0.0 0.0

- pin 2 b1 VDD 0.0 0.2

- pin 3 b1 VDD 0.2 0.0

- \* pin 4 b1 VDD 0.2 0.2

- \* [MCP End]

```

--- SPICE elements ---

```

.ends

#### Example of VDD net across chip-pkg-board

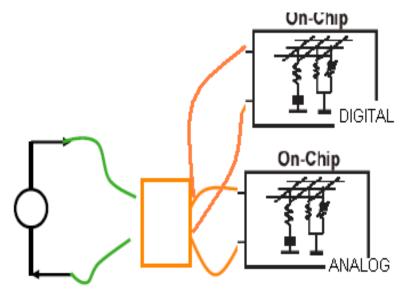

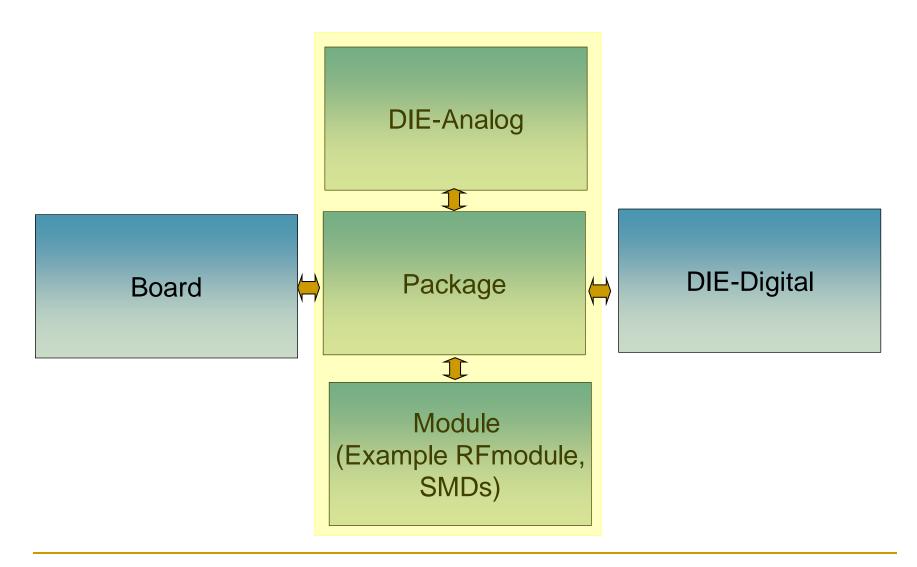

- Analyze power-delivery to ICs when Package rails supply power to

- different ICs that could be digital and/or analog

- RF-modules and Passive/Active SMDs

- Need Schematic driven Mixed Signal Simulations to process IR-drop at power-rails

PDN supplying Analog and Digital multi-DIE system

## MCP Extensions for Mixed Signal SiP -Current MCP scope

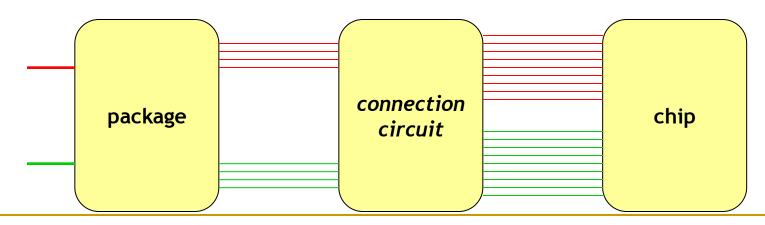

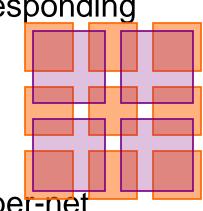

- Electrical connectivity of models with disparate pin grouping

- Support for mapping of different electrical port-groups across different structures

- As an example

- a package model with 2-by-2 grid-based pin grouping

- a chip model with 3-by-3 grid-based pin grouping

- desired is an electrical circuit to interface between an 8 node circuit and an 18 node circuit

- Optional Column for mapping of electrical nodes across structures

Package: .Subckt bp1 dp1

- Caution: Electrical connectivity with disparate pin grouping

#### Examine the nodes of the each net

- for overlapping pin group domains, the corresponding nodes are shorted together

- (1,1) node shorts together {(1,1), (1,2), (2,1), (2,2)} nodes

- (1,2) node shorts together {(1,2), (1,3), (2,2), (2,3)} nodes

- (2,1) node shorts together {(2,1), (2,2), (3,1), (3,2)} nodes

- (2,2) node shorts together {(2,2), (2,3), (3,2), (3,3)} nodes

alternately

- (2,2) node shorts together {(1,1), (1,2), (2,1), (2,2)} nodes

- all nodes are shorted together, reducing to per-net connectivity

- instead of 8 or 18 node electrical connectivity it is actually 2 node connectivity

#### Recommendation

- Connecting two disparately pin-grouped models is possible by choosing to short together electrical nodes that have overlapping pin domains

- but it can reduce the effective resolution of the model at the chip/package interface

- Useful in case of early debugging and quick connectivity

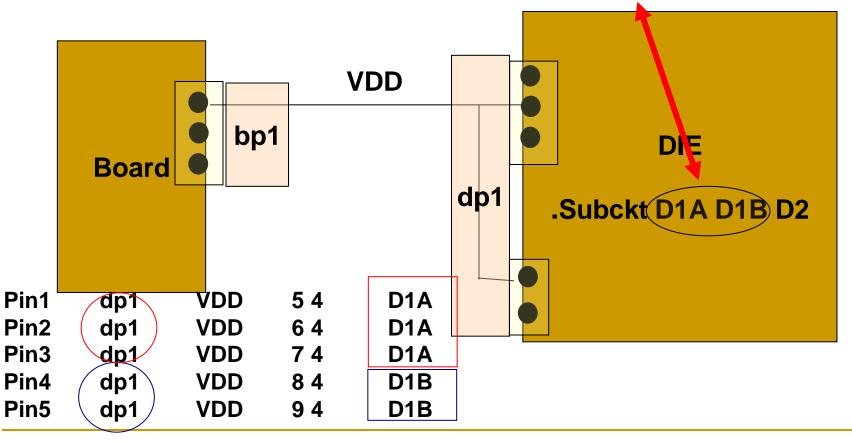

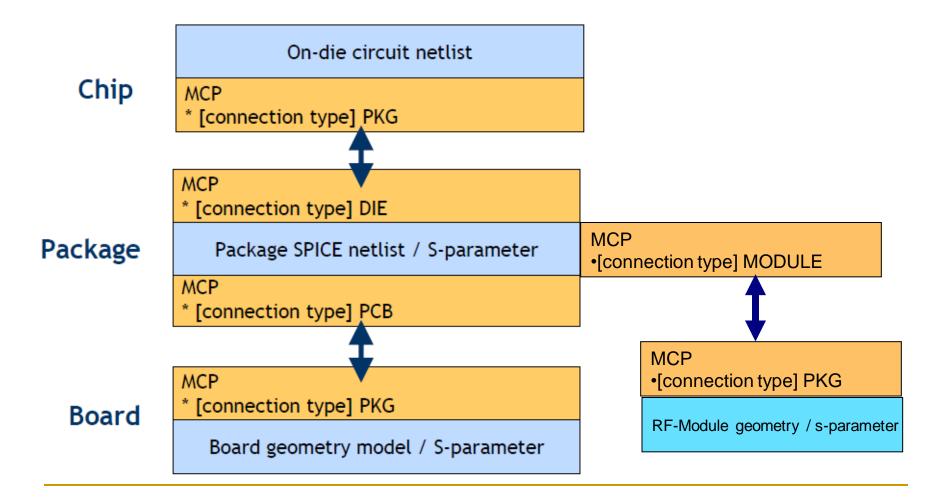

- Support for Modules as connect type structures

- Mixed Signal SiPs would have elements other that ICs like

- RFmodules

- Metal Passive structures

- SMD components

- Silicon Interposers

- These structure draw power impacting PDN loading and hence we need to support [Module] category besides IC, Package and Board

- Support for Modules as connect type structures

- Connection by Refdes besides X-Y location

- In order to connect to structures that are SMD or metal-passive structures on SiP – usually a case for Mixed Signal SiP, it becomes difficult to connect by X-Y locations.

- Early analysis may require quick way of stitching the models across structures and minor placement or resolution changes can cause X-Y mapping to fail.

- Optional column showing connection by REFDES makes easy mapping for Mixed-Signal modules and early trials

- Examples of connecting interfaces could be

- IO-cellname (DIE IO)

- R1:1 (pin 1 of R1)

- CONN:1 (pin1 of PCB connector)

- my\_model\_opamp:3 (port-3 of opamp subcircuit)

- Connection by Refdes besides X-Y location

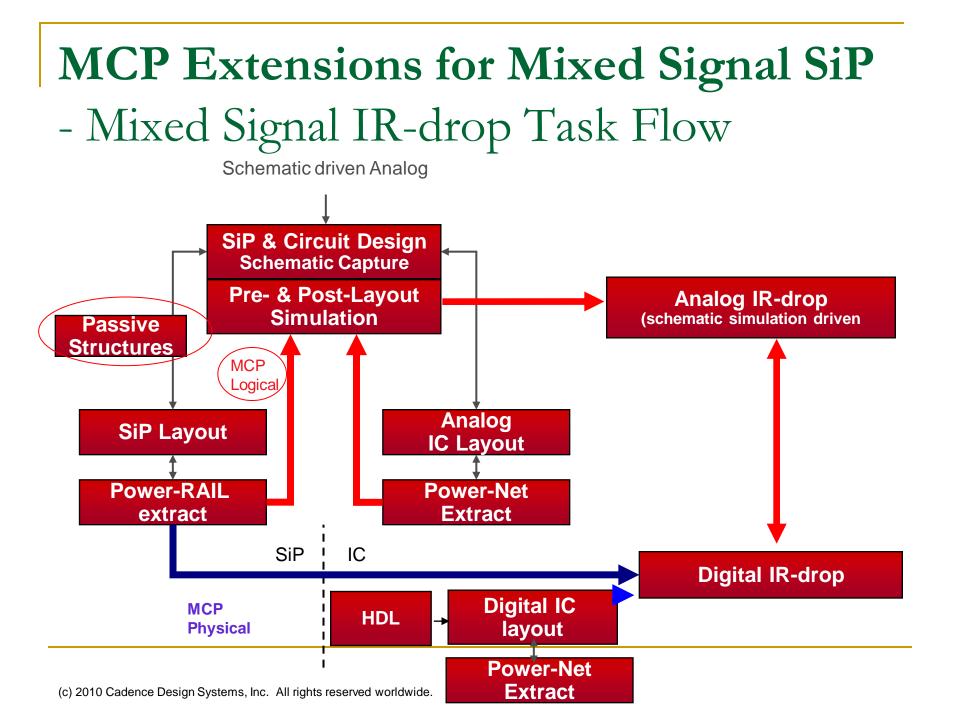

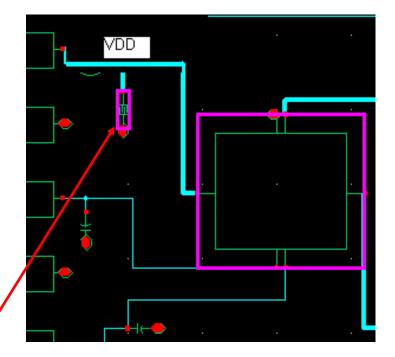

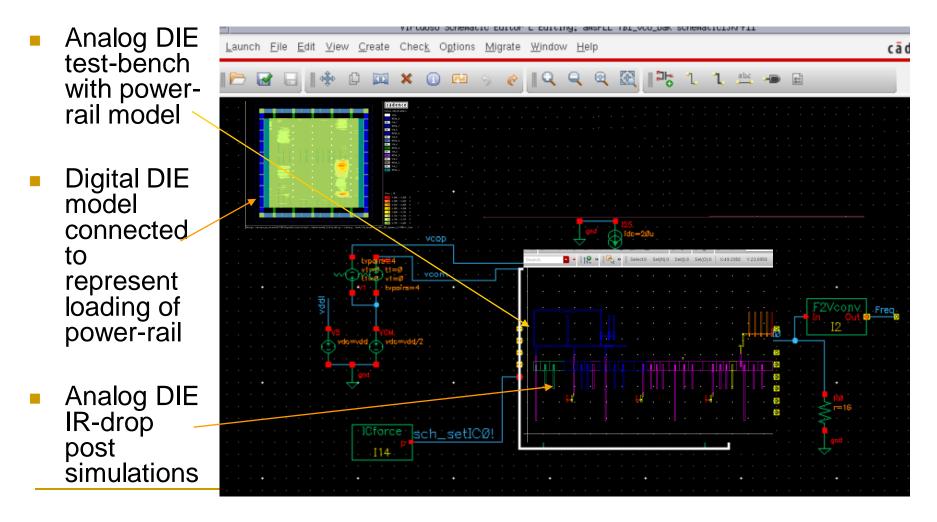

- Simulating Analog DIE in package schematics with loading from passive structures connected to DIE

- The simulation data is postprocessed to obtain IR-drop at power-rails

| [connection type MODULE] |     |     |            |

|--------------------------|-----|-----|------------|

| Pin1                     | dp1 | VDD | <b>5</b> 4 |

| Pin2                     | dp1 | VDD | 6⁄4        |

| Pin3                     | dp1 | VDD | 74         |

varistor1:2 //Reference\_design:pin// varistor2:2

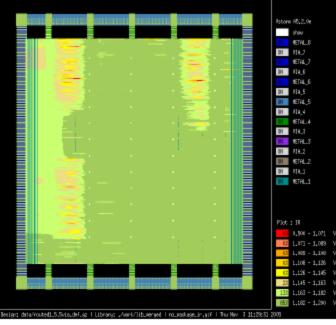

## MCP applications: Digital DIE IR-drop - Digital DIE in context of package model

#### Simulation results of Vdd rail: Dynamic IR-Drop

#### Without package effects worst-case IR drop : 147.5mV

worst-case IR drop : 179.3mV

#### MCP applications: Analog DIE IR-drop -Analog DIE in context of package model & Digital DIEmodels

#### Summary: MCP format updated in context of Mixed Signal contents [MCP Ver] 1.1 \* [Structure Type] {DIE | PKG | PCB } Device Info (self) \* [MCP Source] source text Device Info (external) [Coordinate Unit] unit [Connection] connectionName (partName) numberPhysicalPins [Connection Type] {DIE|PKG|PCB} Module Connection Info \* I/F part-ref [Power Nets] \* I/F electrical column pinName modelNodeName netName x y node column \* pinName modelNodeName \* netName x v Ground Netsl \* \* pinName modelNodeName netName х y Pin Info \* \* pinName modelNodeName netName х v [Signal Nets] \* pinName modelNodeName netName x v pinName modelNodeName netName x v [MCP End]

# cādence<sup>®</sup>