## Subckt Package Model in IBIS

(Originally presented on November 4, 2009 in Shanghai China)

Dr. Wenliang Dai (wldai@cadence.com)

**Cadence Design Systems, Inc.**

Asian IBIS Summit, Tokyo, Japan, November 6th 2009

- Standard IBIS Package Model Overview

- Requirements on IBIS Package Model in High Speed Circuit Analysis

- Proposed IBIS Subckt Package Model

- Summary

#### Standard IBIS Package Model Overview

- Existing Simplified IBIS Package Model

- Single RLC value

- Customized IBIS Package Model

- Segmented/Forked RLC value

- Coupled IBIS Package Model

- RLC Matrix value

- Pin Mapping in Pin Numbers and Model Data Section

- 1:1 mapping of die pins to package pins

- Simple RLC for each signal, power and ground pin

- Standard IBIS Package Model Overview

- Requirements on IBIS Package Model in High Speed Circuit Analysis

- Proposed IBIS Subckt Package Model

- Summary

#### **Extracted Package Model by Field Solvers & Measurements**

- Current Standard IBIS Package Model Format

- Very simple RLC value with 1:1 mapping of BGA pins to Die pins

- It makes little sense for each pwr/gnd pins

- Subckt Model for Coupling Signal, Power and Ground Nets from Field Solvers

- Complex Spice subckt with high accuracy & efficiency by pwr/gnd pins group process

- Touchstone Format S Parameter Model from Field Solvers or Measurement

- S/Y/Z parameter model and related Subckt model can be obtained conveniently

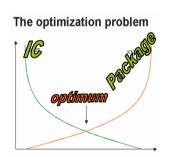

- Today's power & SSN analysis with lower voltage and higher current require high accurate power, ground (including decaps) and signal nets coupling circuit model for higher simulation accuracy and efficiency

- Subckt or S parameter models are required

- Pin-Port Mappings are required by full system high speed circuit analysis

Notes: Current IBIS Package Model is NOT ENOUGH for high speed circuit analysis, especially for Power analysis & SSN simulation

#### How to Use the Extracted Subckt Package Model

- Create the Whole Circuit Netlist by Editing the Connection between the Extracted Spice Package Model and S Parameter Model in Text File Format

- Good

- Create the Connection between the Package Model and other Models in GUI with additional Pin-Node Mapping file Manually

- Better

- Create the Connection between Package Model and other Model automatically through Enhanced IBIS Package Model

- Best and it's a Standard

Notes: Consume complicated/coupled signal & power net subckt in IBIS models

- Standard IBIS Package Model Overview

- Requirements on IBIS Package Model in High Speed Circuit Analysis

- Proposed IBIS Subckt Package Model

- Summary

## **Existing IBIS Package Model in V5.0**

```

[Define Package Model]

|-- [Manufacturer]

|-- [OEM]

|-- [Description]

|-- [Number Of Sections]

|-- [Number Of Pins]

|-- [Pin Numbers]

Len, L, R, C, Fork, Endfork

|-- [Model Data]

Banded_matrix, Sparse_matrix,

|-- [Resistance Matrix]

Full_matrix

|-- [Bandwidth]

|-- [Row]

Banded_matrix, Sparse_matrix,

- [Inductance Matrix]

Full matrix

|-- [Bandwidth]

|-- [Row]

Banded_matrix, Sparse_matrix,

-- [Capacitance Matrix]

Full matrix

|-- [Bandwidth]

|-- [Row]

|-- [End Model Data]

|-- [End Package Model]

```

#### What's New in the Enhanced IBIS Package Model

- [Define Package Model]

- [Manufacturer]

- [OEM]

- [Description]

- [Number Of Sections]

- [Number Of Pins]

- [Pin Numbers]

- [Model Data]

- [End Model Data]

- [End Package Model]

It also supports multiple Subckt models in one package with its pin node mapping

[Define Package Model]

[Manufacturer]

[OEM]

[Description]

[Number Of Pins]

[Number Of Sections]

[Pin Numbers]

[Model Data]

[End Model Data]

[Subckt Package Model]

[Pin-Node Mapping]

[End Pin-Node Mapping]

[Subckt Model Data]

[End Subckt Model Data]

[End Subckt Package Model]

<u>[End Package Model]</u>

## Keywords for Proposed IBIS Package Model

**Keywords:** [Subckt Package Model] **Keyword: [Subckt Model Data]** Required: Yes Description: Indicates the beginning of the formatted subckt package model data, that can include the spice subckt or s parameter model keywords. [Pin-Node Mapping] [End Pin-Node Mapping] [Subckt Model Data] [End Subckt Model Data] **Keyword: [End Subckt Package Model]** Required: Yes Description: Indicates the end of the formatted model data. Other Notes: In between the [Subckt Package Model] and [End Subckt Package Model] keywords is the pin node mapping, data itself of subckt package model. [End Subckt Package Model]

Notes: The goal is to specify a complicated spice-like subckt package model instead of standard simple RLC package model to be used by the keyword Subckt Package Model.

## Keywords for Proposed IBIS Package Model

```

Keywords:

Keyword: [Pin-Node Mapping]

Required: Yes

Description: Indicates the beginning of the formatted Pin Node mapping data for

subckt package model data.

[Pin-Node Mapping]

Keyword: [End Pin-Node Mapping]

Required: Yes

Description: Indicates the end of the formatted pin port mapping data.

Other Notes: In between the [Pin-Node Mapping] and [End Pin-Node Mapping]

keywords is the pin port mapping data itself. The data is a set of subckt node

name like N001, pin name like VDD01 and net name like Net1 as below

N001 VDD01 Net1

N002 VDD02 Net1

N003 VDD03 Net2

N004 VSS01 Net3

The net name like Net1 is "OPTIONAL"

[End Pin-Node Mapping]

```

## Keywords for Proposed IBIS Package Model

```

Keywords:

[Subckt Model Data]

Keyword: [Subckt Model Data]

Required: Yes

Description: Indicates the beginning of the formatted subckt package model data,

that can include the subckt or s parameter model keywords.

Keyword: [End Subckt Model Data]

Required: Yes

Description: Indicates the end of the formatted subckt model data.

Other Notes: In between the [Subckt Model Data] and [End Subckt Model Data]

keywords is the data itself for subckt package model.

The data is a set of spice subckt or S parameter model as below

Spice: ".subckt PowerModel N001 N002 N007 N008 ... .ends PowerModel"

Or S parameter: ".MODEL name sp [DATA=(npts ...)] [DATAFILE=filename]

[End Subckt Model Data]

```

- Standard IBIS Package Model Overview

- Requirements on IBIS Package Model in High Speed Circuit Analysis

- Proposed IBIS Subckt Package Model

- Summary

### **Summary**

- Requirements on IBIS Package Model

- Accurate Power/SSN analysis with a complex package model

- Proposed Subckt Type in IBIS Package Model

- Spice circuit or S parameter data

- Applications for IBIS Subckt Package Model

- IC-Package-Board co-design flow and Design Link

#### **Action items**

- Add the proposed subckt package model keywords into standard IBIS package part

- IBIS parser parses the subckt package keywords

- Similar use model to existing lumped package model

- EDA tools consume the subckt package model to create circuit netlist

# cadence™