# Easy IBIS model handling with Simulation Kit

### IBIS diffusion status

# The visibility of IBIS

Recognized as de facto standard models of Transmission-line Simulator for PCB Design.

#### Model diffusion level

Provided by various semiconductor venders

### Tool diffusion level

Various associated practical level tools are available

Looking overall, IBIS environment is thoroughly satisfied.

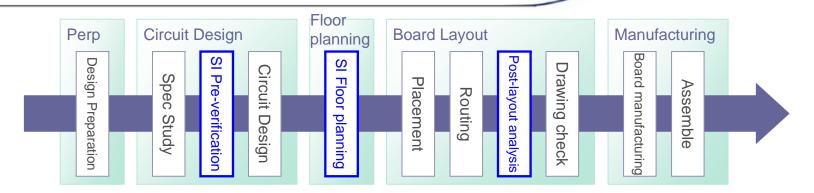

### IBIS Simulation Flow

# Circuit Design

## PCB Layout

### Manufacturing

### Pre-layout analysis

- Routing path

- Circuitry

- Passive component

#### Floor planning

•SI verification at placement phase

#### Post-layout analysis`

•SI verification at post layout phase

Copyright, Zuken Inc. 2008

### Trend in use of IBIS

- Division-of-roles type usage i.e. Operation by Full-time Analysis Engineer is very common.

- Operation by Normal Designer is much less common (different from each customer).

Investigate the cause by listening to the designer's voice...

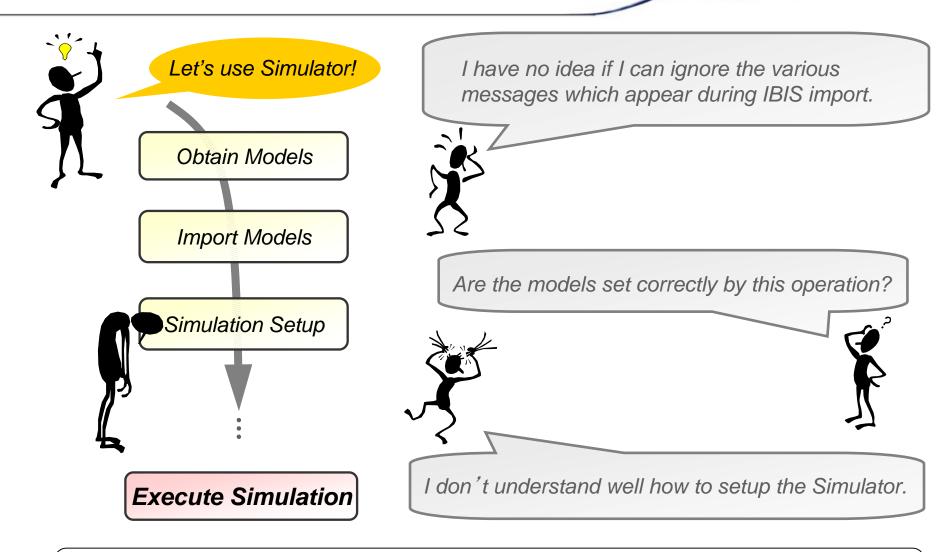

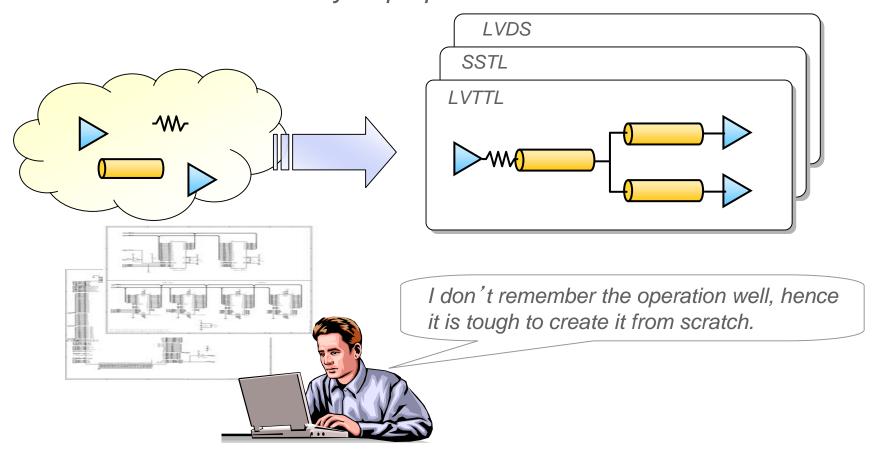

# Voice of Designers

I cannot use the simulator at once due to a complex preparation work!

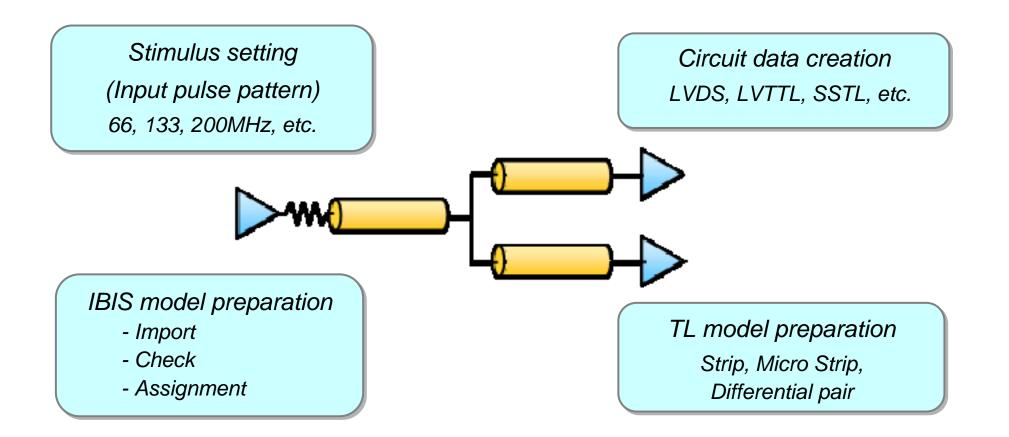

# Required preparation task for analysis

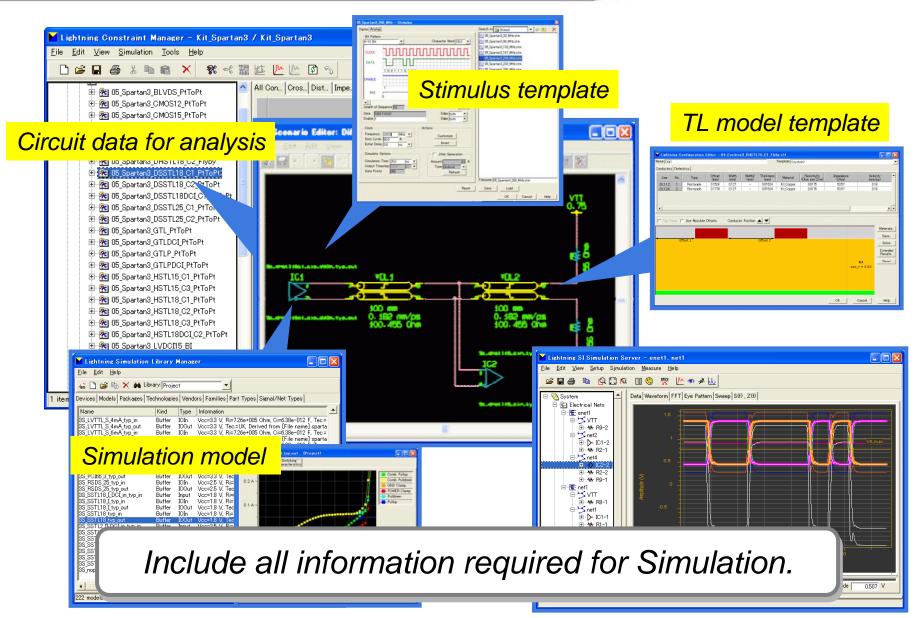

Complicated preparation task can be reduced by providing these initial templates.

### Create the circuit data for analysis purpose

Provide the circuit data for analysis corresponding to various I/O buffers.

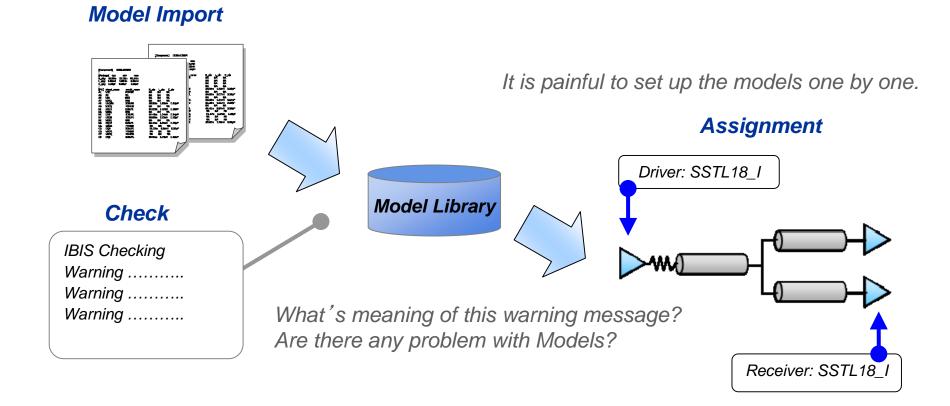

### Preparation of IBIS models

All processes from the model import to the model assignment are implemented in advance.

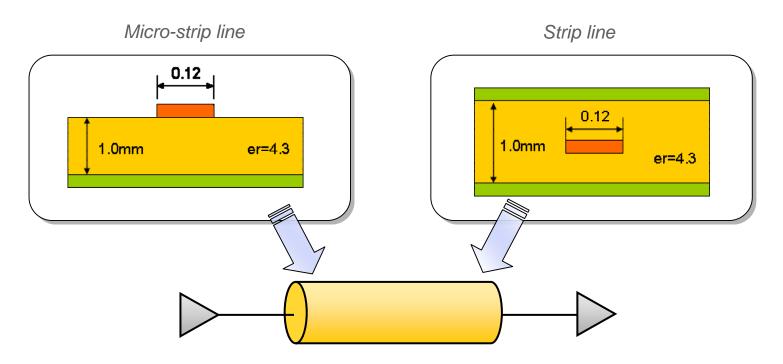

# Preparation of Transmission Line Model

TL model preparation also takes time.

Provide the template or something is required.

Template of the cross-section models of the transmission line is pre-defined.

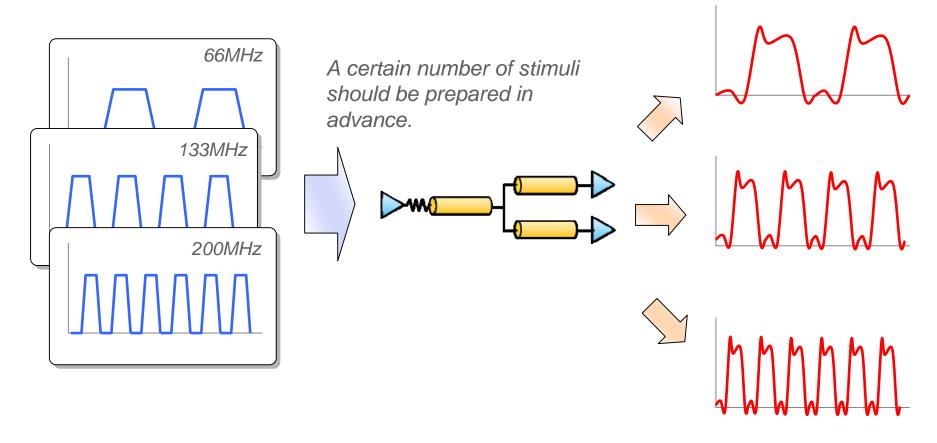

# Setup of stimulus (input pulse pattern) for Simulation

Several Templates of stimulus for simulation are predefined.

### Contents of Simulation Kit

# Simulation Kit Release History

13-Sep-2007 Release the Kit for Altera Arria GX FPGA

17-Oct-2007 Release the Kit for Xilinx Virtex-5 FPGA

20-May-2008 Release the Kit for Altera Cyclone III FPGA

10-Oct-2008 Release the Kit for Xilinx Spartan-3 FPGA

We are continually expanding the simulation kit to promote the utilization of the simulator by the designer.