# Enhanced Mπlog Models for Power Integrity Analysis.

Modeling from simulation and measurement, IBIS data extraction, crossvalidation

**A.** Girardi<sup>1</sup>, I.S. Stievano<sup>2</sup>, R. Izzi<sup>1</sup>, T. Lessio<sup>1</sup>, F.G. Canavero<sup>2</sup>, I. Maio<sup>2</sup>, L. Rigazio<sup>2</sup>

<sup>1</sup> Numonyx Italy S.r.I., <sup>2</sup> Politecnico di Torino, Italy

Ref. contacts: {antonio.girardi@numonyx.com, igor.stievano@polito.it}

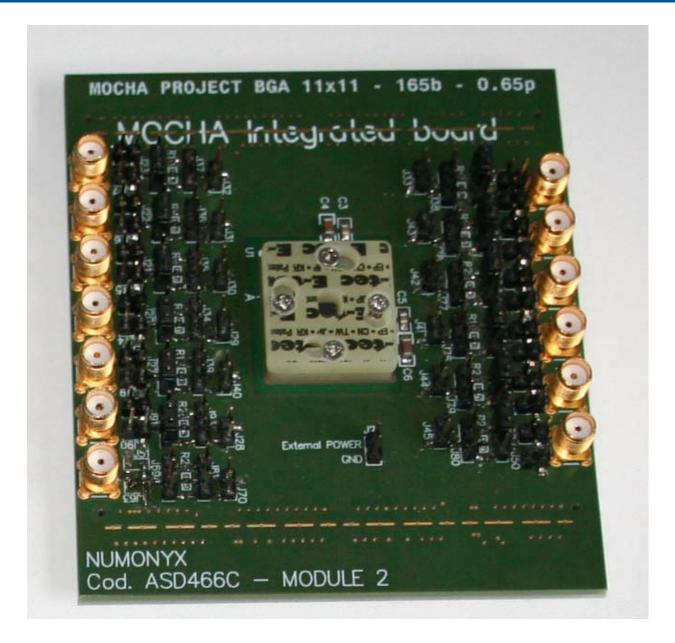

## MOCHA, MOdelling and CHAracterization for SiP - Signal and Power Integrity Analysis

(www.mocha.polito.it)

☐ European Project FP7-ICT-2007-1\* (Jan 2008 – Mar 2010)

"Develop reliable modelling and simulation solutions for SiP design verification"

#### ☐ Partecipants:

- Numonyx Italy Srl (Italy) [Coordinator]

- Politecnico di Torino (Italy)

- Cadence Design Systems Gmbh (Germany)

- Agilent Technologies (Belgium)

- Universidade de Aveiro (Portugal),

- Microwave Characterization Center (France)

#### ■ Work Packages

- WP1, IC power integrity model

- WP2, IC buffers' innovative modelling approach

- WP3, SiP design and verification EDA platform

WP4, SiP signal integrity measurement platform

\* The research leading to these results has received funding from the European Community's Seventh Framework Programme FP7-ICT-2007-1 under the MOCHA (MOdeling and CHAracterization for SiP - Signal and Power Integrity Analysis) grant n. 216732.

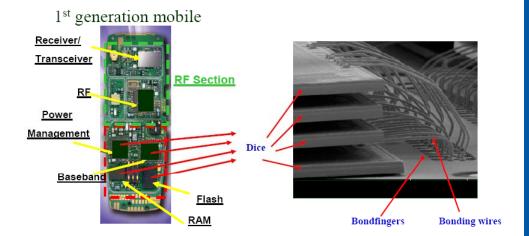

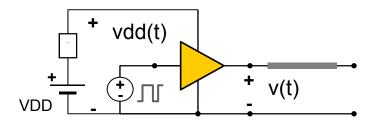

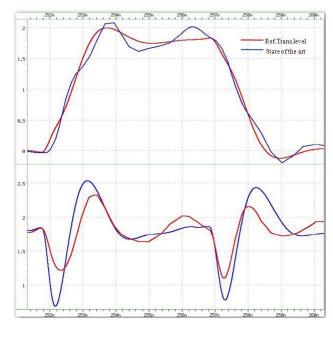

#### **WP2** overview

Objective: Development of accurate and efficient models of digital ICs

Overcome current limitations of existing models

e.g., state-of-the art models allow only for limited power supply variations

--- Ref. trans. level

State-of-the art

☐ Generate models from measurements & simulations

#### WP2 achievements (i)

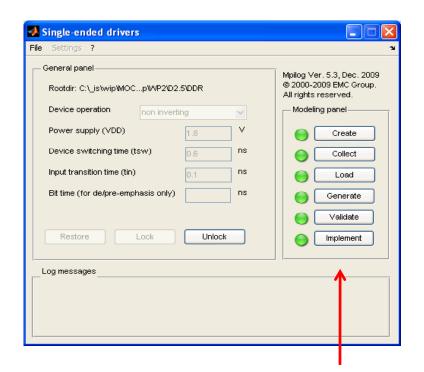

□ Availability of the General structure of the extended model for digital buffers

□ Procedure for parameter estimation from simulation / measurement

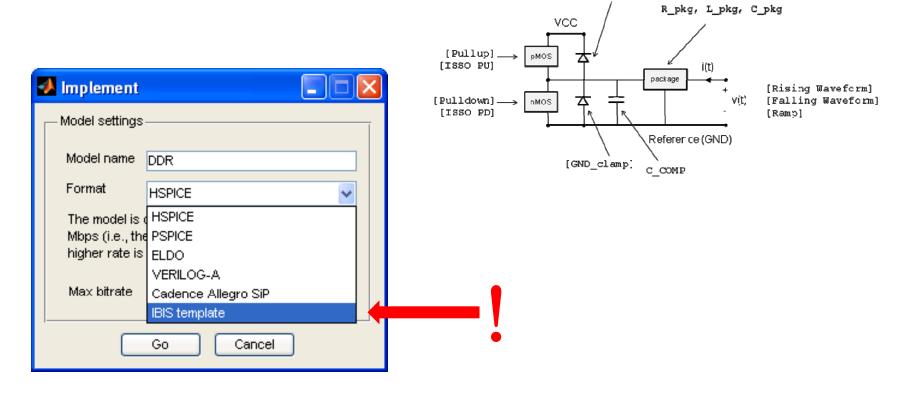

□ Model implementation in different formats (HSPICE, ELDO, VERILOG-A,...)

□ Application to test cases (proprietary and third party devices) from simulation

#### WP2 achievements (ii)

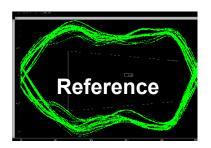

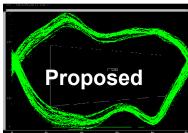

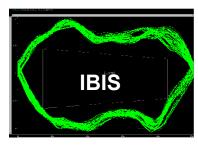

☐ Model Accuracy, second test case (estimation from simulation)

| Reference      |  |  |

|----------------|--|--|

| (trans. level) |  |  |

| IBIS           |  |  |

| Proposed       |  |  |

| (MπLOG)        |  |  |

| Eye opening | Error | CPU           |

|-------------|-------|---------------|

| 72%         | -     | 773 s         |

| 78.8 %      | 9.5 % | 13 s<br>(59x) |

| 73.8 %      | 2.5 % | 31 s<br>(25x) |

- ✓ Improved Accuracy

- √ High efficiency

#### WP2 achievements (iii)

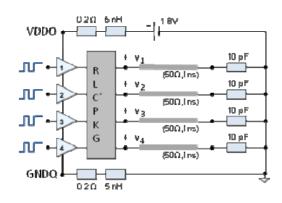

□ Design two test boards for the characterization of the IC ports of the MOCHA test cases

e.g., first test case, DQ0 I/O buffer

Device models

from transient

port voltage and

current

responses

recorded during

IC normal

operation

## WP2 achievements (iv)

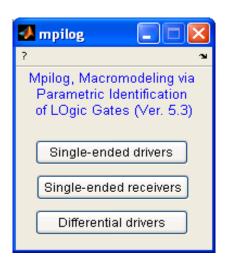

**☐** Tool for the interactive generation of IC models

Mπlog ver. 5.3,

available @

www.emc.polito.it

Guided step-by-step modeling procedure

## WP2 achievements (v)

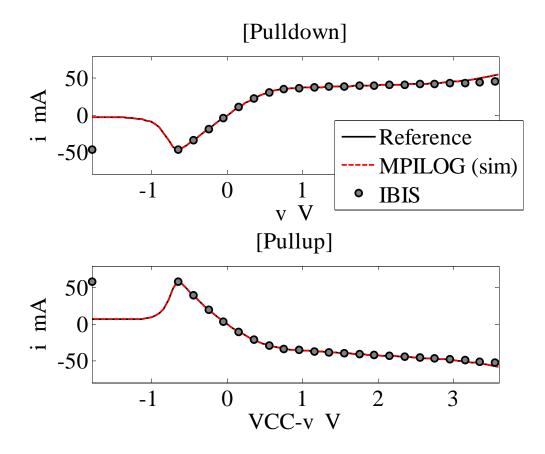

□ procedure for the extraction of device characteristics suggested by IBIS from the estimated models

[POWER\_clamp]

#### X-Validation (i)

**Test case:** 512Mb LPDDR third party device, in 70nm technology and clock frequency of 133MHz.

#### Models:

- □ Reference Transistor-level

- **□** IBIS

- $\square$  M $\pi$ log (from simulation)

- $\square$  M $\pi$ log (from measurements)

|        | IBIS  | MPLOG (sim) |

|--------|-------|-------------|

| С_СОМР | 3.1pF | 3.045 pF    |

#### X-validation (ii)

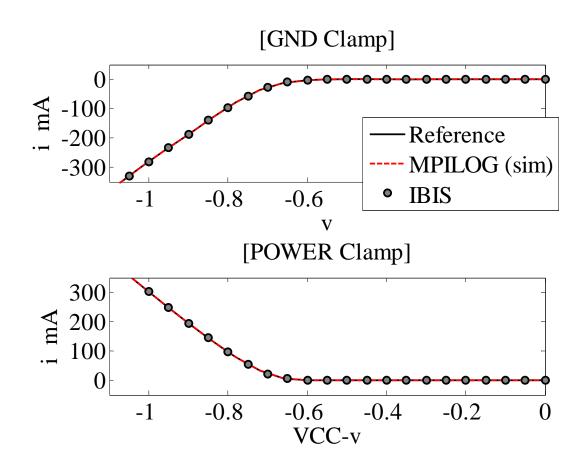

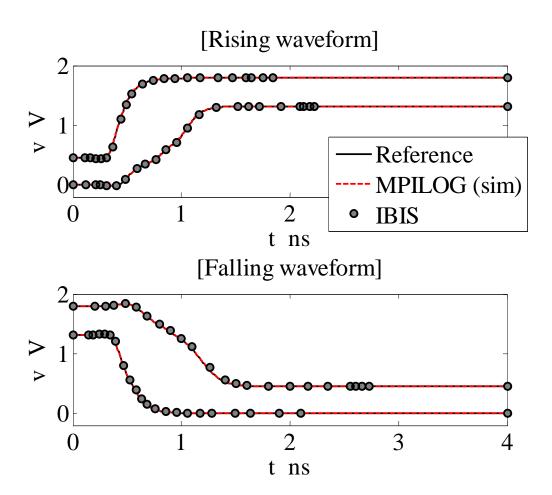

## X-validation (iii)

## X-validation (iv)

## X-validation (v)

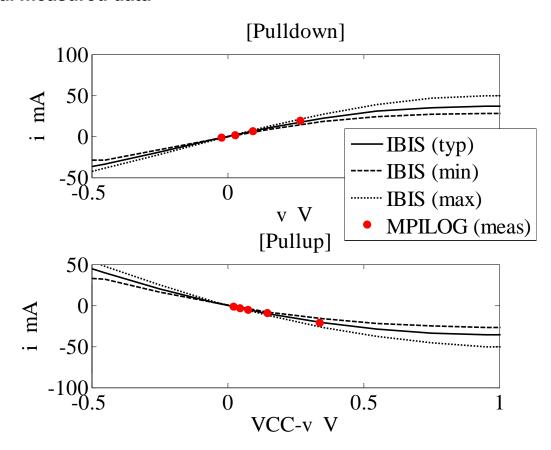

#### ...model from real measured data

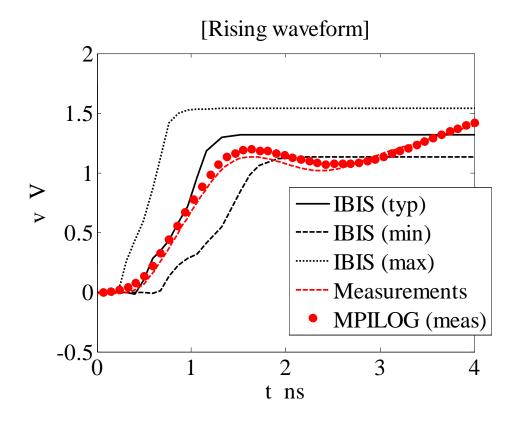

## X-validation (vi)

#### ...model from real measured data

R\_fixture = 47 Ω L\_fixture = 18 nH C\_fixture = 7.4 pF V\_fixture = 0V