# Computer-Assisted Modeling of Digital I/O Buffers for IBIS

F.G.Canavero<sup>1</sup>, I.A.Maio<sup>1</sup>, I.S.Stievano<sup>1</sup>, M.Swaminathan<sup>2</sup>, P.Franzon<sup>3</sup>

<sup>1</sup> Politecnico di Torino, ITALY (http://www.eln.polito.it/research/emc)

Georgia 1/2 GaTech, Atlanta, USA

NC STATE UNIVERSITY <sup>3</sup> NC State University, USA

### **Discussion within CPMT – TC12**

Electrical Design, Modeling and Simulation (EDMS, TC-12) sub-commitee http://www.ewh.ieee.org/soc/cpmt/tc12/

- EDMS sub-committee works on the standardization of design tools and design methodologies in packaging

- Initiative for "Practical Macromodels for Digital I/O"

- → First meeting @ EPEP, Oct. 2004 in Portland, Oregon, USA. http://www.ewh.ieee.org/soc/cpmt/tc12/standardization\_files/IBIS\_TC12a.ppt

SPI (Signal Propagation on Interconnets) IEEE Workshop, May. 10-13, 2005 in Garmisch-Partenkirchen, Germany (c.f.p. at http://www.spi.uni-hannover.de/)

### **I/O Buffers Macromodeling**

#### • Required Goals:

- IP protection

- Vendor-independent format

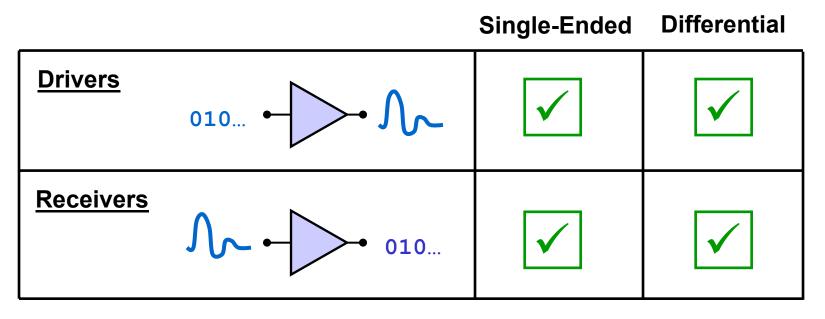

- Have to capture TX, RX, and package parasitic essentials

- Sufficiently accurate to be useful

- Easy to automatically generate from Spice and Measurements

- Easy to verify

- Easy and fast to simulate

### I/O Buffers Macromodeling Current status

#### **Circuit-based modeling**

(native IBIS)

- standard,

- large data/model libraries,

- EDA tools support...

specification and tools from http://www.eigroup.org/ibis/

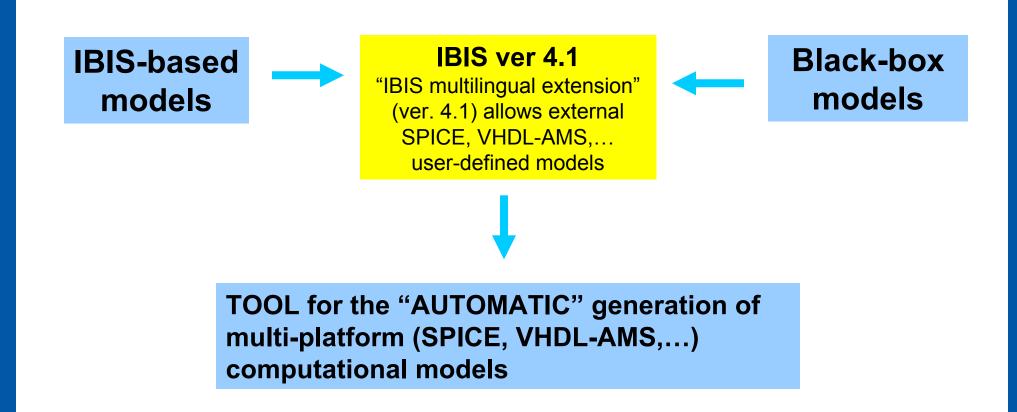

#### **Black-box modeling**

i=F(v,d/dt)

...aimed at improving the modeling of latest technologies and high-order effects

- LVDS drivers with pre-emphasis

- DDR memories,

- power supply ports...

e.g., parametric modeling

### I/O Buffers Macromodeling The way forward

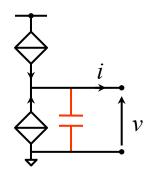

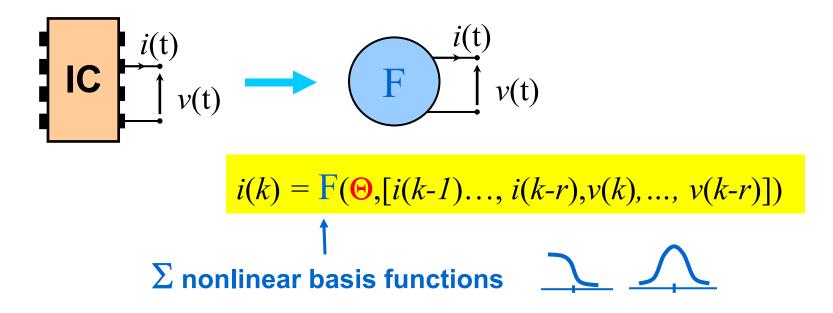

### Black-box modeling @ Politecnico di Torino

$M\pi log^{\mathbb{C}}$  (Macromodeling via parametric identification ( $\pi$ ) of logic gates): Method & Tool

#### Model parameters ( $\Theta$ ) via system identification methods

### $M\pi log$ features

+ { Power Supply ports Temperature effects

|                                                    | Mπ <i>log</i> Tool                                                                                                                                                                                                                                                                              | Mpilog 🔲 🔀                                     |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| <b>Steps 🔤 🖂 🔀</b><br>File Help 🛛 🛥                | Mpilog - Single-Ended Drivers Macromodeling                                                                                                                                                                                                                                                     | Macromodeling via<br>Parametric Identification |

| 1. Port excitation<br>Create                       | File       Help       n         Device details                                                                                                                                                                                                                                                  | of LOgic Gates Single-Ended Drivers About Quit |

| Collect                                            | Time step (T)       10       ps       Macromodel - Implement         Driver input signal       . amplitude       1.8       V       Model settings         . rise-time       0.1       ns       Model format       HSPICE         . fall-time       0.1       ns       Model format       HSPICE | Units {V,A,s}                                  |

| 3. Macromodel<br>Generate<br>Validate<br>Implement | Go Bit time 1 ns Bit stream "01011"                                                                                                                                                                                                                                                             | View                                           |

|                                                    | Tool available on request (igor.stievano@po                                                                                                                                                                                                                                                     | olito.it)                                      |

🗯 emc group

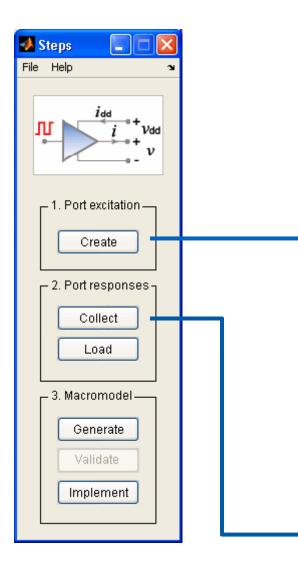

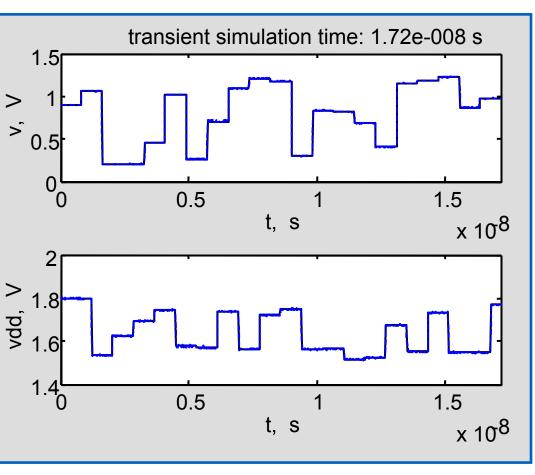

# $M\pi log$ Tool

RUN YOUR PREFERRED CIRCUIT SOLVER (e.g. SPICE)

### $M\pi log$ Tool

eme group

## $M\pi log$ Tool

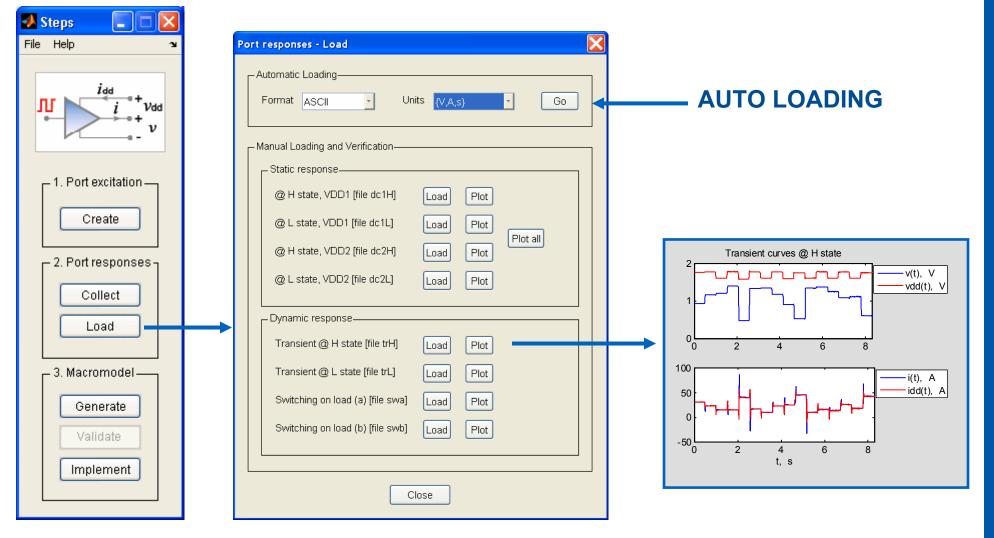

| Steps                                                                                                       | Macromodel - Generate                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <i>i</i> dd<br><i>i</i> +Vdd<br><i>v</i><br><i>v</i><br>1. Port excitation<br>Create<br>- 2. Port responses | Advanced settings<br>Dynamic order<br>2<br>Maximum model size 5<br>Show curves<br>Go<br>Close                                                                                                     |

| 2. Port responses<br>Collect<br>Load<br>3. Macromodel<br>Generate<br>Validate<br>Implement                  | Close Macromodel - Implement Model settings Model name DRV2 Model format VHDL-AMS2 (external bit stream) Units {VA,s} Bit time 1 ns generates the IBIS file (ver. 4.1) Bit stream "01011" View Go |

enc group.

# **Conclusions (i)**

- $\odot$   $\odot$  IP protection

- ⊕ ⊕ − Have to capture TX, RX, and package parasitic essentials

■

- $\odot \odot \odot \odot$  Sufficiently accurate to be useful

- Or Constraints

Or Co

- ⊕ ⊕ − Easy to verify

■

- $\odot$   $\odot$  Easy and fast to simulate

# **Conclusions (ii)**

Black-box models are expressed by equations that are used **as they are**, without any interpretation

- no data to model conversion needed

- Ilexible modeling methods

- model enhancements do not affect IBIS and IBIS simulator structures

The distribution of black-box models would be a valuable complement to the distribution of behavioral data

### **Acknowledgements**

Thanks to

- ★ GRAPHER for providing the Analog/Mixed-Signal simulator environment (ADVance MS<sup>™</sup> + Eldo<sup>™</sup>)

- Sergio Perazza (Mentor, Italy) for the technical support on Mentors' products

- Arpad Muranyi (Intel) for VHDL templates and code posted on http://www.eda.org/pub/ibis/summits/jun03a/ and http://www.eda.org/pub/ibis/summits/feb04a/