**Stephane Rousseau**

**Customer Marketing Manager**

**System Design Division**

Graphs<sup>®</sup>

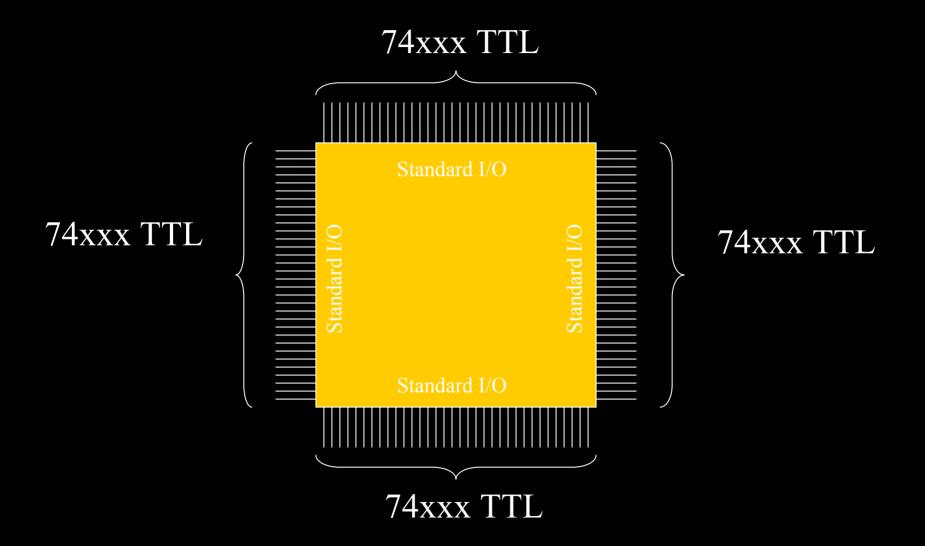

# A Little History ...

#### Then, speeds increased ....

SPICE/Encrypted SPICE models

SPICE/Encrypted SPICE models

SPICE/Encrypted SPICE models

Standard I/O

**SPICE**

- ·Slow

- •Complex

- Encrypted

**SPICE**

**SPICE**

models

Encrypted

IBIS Forum - DATE 2005

Copyright ©1999-2001, Mentor Graphics.

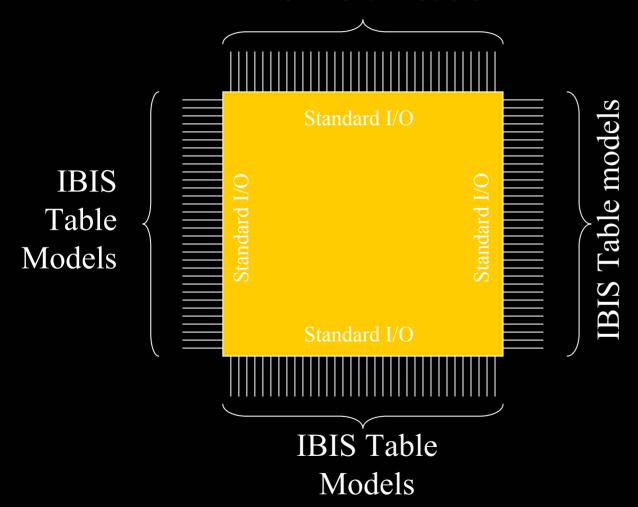

**IBIS Table Models**

**IBIS**

- •Fast

- Simple

- Standard

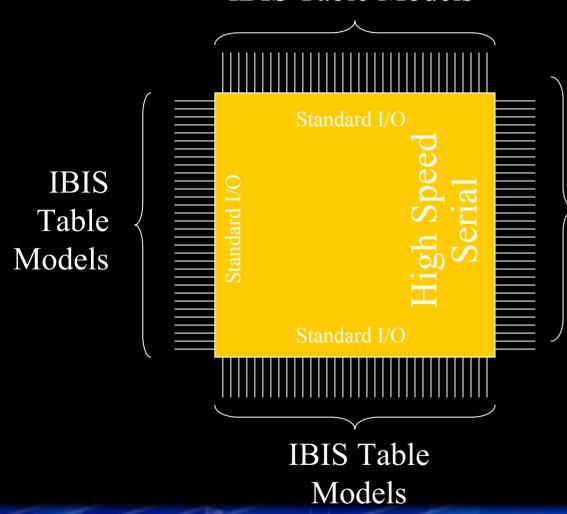

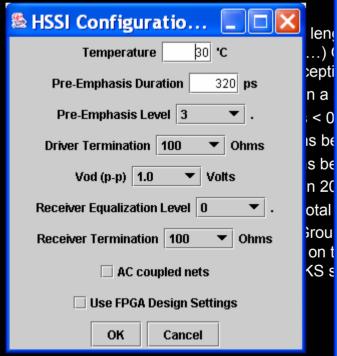

# Then came High Speed Serial I/O ... 2002

**IBIS Table Models**

SPICE /

Encrypted

SPICE

Models

**SPICE**

- ·Slow

- Complex

- Encrypted

#### IBIS Table Models

Standard I/O

IBIS Table Models

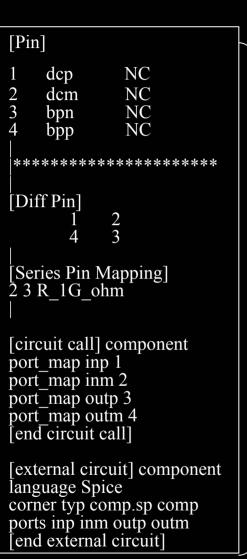

IBIS 4.1 Wrappers SPICE

Encrypted SPICE

Models

Examples & Documentation

**IBIS**

Table

Models

#### **IBIS 4.1 with SPICE**

- IBIS

- Simple to use

- Fast

- Unencrypted

- Standard

- IBIS 4.1/SPICE

- Simple

- Slow

- Encrypted

- Partially Proprietary

- SPICE

- Complex

- Slow

- Encrypted

- Proprietary

## **Better Mousetraps IEEE-1076.1 Analog Modeling** Language

```

library IEEE;

use IEEE.electrical systems.all;

use IEEE.std logic 1164.all;

entity sgx hssi tx icx slow is

generic (ui real : real := 320.0e-12);

type time, internally)

port (terminal a drive, a signal pos,

a signal neg, pre emphas2,

pre emphas1, pre emphas0,

drive sel2, drive sel1, drive sel0,

termsel1 termsel\overline{0} : electrical):

end entity sgx hssi tx icx slow;

```

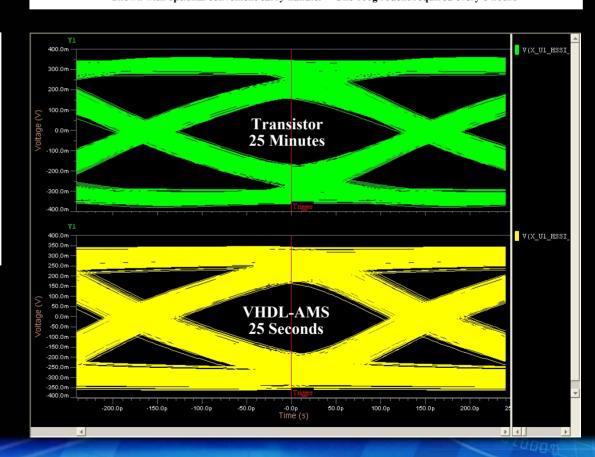

- —Solves speed problem

- —Shields user from SPICE complexity

- **Double IP security**

- —Industry Standard, Non Proprietary

Shown with optional convenient carry handle. \*One 100g rodent required every 8 hours

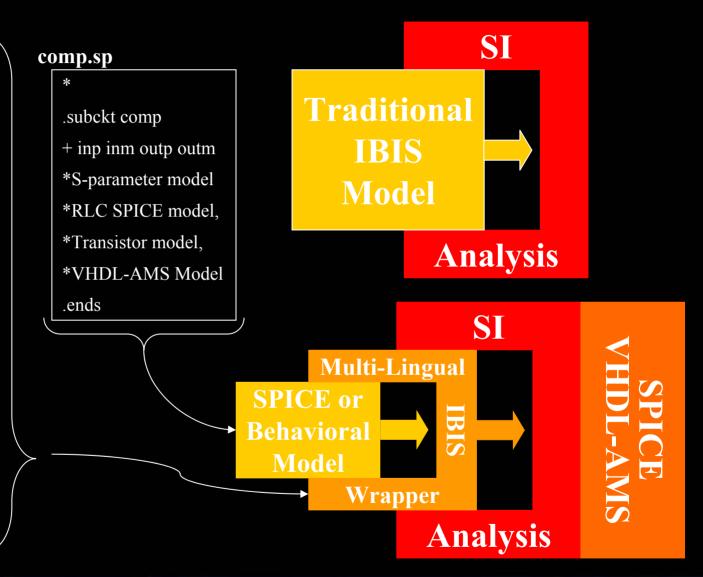

#### IBIS 4.1 with IEEE 1076.1 AMS ...

2003

**IBIS Table Models**

**IBIS** Table Models Standard I/O

IBIS Table Models

IBIS 4.1 Wrappers

IEEE 1076.1 AMS

Examples & Documentation

#### **IBIS 4.1 with IEEE 1076.1 AMS**

- IBIS

- Simple to use

- Fast

- Unencrypted

- Standard

- IBIS 4.1/SPICE

- Simple 🏽 🚺

- Slow

- Encrypted

- Proprietary

- HSPICE

- Complex

- Slow

- Encrypted

- Proprietary

- IBIS 4.1/IEEE1076.1

- Simple

- Fast

- Unencrypted

- Standard

#### **IBIS 4.1 Standard**

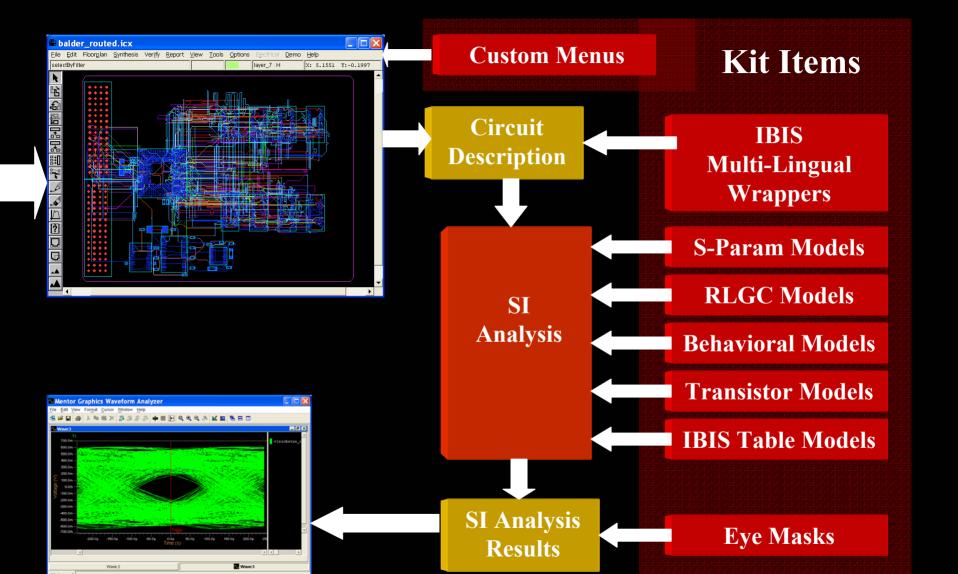

### What Next?

- Some more modeling enhancements

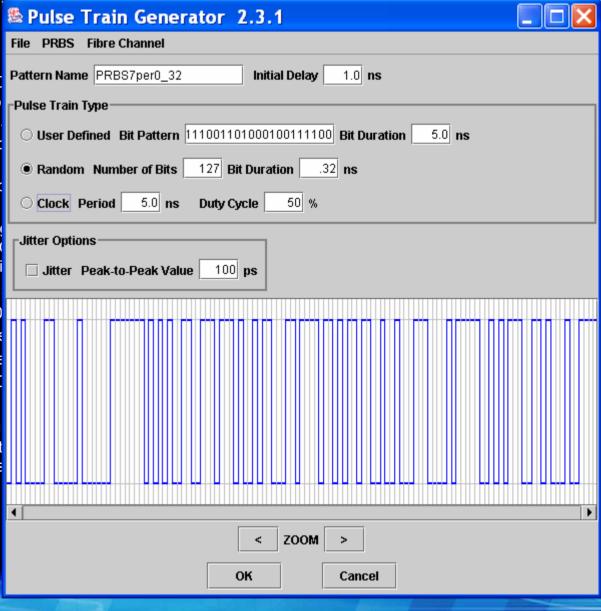

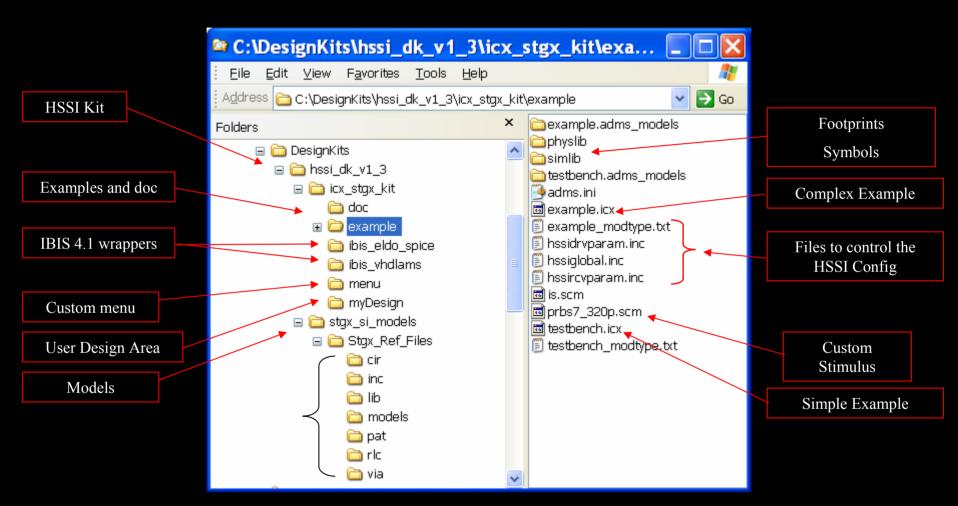

- High Speed Design Kits

**Constraints**

**Reference Designs**

Reuse Blocks

**Kit Items**

**Constraints**

**Footprints**

**Reference Designs**

Drop-in Core Layout

#### **Kit Items**

#### Routing Rules

- All signals within a given "QI FPGA's (U110 and U148) to deviation is +/- 0.050 inches

- Keep the distance from the ρ less than 750 mils.

- Keep the distance from the r

#### **Tour de Kit**

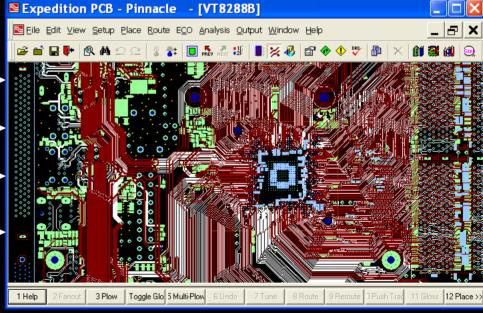

# **Design Kits Development**

## **Design Kits – Benefits to Customers**

- Be up and running faster

- Have access to more than just Models, maximize efficiency and productivity

- Saves significant time

- Saves valuable resources

- Saves cost

# Design Kits – Benefits to IC/FPGA Vendors

- Facilitates adoption of vendor silicon

- Better service to their customers

IBIS Forum - DATE 2005

# Design Kits – Benefits to EDA vendors

- Facilitates adoption of tools

- Maximize tool usage

- Better service to their customers

### **IBIS Committee/Forum**

Should maybe be another place to drive High Speed Design Kits requirements and make proposal for a common format/content?