# IBIS in the Design Chain of Noise Modelling

Manfred Maurer, Thomas Steinecke

manfred.maurer@siemens.com

thomas.steinecke@infineon.com

#### Contents

- Motivation

- Design Chain

- Model Hierarchy

- Model Integration

- IBIS Viewpoint

- Conclusion

#### Motivation

■ Signal Integrity ✓

■ Power Integrity + EMI!

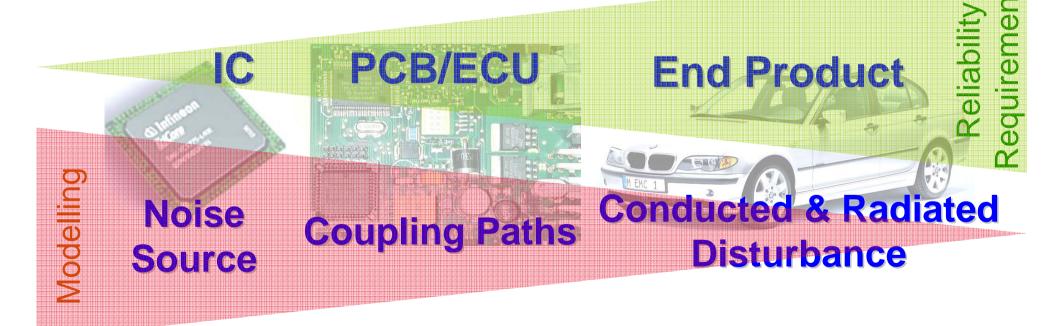

## Design Chain

- Goal = High reliability of end customer products

- Process = Reliability requirements for all components (top-down)

Standardized EMI Models along design hierarchy (bottom-up)

Use common model format (SPICE, VHDL-AMS)

# Model Hierarchy (1)

- Level "IC" (Chip Floorplan + IC Package):

- Minimize EMI by on-chip design measures and block place+route

- Minimize EMI by in-package design measures and substrate routing

- Level "ECU" (IC Placement + Power/Signal Routing):

- Minimize EMI by ECU on-board design measures and IC place+route

- Level "Car" (ECU+Antenna Placement + Harness Routing):

- Minimize EMI by in-car design measures and improved control unit position & harness interconnects

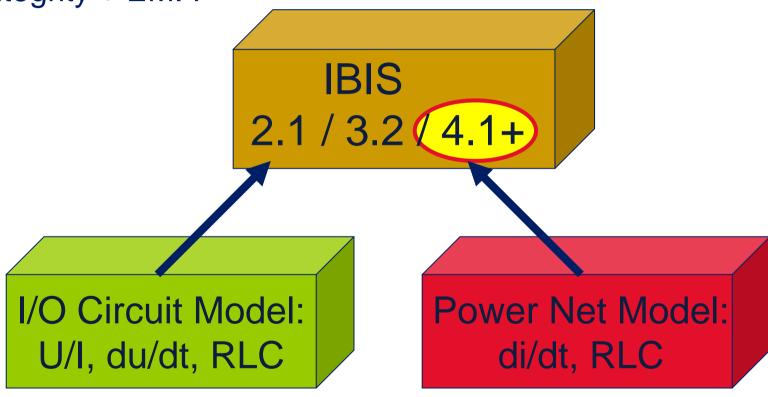

## Model Hierarchy (2)

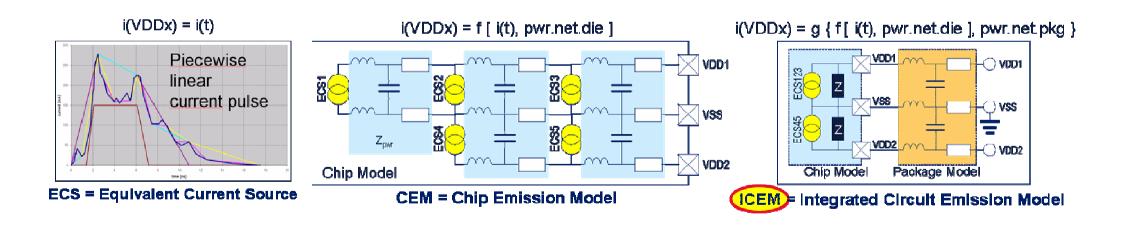

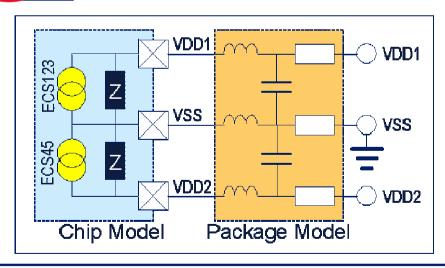

#### Level "IC" (Chip Floorplan + IC Package):

- ECS = Equivalent current source, describes i(t) of every IC function block

- CEM = All ECS of a chip, connected by RLC of on-chip power networks

- ICEM = Chip (CEM) as "black box" + RLC of IC package

## Model Hierarchy (3)

■ Level "IC Placement" + "Power/Signal Routing":

IBIS = I/O buffer description for IC

ICEM = Power supply noise + network description for IC

IBIS 4.1+

#### Model Integration

- ICEM can be integrated into IBIS in two ways:

- as i(t) table

- as executable SPICE model

- i(t) table requires IBIS standard extension

- Executable SPICE is supported by IBIS 4.1+

- Proposals by

Bob Ross (2003),

Syed Huq et al (2004)

```

Some additions to the IBIS model:

[Circuit Call] ICEM

| mapping port

node

Port map

Code connecting vdd_ic to pin 12 and vss_ic to

pin 14,

************

[External Circuit] ICEM

Language SPICE

Corner

corner name

file name

circuit name (.subokt name)

Corner

Typ

icem d60.spi icem typ

| Ports are in same order as defined in SPICE

vdd ic vss ic

[End External Circuit]

Separate SPICE file icem d60.spi

************

.SUBCKT icem_typ vdd_ic vss_ic

RVDD Vdd_ic Vdd_n1 2

LVDD Vdd_n1 Vdd_n2 2.2n

Cd Vdd_ic Vss_ic 3.2n

Cb Vdd_n2 Vss_n2 50p

RVSS Vss ic Vss n1 2

LVSS Vss_n1 Vss_n2 2.2n

Ib Vdd_a2 Vss_a2 PULSE(0.01 0.4 10as 1.0as 1.0as 0.0las 31.25as)

.ENDS Icem typ

```

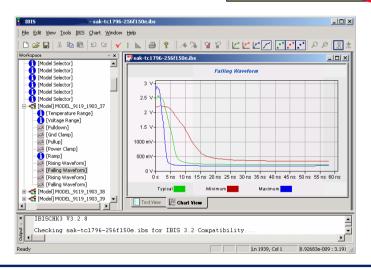

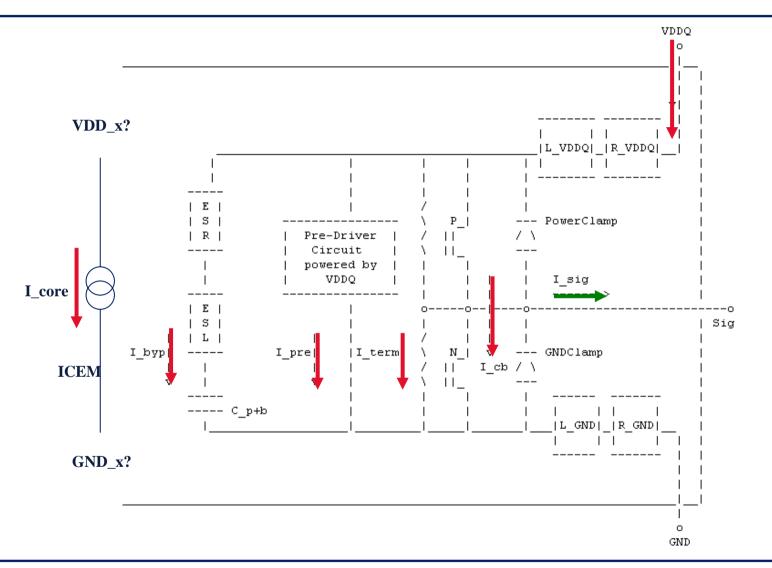

### IBIS viewpoint of ICEM Models

- Why ICEM Model from IBIS viewpoint

- EMI simulation

- SI simulation under more realistic Vdd/GND connections

- Model Structure

- Model placement

- What is required in practice?

- the ICEM model

- BIRD95.1(2)

- Conclusions

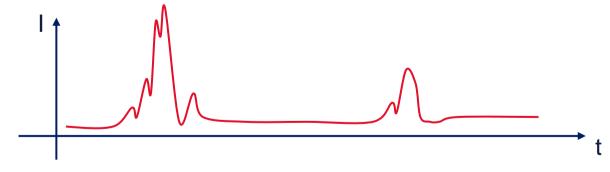

#### **ICEM Model Structure**

- 2 x Current generator

- different behavior at rising / falling CK-edge

- different amplitude

- different pulse width

- PWL current shape (1. approx. triangle)

- coupled by variable timing relation → frequency

- RLC package / bonding / die

- conform to the IBIS specification

- BIRD95.1 describes the placement of the ICEM model

- [External Circuit] ICEM\_xx

- [Circuit Call] ICEM\_xx

#### ICEM Model Example

#### ■ SPICE subcircuit

```

.SUBCKT ICEM1_typ

vdd_ic vss_ic t_dl_12

R vdd

vdd ic

vdd n1

L vdd

vdd n1

vdd n2

2.2n

C_d

vdd ic

vss_ic

3.2n

C b

vdd n2

50p

vss_n2

R_vss

vss_ic

vss_n1

2

vss n2

2.2n

L vss

vss n1

I b1

vdd n2

vss_n2

PULSE (0.01 0.4 10ns

1.0ns 1.0ns 0.03ns 31.25ns)

PULSE (0.01 0.3 ,10ns+t_dl_12' 1.0ns 1.0ns 0.01ns 31.25ns)

l b2

vdd n2

vss n2

.ENDS ICEM1_typ

```

#### ■ PWL table

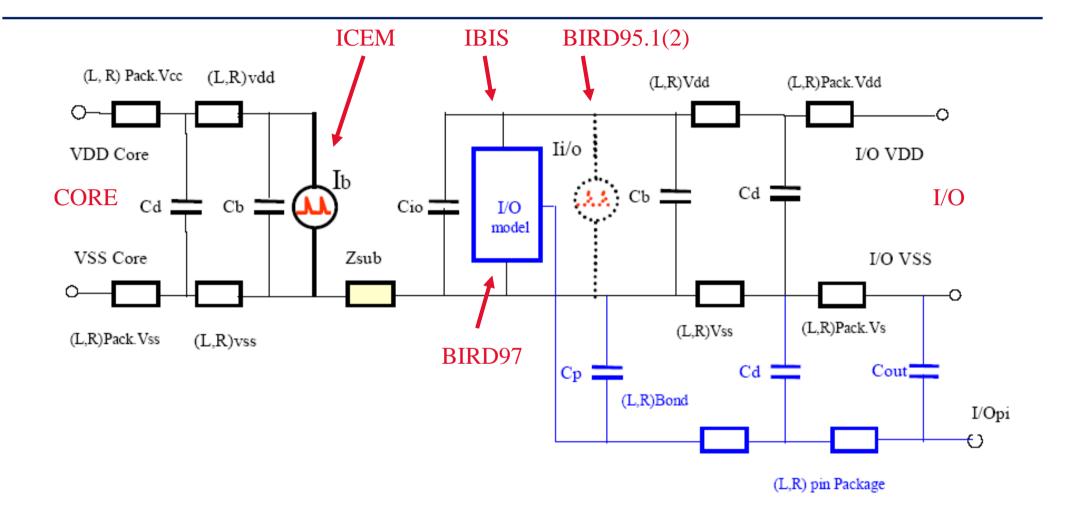

# BIRD 95.1(2)

#### **Model Placement**

## **Summary and Conclusion**

- ICEM models in the actual format are suitable to IBIS 4.1+

- no model modification needed

- mathematical function or PWL format

- parameter for ICEM model tuning are possible, but not desired

- RLC for package + bonding + die only in the IBIS-file

- to avoid double counting

- better accuracy required

- Power/GND-Pin assignment for I/O and CORE

- [Pin Mapping]

- BIRD 95.1(2)

- →→→ SI and EMI simulation

more accurate by considering the I(t) and Vdd/GND connections