# **Quality of IBIS Models IBIS for LVDS**

**Christian Sporrer Infineon Technologies AG**

## **LVDS Definition**

**IBIS for LVDS**

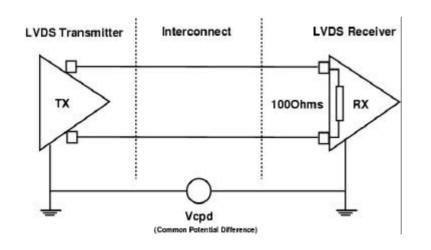

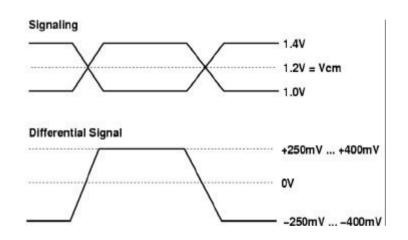

# LVDS Low Voltage Differential Signaling Point to Point 500 MBit/sec

Standard TIA/EIA-644 IEEE Std 1596.3

# **Modeling Methodology**

**IBIS** for LVDS

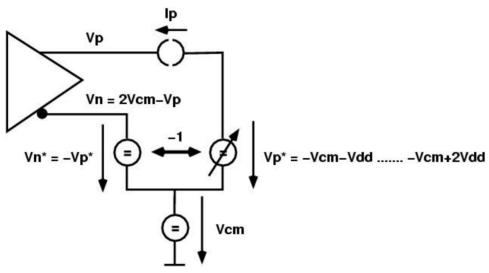

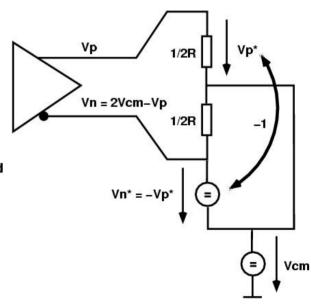

Problem: In IBIS for each differential output pin a own buffer model is necessary, but this models are not independent!!

#### VI - Characteristics

#### **Vt - Waveforms**

Introduced by Proven by

A. Tambone

H. Hegazy, et. al.

D. J. Burns, et. al.

(Semiconductor Business News 2000)

(IBIS Summit Date 2001)

(IBIS Summit DAC 2002)

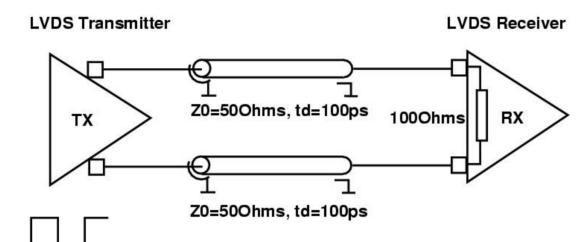

Testsystem

IBIS for LVDS

**Testcases:**

700MHz, CMOS

625MHz, Bipolar

#### **SPICE** Referenz:

TITAN (Infineon) for 700MHz, CMOS using layout extracted netlist.

SPECTRE (Cadence) for 625MHz, Bipolar using schematic netlist.

**IBIS Simulation:**

**HSPICE (Avant!)**

Interconnectix, ICX IS (Mentor)

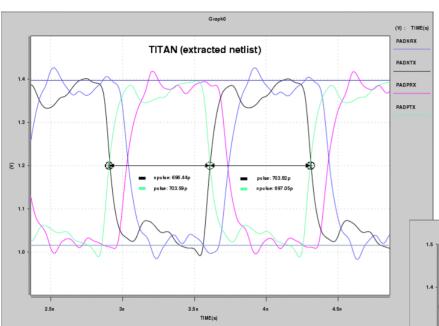

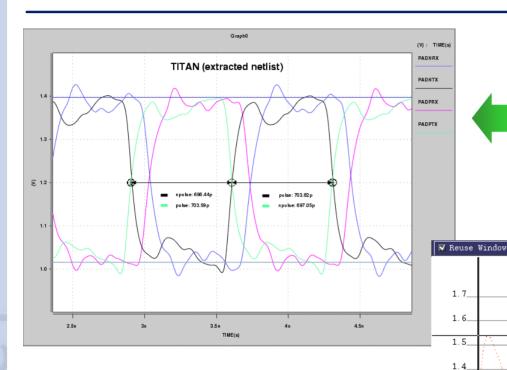

# Results 700MHz, CMOS

#### **IBIS for LVDS**

SPICE (TITAN)

Transmitter Output & Receiver Input

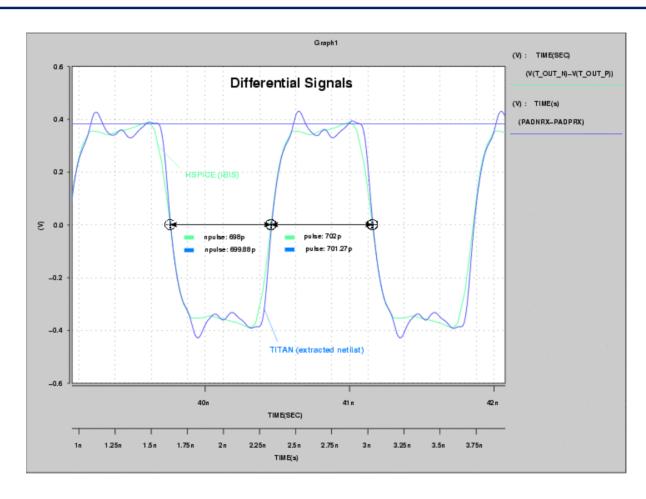

# Results 700MHz, CMOS

**IBIS for LVDS**

Differential Signal at Receiver Input SPICE (TITAN) & IBIS (HSPICE)

# Results 700MHz, CMOS

#### **IBIS for LVDS**

ICX STUB DESIGN U0-2 (die)

ICX STUB DESIGN U2-2 (die)

ICX STUB DESIGN

SPICE (TITAN)

Transmitter Output & Receiver Input

ICX\_STUB\_DESIGN/U0-1./pinInst: 11.500 ns 1.536 V

1.3 Vinh VMead 2 Vinh 1.1

11.0

Time [ns]

12.0

10.0

IBIS (Interconnectix, ICX IS)

Transmitter Output & Receiver Input

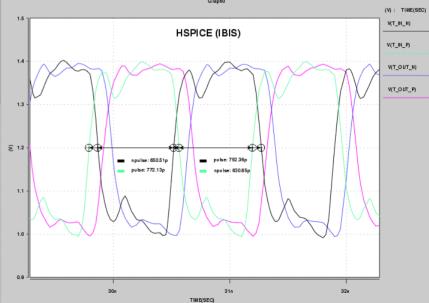

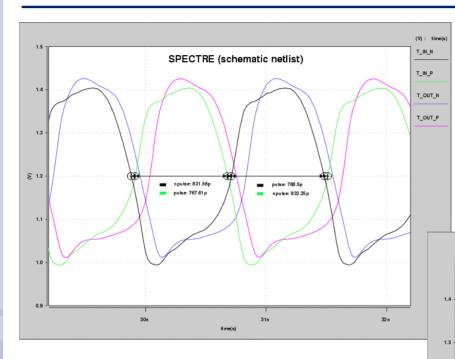

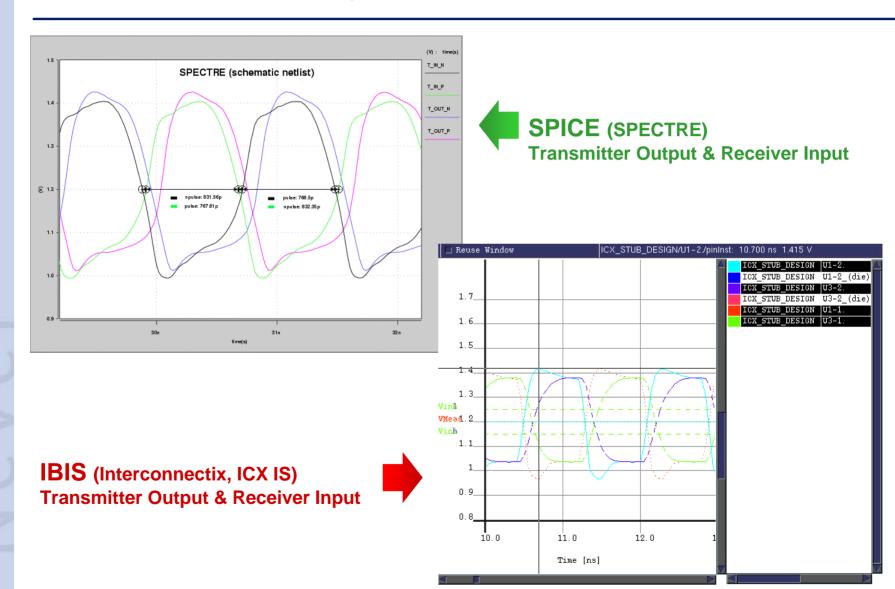

# Results 625MHz, Bipolar

**IBIS for LVDS**

V(T\_OUT\_P)

SPICE (SPECTRE)

Transmitter Output & Receiver Input

HSPICE (IBIS)

TIME(SEC)

pulse: 860.22 p

1.1

IBIS (HSPICE)

Transmitter Output & Receiver Input

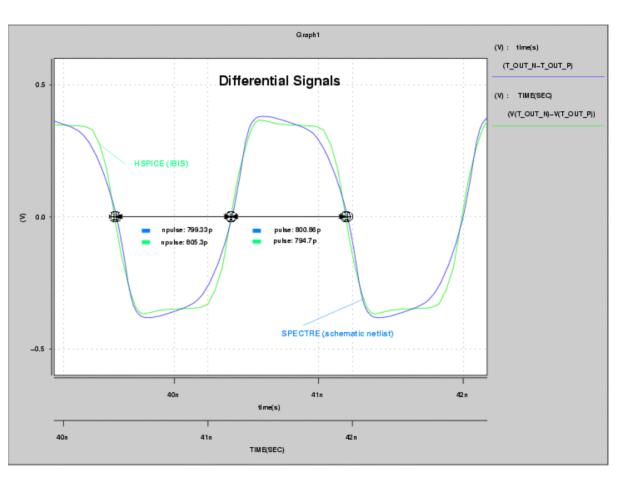

Differential Signal at Receiver Input SPICE (SPECTRE) & IBIS (HSPICE)

# Results 625MHz, Bipolar

#### **IBIS for LVDS**

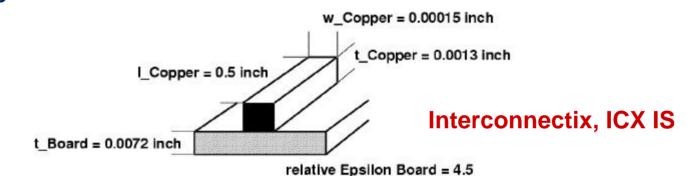

# **Transmission Line Modeling**

**IBIS** for LVDS

#### Microstrip Approach proposed by Brain C. Wadell

**Transmission Line Design Handbook**

Artech House Norwood MA, 1991 pp 94 .. 95

Z0=50Ohms, td=100ps

TITAN, SPECTRE, HSPICE

# **Results Summary**

**IBIS** for LVDS

Differences in pulsewidth symmetry and dc-shift of waveform crossings

**HSPICE:** Tendency to shorten the low level pulse.

ICX IS:

Interchange of signal behaviour at transmitter output and receiver input compared to SPICE.

**Option > Remove Initial Delay from V-t-curves <**

must be turned on!

**Overclocking**

**HSPICE:** t\_rise + t\_fall < 2T\_Signal

(e.g. T\_Signal = 1.6ns for 625MHz, Bipolar testcase)

ICX IS: not verified!

Without assistance of tool vendors improvement of IBIS model quality is very difficult !!

#### **Model Vendors Dilemma**

**IBIS** for LVDS

The different simulation results are all similar, but the differences are large enough, that a potential modeling weakness cannot be excluded.

What is wrong: the IBIS modeling or the IBIS simulations?

The Golden Parser only supports syntax checking and plausibility checks (e.g. vi-characteristics, vt-waveforms compliance check), but no verification of the electrical behaviour.

How to assure the quality of IBIS models?

## **Possible Solutions**

**IBIS** for LVDS

#### What can be done?

Ignore the problem

**Golden Simulator**

Focus on key customer

**Qualification service for IBIS models**

Free access to IBIS tool sweet

Cooperation with dedicated tool vendor