#### **Automated AMI Model Generation & Validation**

DAC IBIS-Summit Anaheim, CA June 15<sup>th</sup>, 2010

José Luis Pino Amolak Badesha

Manuel Luschas Antonis Orphanou Halil Civit

**Agilent Technologies**

# Agenda

- AMI Model Generation Barriers

- Automated AMI Model-generation flow

Example-1: 6.25 Gb/s

Example-2: 10.3125 Gb/s

• TX Model Correlation Study

-with Transistor Simulations

-with Measurements

Benefits of Automated AMI flow

## **#1 AMI modeling barrier** *Model Generation Time*

AMI Modeling suppose to Speed-up System Design Cycle, BUT, Model-generation takes Significant Time & Resources

....System Vendors have to wait a LONG time before accurate AMI models become available

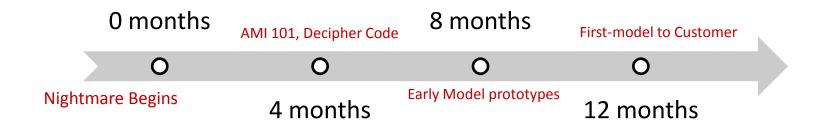

Note: Vendors with NO experience in AMI modeling are spending <u>6-12+ months</u> to come up with first-generation models

Models come very late in Design Cycle  $\rightarrow$  used only for Validation, NOT Design

## Why AMI-model generation takes so long?

Typical Signal Integrity Engineers are NOT programmers

....they are having "Nightmares" in trying to develop AMI models

- Cryptic Matlab/C++ code passed from System-Architectures  $\rightarrow$  AMI Modeler (if lucky)

- Challenge to Convert Algorithm design Code  $\rightarrow$  AMI format

## **Typical AMI model generation flow...**

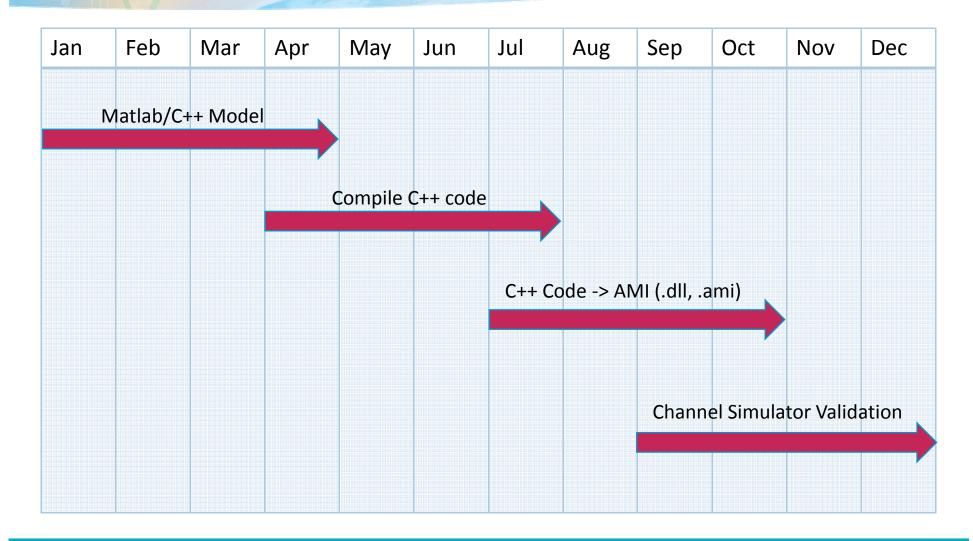

## **Automated AMI model generation flow...**

| Jan                                                                                                 | Feb                                              | Mar     | Apr                                                   | May        | Jun | Jul | Aug | Sep | Oct | Nov | Dec |

|-----------------------------------------------------------------------------------------------------|--------------------------------------------------|---------|-------------------------------------------------------|------------|-----|-----|-----|-----|-----|-----|-----|

| Matlab/(<br>Library of C<br>Building Blo<br>-FIR/IIR<br>-FFE/DFE<br>-CDR<br>-S-block<br>-Peaking, V | C++ Mod<br>Common<br>Cocks C<br>GA etc. C-<br>Au |         | ++ code<br><u>n</u><br>> AMI (.c<br><u>Generation</u> | dll, .ami) |     |     | Aug | Seb |     |     | Dec |

| Autom                                                                                               | ated AM                                          | II Flow |                                                       |            |     |     |     |     |     |     |     |

### **ESL flow for Automated AMI Modeling**

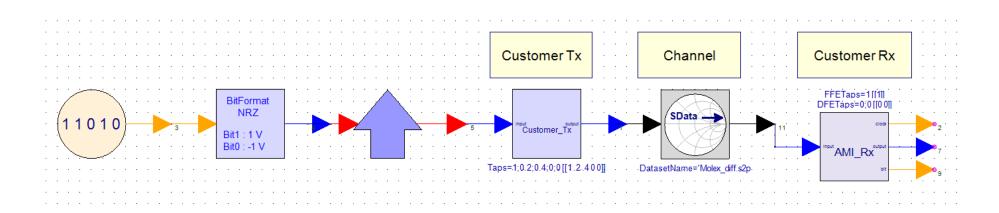

Here is an Example of SerDes modeling using ESL flow-

**Electronic System Level (ESL)** design and verification is an emerging electronic design methodology that focuses on the *higher abstraction* level concerns first and foremost.

ESL flow facilitates utilization of appropriate abstractions in order to <u>increase</u> <u>comprehension about a system</u>, and to enhance the probability of a successful implementation of functionality in a <u>cost-effective</u> manner

## **ESL flow: TX Modeling Example (1)**

#### **Step-1:** Starting Architecture Design with Generic Model

Different blocks represent high-level TX architecture

#### **Challenges:**

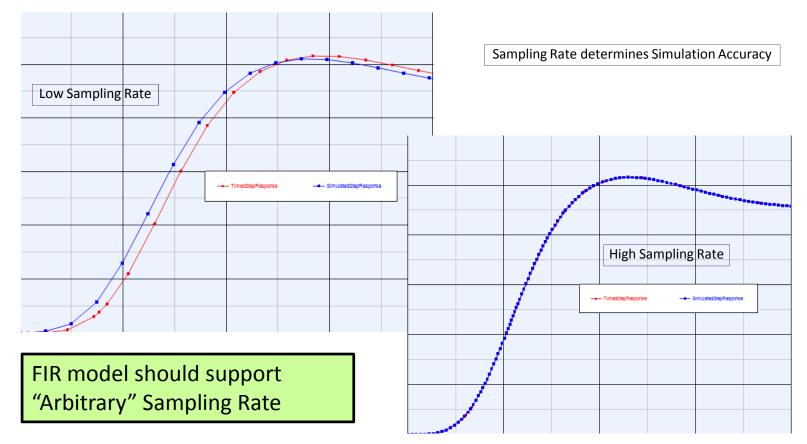

1. Typical Simulation and Measured Data is not equally time-stepped

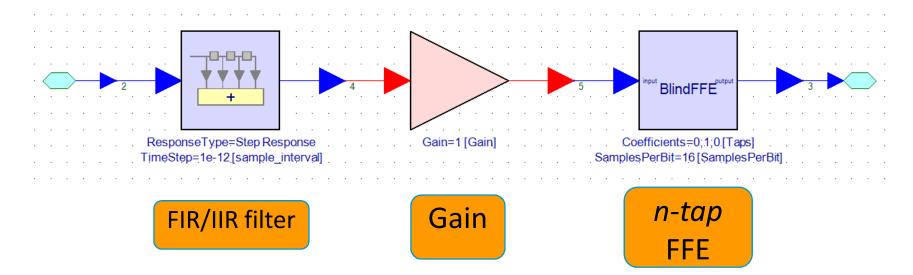

## ESL flow: TX Modeling Example (2)

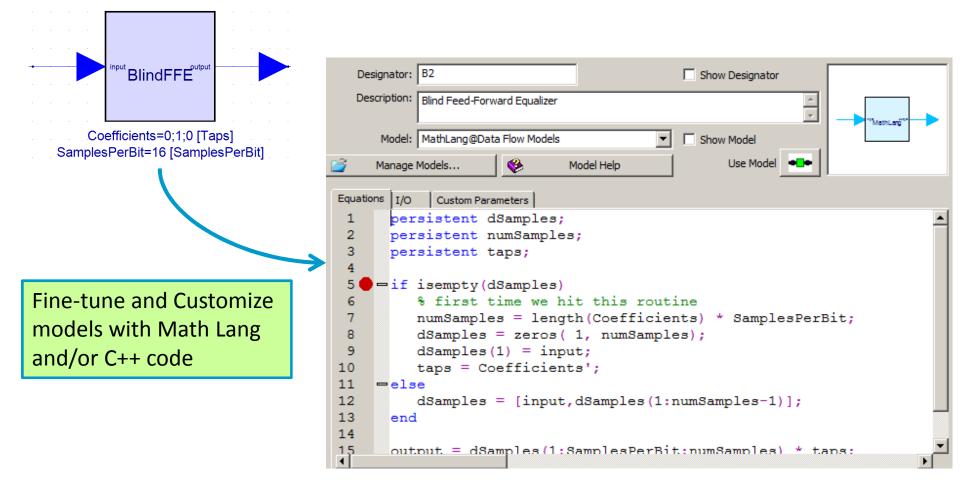

#### **Step-2:** Customize IP -> Bring in Math Lang or C++ Code

## ESL flow: TX Modeling Example (3)

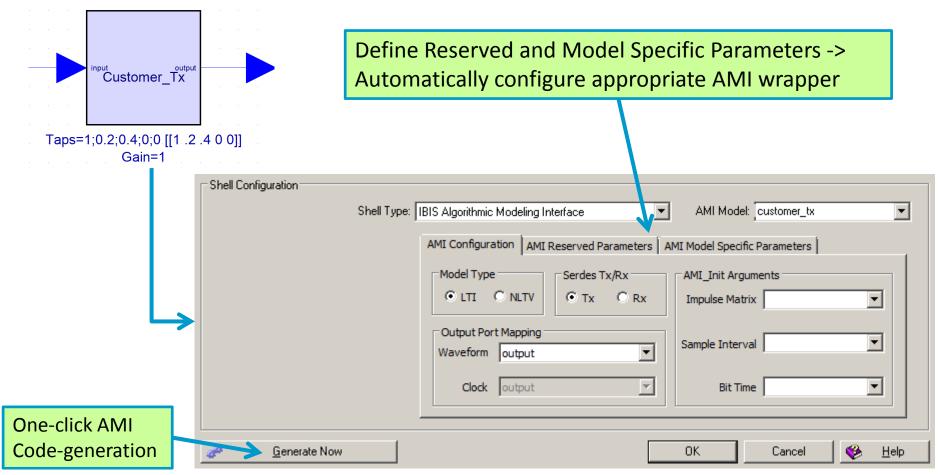

#### Step-3: One-click AMI Code-Generation

## **ESL flow: TX Modeling Example (4)**

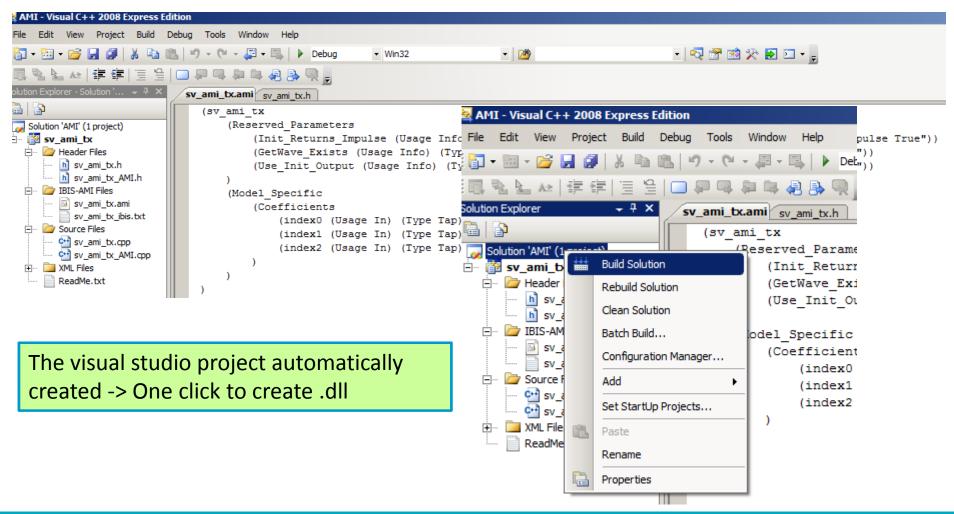

#### **<u>Step-4</u>**: Automatically Generated .ami and Visual-Studio project

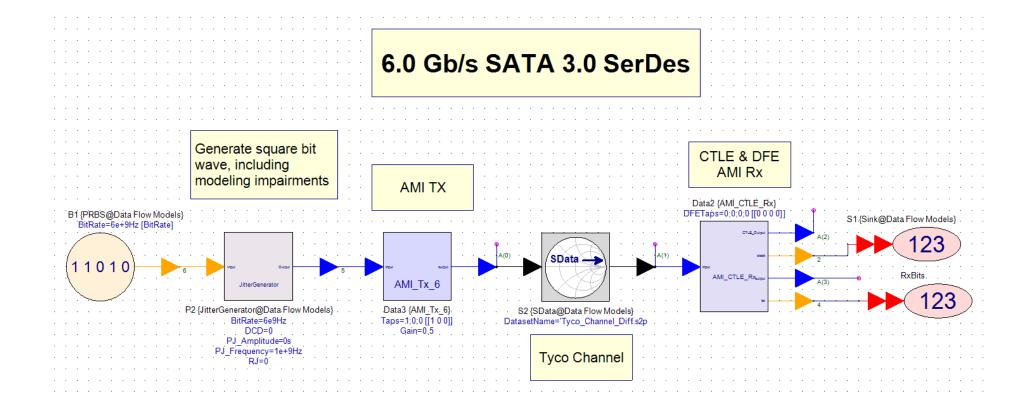

### Example #1 6.0 Gb/s (SATA 3.0)

## TX Modeling 6.0 Gb/s (SATA 3.0)

#### **TX** Architecture

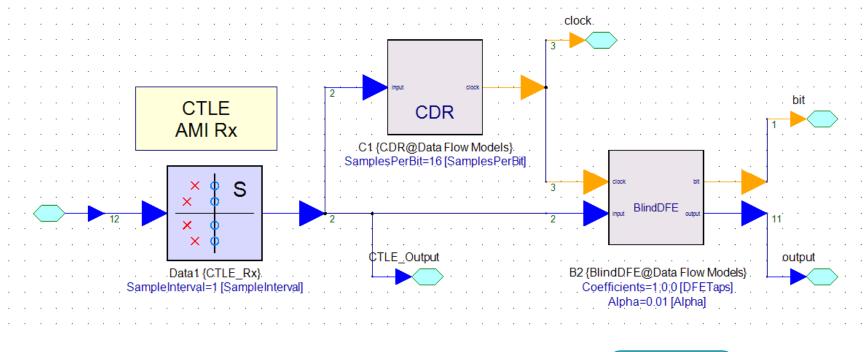

## RX Modeling 6.0 Gb/s (SATA 3.0)

#### **RX** Architecture

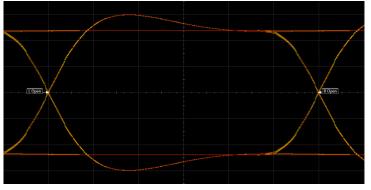

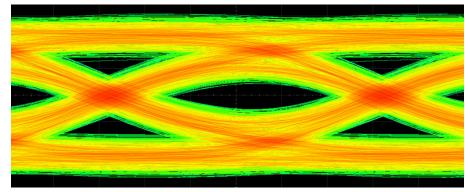

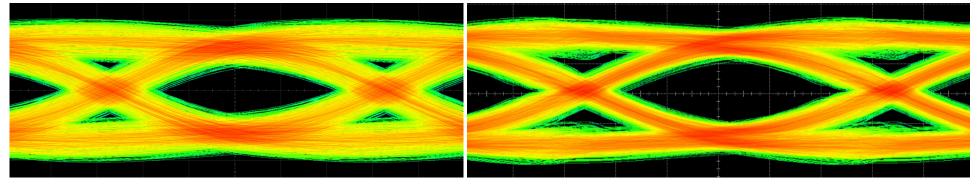

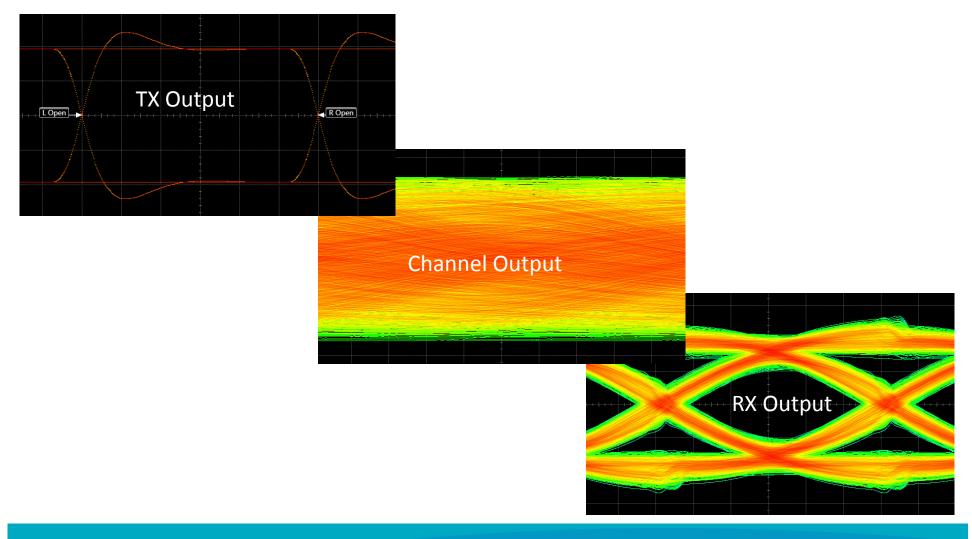

## Results 6.0 Gb/s (SATA 3.0)

#### After CTLE EQ

#### After Channel

#### After CTLE+DFE EQ

\*Note: EQ taps not optimized for maximum eye

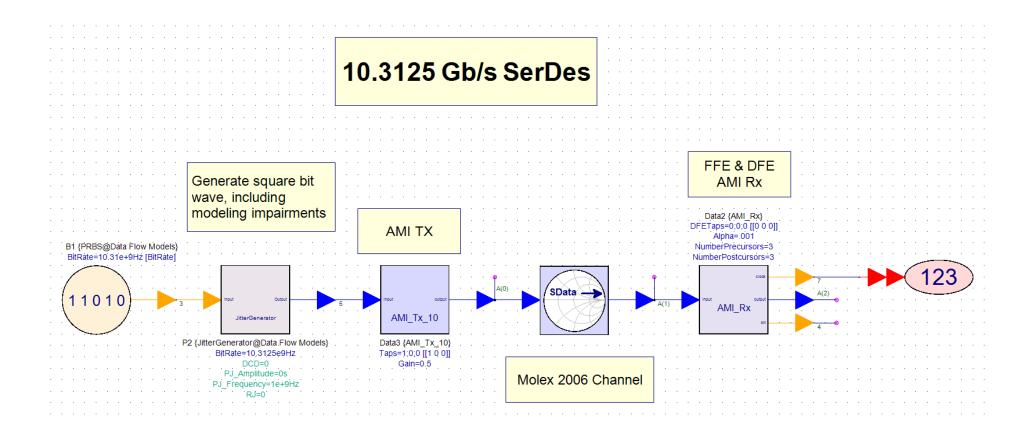

#### Example #2 10.3125 Gb/s (10-GB Ethernet)

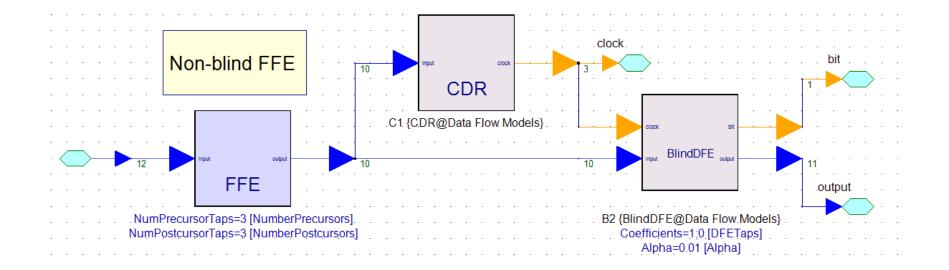

### RX Modeling 10.3125 Gb/s (10-GB Ethernet)

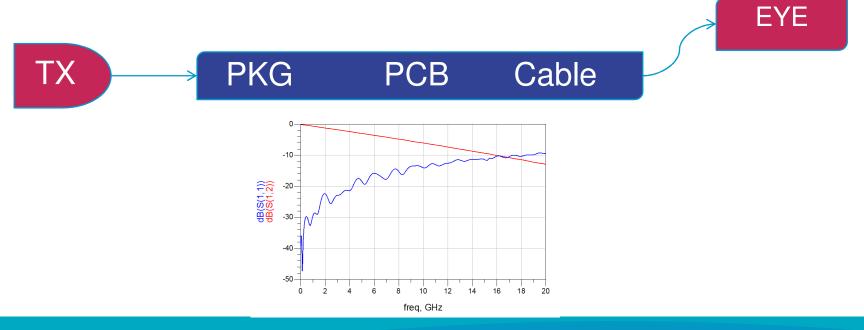

## Example #2 10.3125 Gb/s (10-GB Ethernet)

# TX 10.3125 Gb/s AMI model correlation study

#### Strategy

- 1. Correlate Transistor Simulation vs. AMI model

- 2. Correlate Measured vs. AMI model

#### Steps-

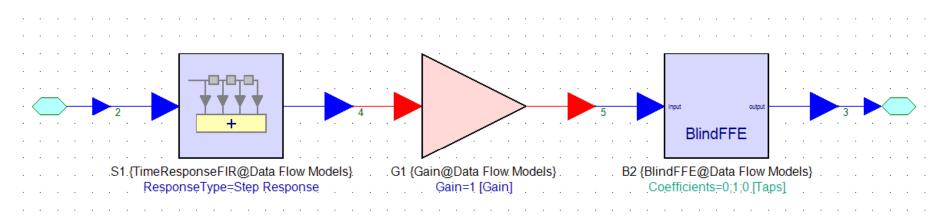

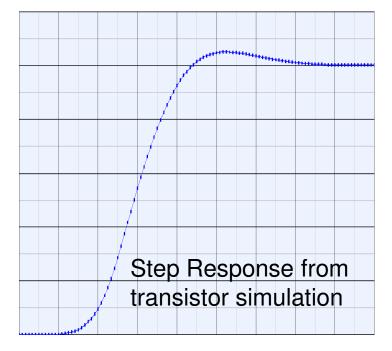

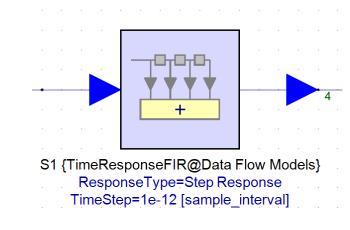

- 1. Generate Step Response from transistor simulation

- 2. Generate AMI model using Agilent SystemVue

- 3. Compare

FIR filter with Step Response Input

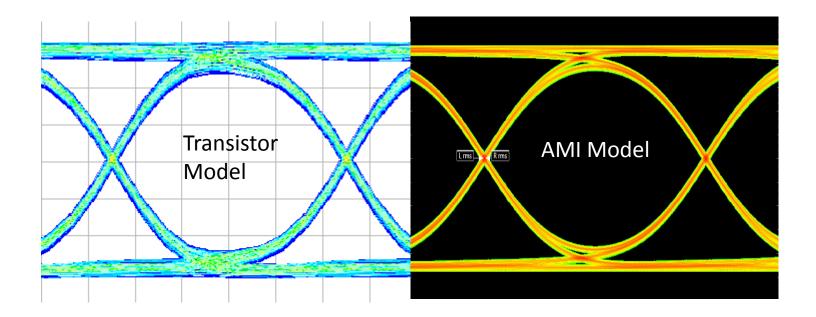

## **Correlation** *transistor model vs. AMI model*

Excellent match between transistor simulation and AMI model

Good faith in model-generation methodology!

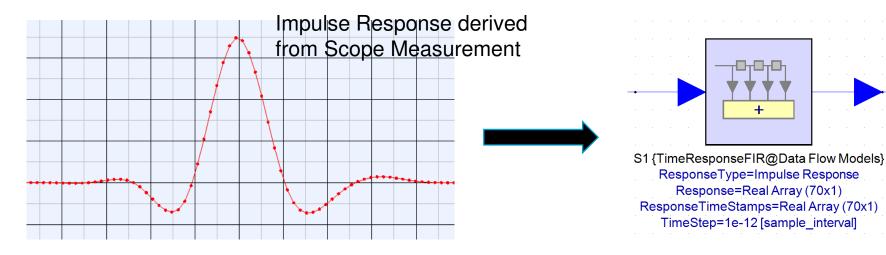

#### Steps-

- 1. Measure waveform

- 2. De-embed Channel

- 3. Output Impulse response

FIR filter with Impulse **Response Input**

+

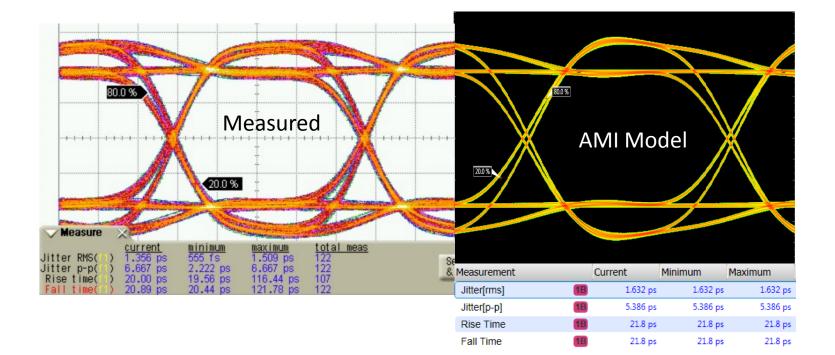

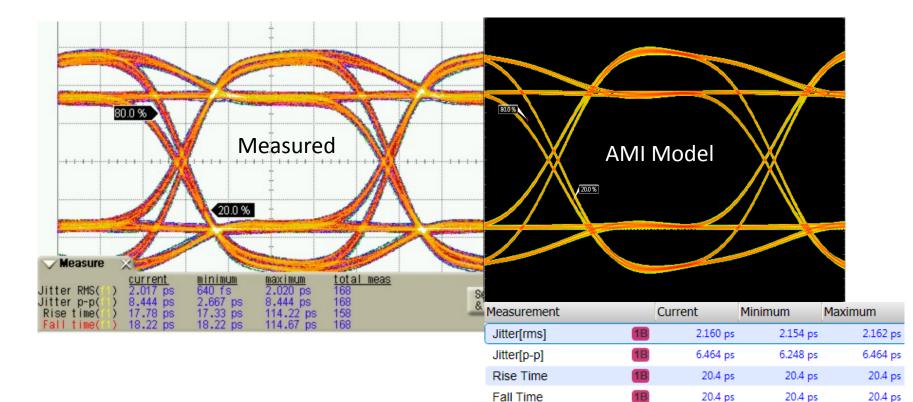

# **TX Correlation Measured** *emphasis #1: tap 0, 1, -0.2*

# TX Correlation Measured emphasis #2: tap 0, 1, -0.25

# **Benefits of ESL Design Flow**

Automated AMI-Model Generation

- 1. Complete "Automation" of Code-generation and Model Compilation *a task that routinely takes months because of its complexity*

- 2. Basic building blocks that can used to start model development *FIR/IIR filters, FFE, DFE, CDR etc.*

- Easily customize models to include custom IP

Custom C++ and Math-Lang