## Issues with Interfacing "2N" and "N+ref" Behavioral Models

Sam Chitwood Sigrity, Inc.

DAC IBIS Summit June 5, 2007

## Outline

- Review of typical S-parameter connections and "N+ref" implementation in SPICE

- Comparison of "2N" and "N+ref" modeling techniques

- "2N" Connection Techniques in Simulation

- Comparison of the Resulting Models

- Summary and Conclusions

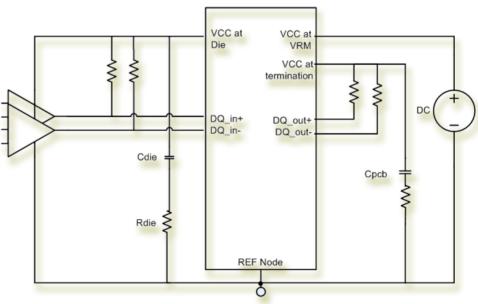

### S-parameters and the REF Node: Port Connections and SPICE Usage

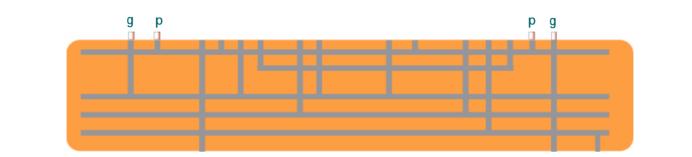

## **Typical PDS Port Connections**

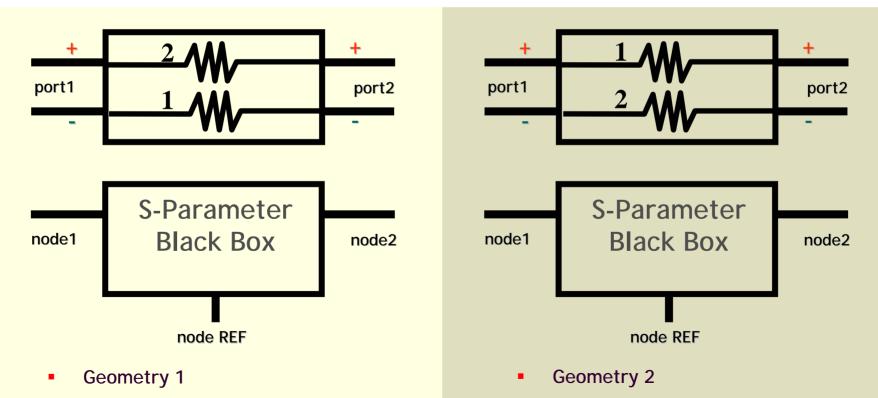

## S-parameters are a "loop" concept

- For the two geometries below, the resulting S-parameters are identical.

- Properties of individual nets *cannot* be derived from S-parameters.

- This is one of the reasons why explicit negative terminals are not provided by many simulation tools. (REF is a very useful technique – more details later).

### **SIGRITY**

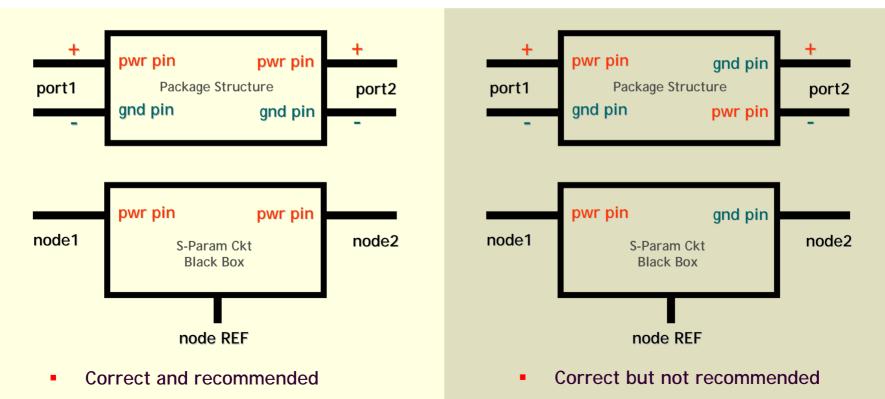

# **Typical Port Connection Guidelines**

- Use the same net (ex. VSS) as the "-" reference terminals for all ports.

- Mixed referencing (using different nets for "-" port terminals) is allowed, but not recommended. (NOT allowed if you hookup circuits across the ports.)

- These guidelines are intended for external circuits with 1 PWR & 1 GND.

# Questions on the Single Reference Node (REF) in Many SPICE Implementations

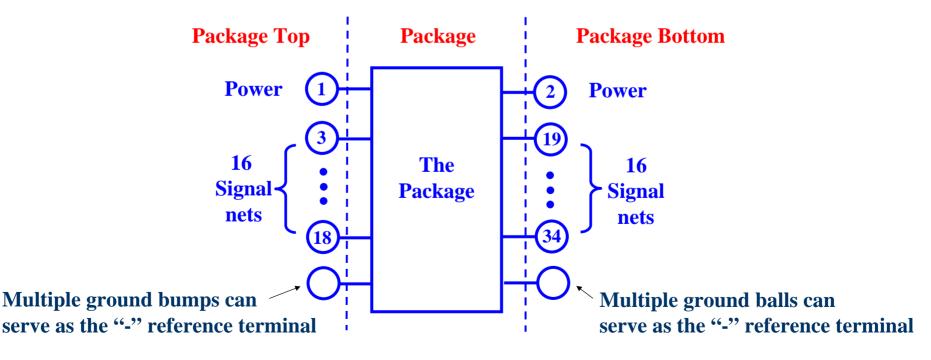

- The physical structure has N ports. Each port has one "+" terminal and one "-" local reference terminal, resulting in a total of 2N physical terminals.

- The SPICE circuit model has N+1 nodes. The N nodes correspond to the N physical "+" terminals, whereas the +1 node is a virtual reference node commonly named "REF".

- The "REF" node is not a physical ground node, nor a power node. Rather, the circuit is created such that the response or behavior at each + node with respect to the REF node models the response or behavior of each of the original "+" port nodes with respect to their individual "-" port nodes. REF is a *mathematical construct*.

# Circuit Connection Guidelines

- When using the REF node with a specific "+" terminal, think of the REF node as that port's corresponding "-" terminal.

- If you do not already have node 0 in your circuit, you should connect REF to node 0 since SPICE requires as least one node 0. This also makes voltage measurement easy!

- If you unfortunately already have node 0 somewhere in the driver or receiver circuits, do

not make the additional connection of REF to node 0. Measure voltage as V(n)-V(ref).

- If the Driver and Receiver models both contain global node names for their negative terminals (ex: ground, gnd, 0), the REF technique accurately models the PDS because those negative terminals are meant to be connected in this technique.

- If the models are encrypted, unfortunately the user does not know if global names are used or not... REF must be used.

## "2N" Behavioral Models

- Some extraction tools may provide "2N" behavioral models (note the 2 ohm resistor). They intend to reproduce the distributed response between all physical terminals.

- These models have unique terminals for multiple power and ground pins.

- Unfortunately, these models cannot be interfaced with (or connected to) typical S-parameters due to the REF technique in many SPICE tools.

- Warning: Global node "0" is used in this model. If node "0" exists elsewhere in the SPICE deck, incorrect results are likely.

| .subckt PowerN | Iodel n1 n2 n3 n4 n5 n6 n7 n8      |

|----------------|------------------------------------|

| Vd1 n1         | n1_p 0                             |

| Rp1 n1_j       | o n8 2.000000                      |

| Gd1_1 n8       | n1_p n1 n8 -3.7036112142644201e-01 |

| Fd1_1 n8       | n1_p Vd1 -7.4072224285288413e-01   |

| Gd1_2 n8       | n1_p n2 n8 1.8288902037848827e-02  |

| Fd1_2 n8       | n1_p Vd2 3.6577804075697662e-02    |

| •••            | -                                  |

| Vd2 n2         | n2_p 0                             |

| Rp2 n2_j       | n8 2.000000                        |

| Gd2_1 n8       | n2_p n1 n8 1.0051775904867706e-01  |

| Fd2_1 n8       | n2_p Vd1 2.0103551809735415e-01    |

| Gd2_2 n8       | n2_p n2 n8 -4.4313952195018808e-01 |

| Fd2_2 n8       | n2_p Vd2 -8.8627904390037626e-01   |

| Gd2_3 n8       | n2_p n3 n8 4.5860899569942673e-02  |

| •••            |                                    |

| Rlarge_n1 nn1  | 0 1.0e6                            |

| Cn1 nn1        | 0 1.0                              |

| Gb1_1 0 n      | n1 n1 n8 0.707107                  |

| Fb1_1 0 n      | n1 Vd1 1.4142135623730951e+00      |

| Ga1_1 0 n      | n1 nn1 0 -2.8955106355430019e+08   |

| ••••           |                                    |

9

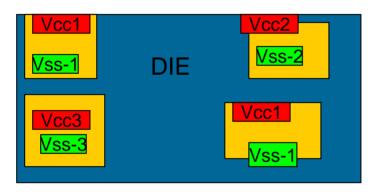

# Typical S-parameter connectivity is not compatible with other "2N" models

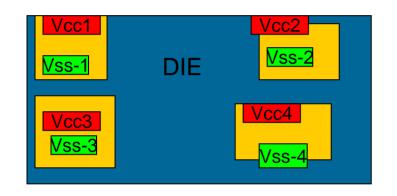

#### **2N Die Model**

.subcircuit vcc1 vss1 vcc2 vss2 vcc3 vss3 vcc4 vss4 die

N+ref Model (with conventional port connections) .subcircuit pwr1 pwr2 pwr3 pwr4 REF pkg\_brd

#### There is a mapping problem!

The multiple "vss" nodes in the 2N model cannot be shorted together at the REF node.

### S-parameter Connection Techniques to Generate 2N External Terminals

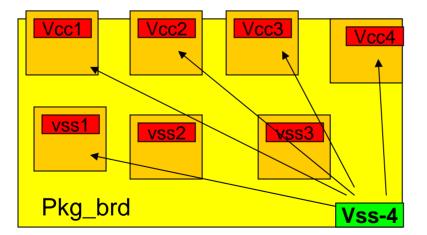

## Alternative Port Connection Technique #1

Instead of the conventional 4 port technique, select one vss bump and let it serve as the negative port terminal for all other ports.

| Port1 vcc1-vss4 | Port2 vcc2-vss4 |

|-----------------|-----------------|

| Port3 vcc3-vss4 | Port4 vcc4-vss4 |

| Port5 vss1-vss4 | Port6 vss2-vss4 |

| Port7 vss3-vss4 |                 |

#### 2N Die Model

.subcircuit vcc1 vss1 vcc2 vss2 vcc3 vss3 vcc4 vss4 die

**S-parameters** (with alternative port connection technique) .subcircuit pwr1 pwr2 pwr3 pwr4 gnd1 gnd2 gnd3 REF pkg\_brd

#### **Node Mapping**

vcc1->pwr1, vcc2->pwr2, vcc3-> pwr3, vcc4->pwr4, vss1->gnd1, vss2->gnd2, vss3->gnd3, **vss4->REF**

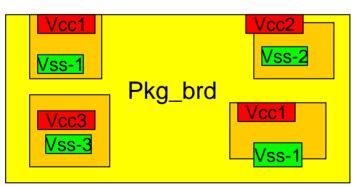

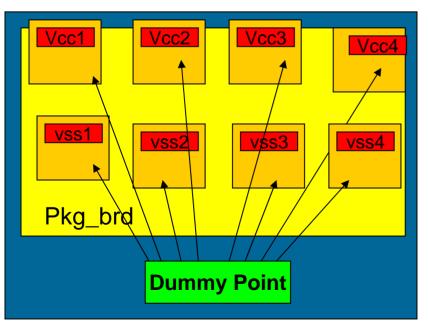

## Alternative Port Connection Technique #2

Instead of the conventional 4 port technique, some tools allow a "dummy reference point". It serves as the negative port terminal for all other ports.

| Port1 vcc1 – d.p. | Port2 vcc2 – d.p. |

|-------------------|-------------------|

| Port3 vcc3 – d.p. | Port4 vcc4 – d.p. |

| Port5 vss1 – d.p. | Port6 vss2 – d.p. |

| Port7 vss3 – d.p. | Port8 vss4 – d.p. |

#### 2N Die Model

.subcircuit vcc1 vss1 vcc2 vss2 vcc3 vss3 vcc4 vss4 die

**S-parameters** (with alternative port connection technique) .subcircuit pwr1 pwr2 pwr3 pwr4 gnd1 gnd2 gnd3 gnd4 REF pkg\_brd

#### **Node Mapping**

vcc1->pwr1, vcc2->pwr2, vcc3-> pwr3, vcc4->pwr4, vss1->gnd1, vss2->gnd2, vss3->gnd3, vss4->gnd4

REF is not connected to the 2N Die model (it floats) structions

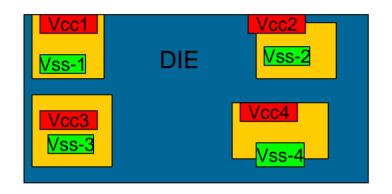

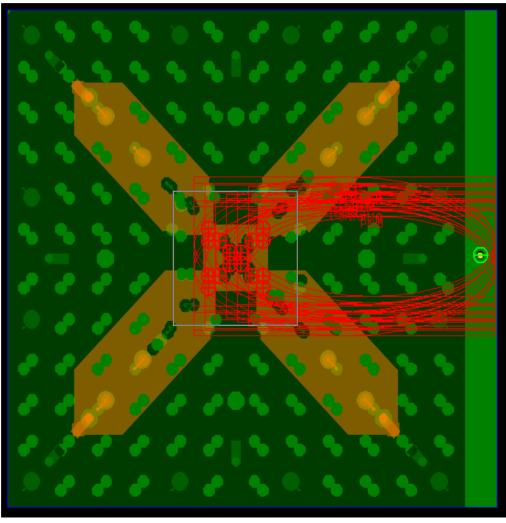

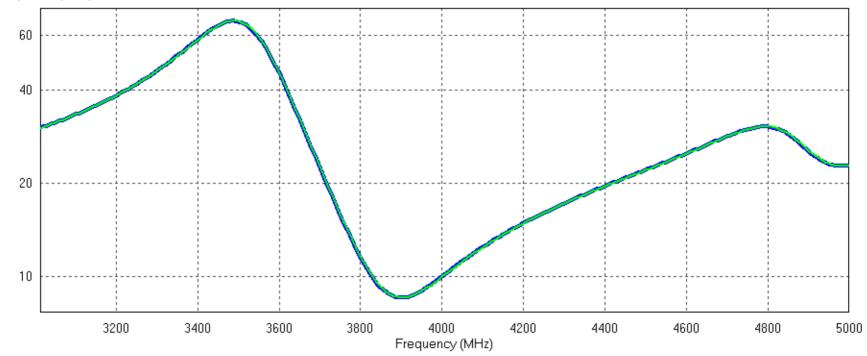

## Graphical Representation of Alternative Technique #2

Sigrity Inc. Proprietary – Use Pursuant to Company Instructions

**Technique #1 – Red Technique #2 – Blue**

- The "loop inductance" test is the impedance at the die with all BGA balls shorted.

- The same results can be achieved with either connection technique.

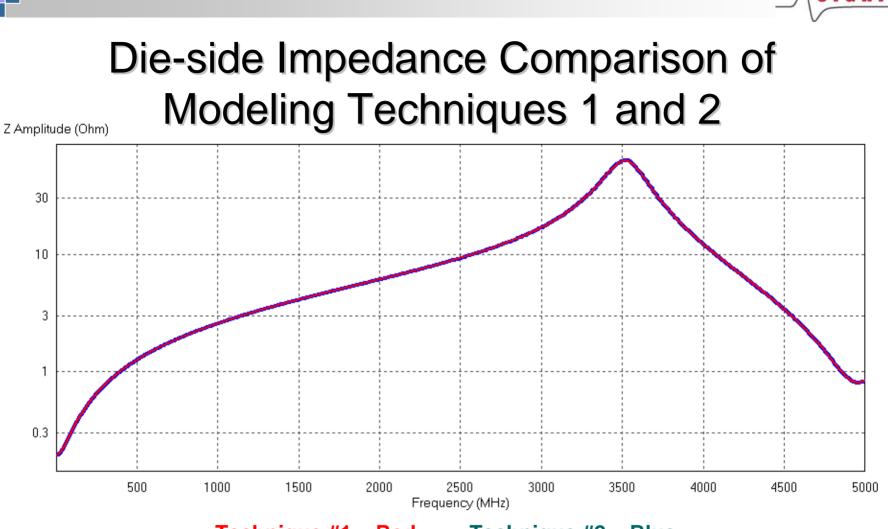

## Comparison of Results for Z(vcc1, vss1)

Z Amplitude (Ohm)

#### Technique #1 – Green Technique #2 – Blue

- Z(vcc1, vss1) is the impedance at the top-left of the die. All BGA balls were shorted.

- Again, the same results can be achieved with either technique.

# **Summary and Conclusions**

- Typical "N+ref" S-parameters do not provide unique reference terminals in SPICE. This is *extremely useful* due to encrypted models and global "gnd" node names.

- The choice between "2N" and "N+ref" modeling techniques should be determined by the connectivity of the intended external circuits

- If distributed reference terminals are desired, two connection techniques were presented that yield S-parameters with explicit connections at all pins

- The "2N" simulation methodologies were shown to produce correlated results

SIGRITY