# An algorithm to model overclocking more accurately

IBIS Summit at DesignConEast 2003 Royal Plaza Hotel, Marlborough, MA June 23, 2003

> Arpad Muranyi Signal Integrity Engineering Intel Corporation arpad.muranyi@intel.com

## Outline

- Problem statement

- A possible algorithm idea (not good)

- A better algorithm idea

- SPICE waveforms to prove second idea

## **Normal operation**

#### **HSPICE's B-element in version 99.4**

#### Disclaimer

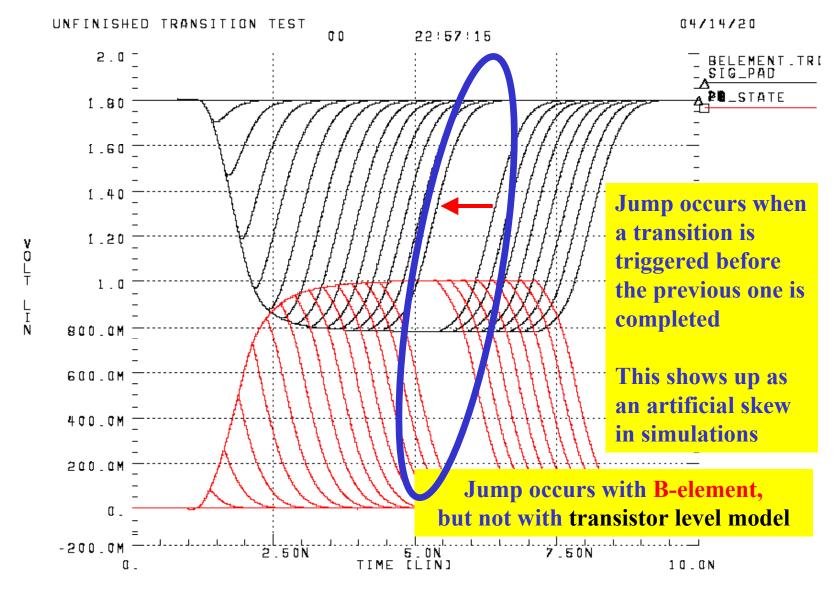

- Even though this problem was first discovered with HSPICE's B-element, this is not only an issue specific to HSPICE.

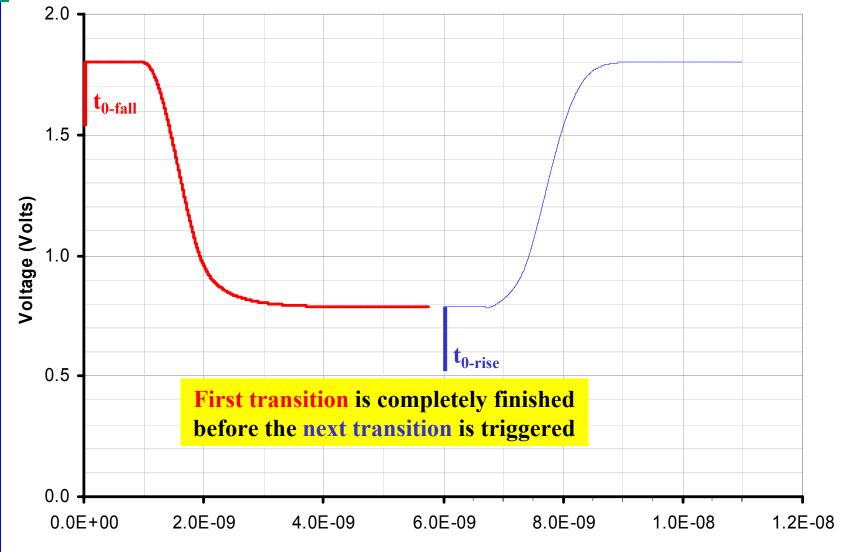

- The fundamental problem is that the IBIS specification was written with the assumption that a transition is always completed before a new transition begins.

- Since the IBIS specification does not address over-clocking, it is up to the tool vendor to deal with the situation when it arises.

- Each tool may have a different solution, some may seem to be correct (because they are not noticeable), but no one can really claim that they can reproduce the SPICE model's waveforms exactly when over-clocking occurs.

# **Conceptual explanation of the algorithm**

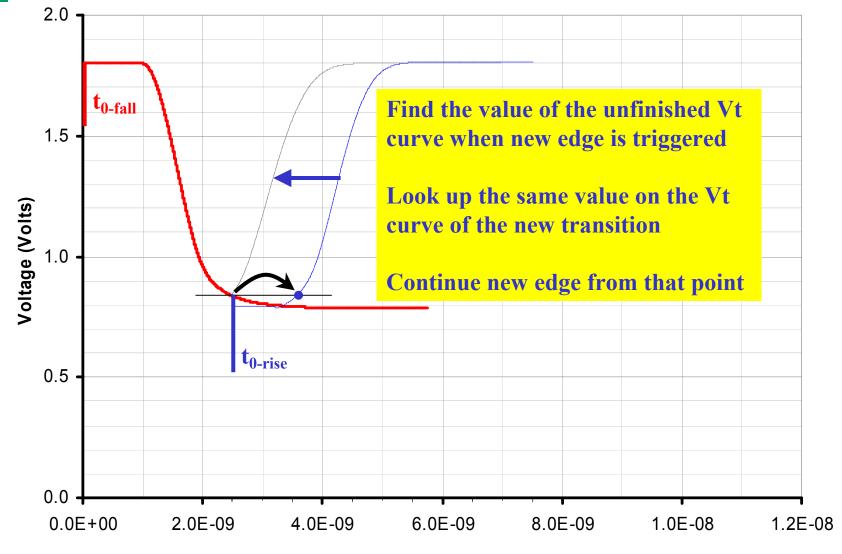

# Arpad's first algorithm idea (don't implement it)

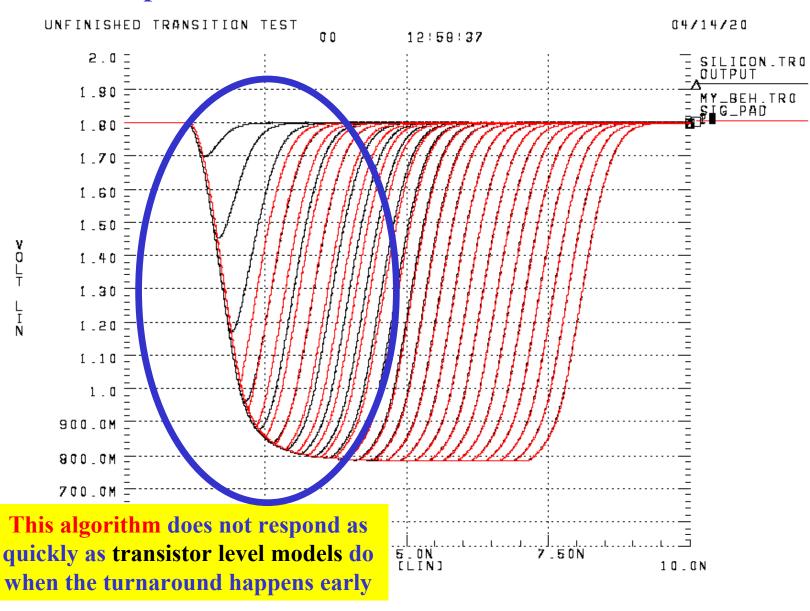

#### Arpad's first idea vs. transistor level model

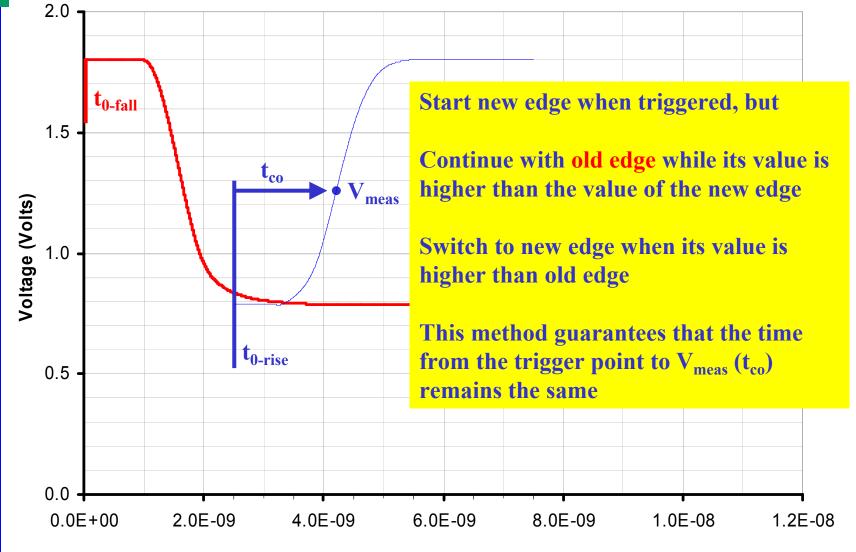

# Arpad's second algorithm idea

Delay t<sub>0-rise</sub> **Replace the lead-in portion of the Vt curve with an ideal delay**

Use the original B-element algorithm with this modified Vt curve, but add a delay every time it is triggered

CPD

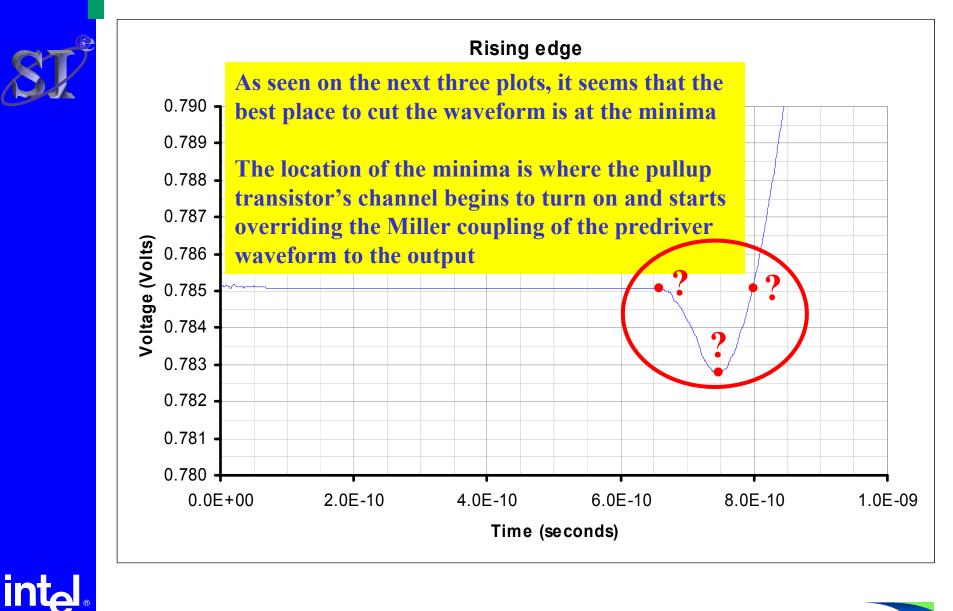

## Where exactly should the Vt curve be cut?

PAGE 10

#### Vt curve cut at left side

#### Vt curve cut at right side

SY

#### Vt curve cut at the minima yields best correlation

# Looking inside the SPICE model for explanations

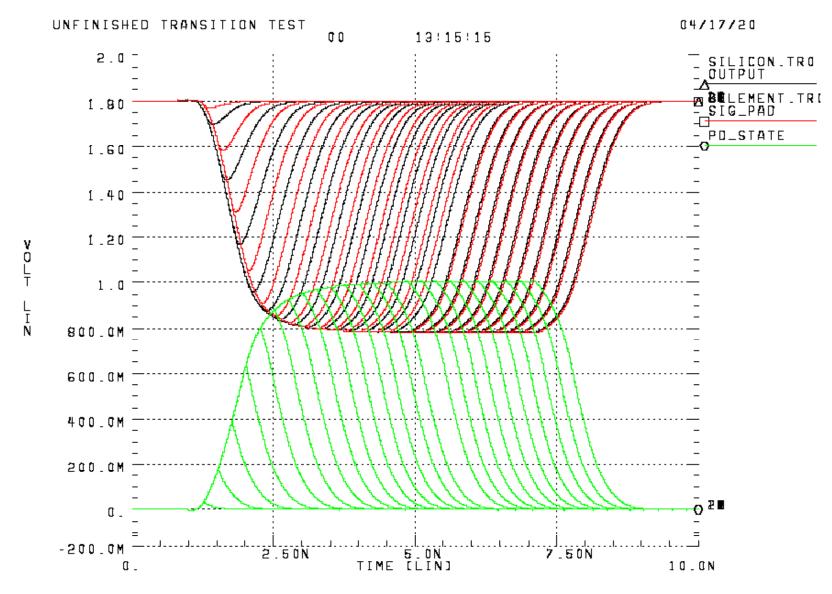

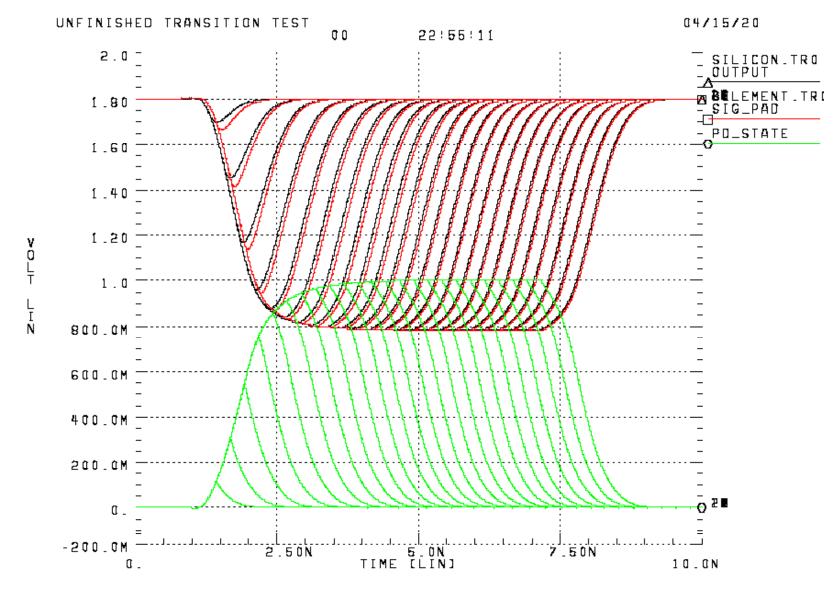

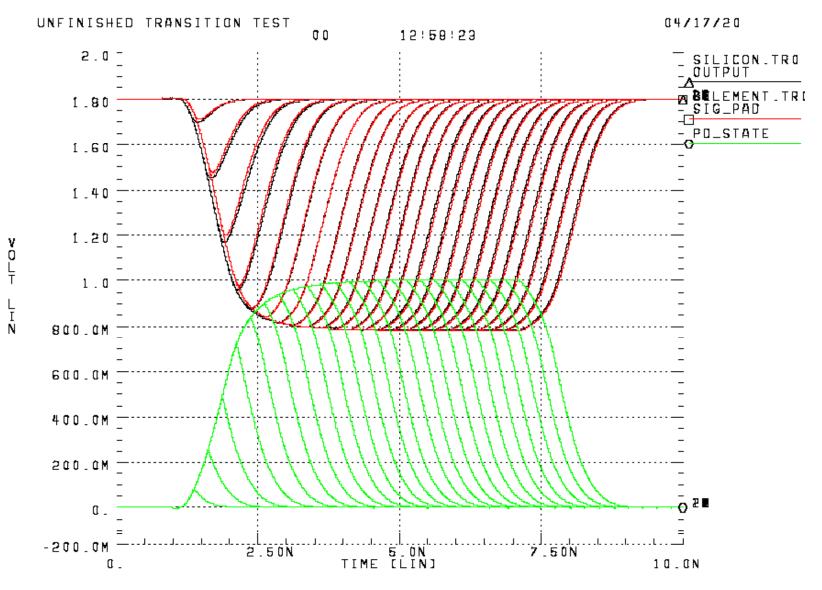

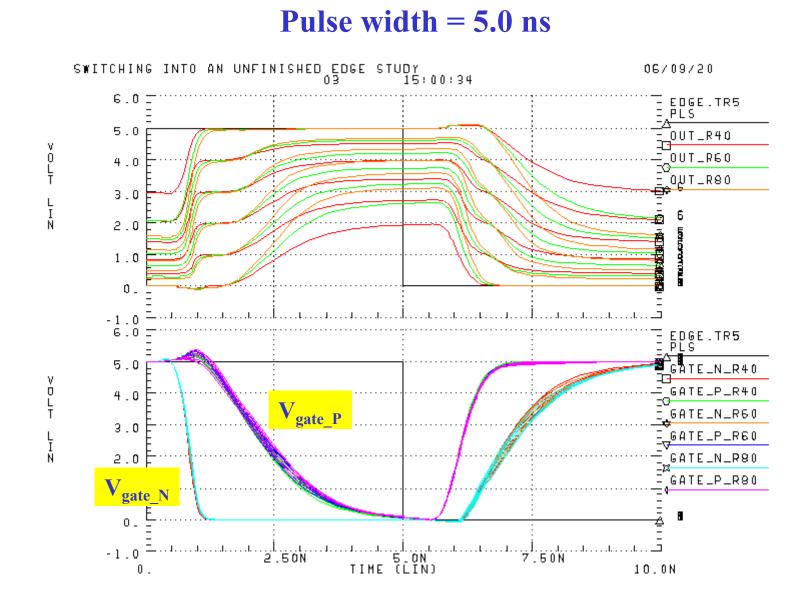

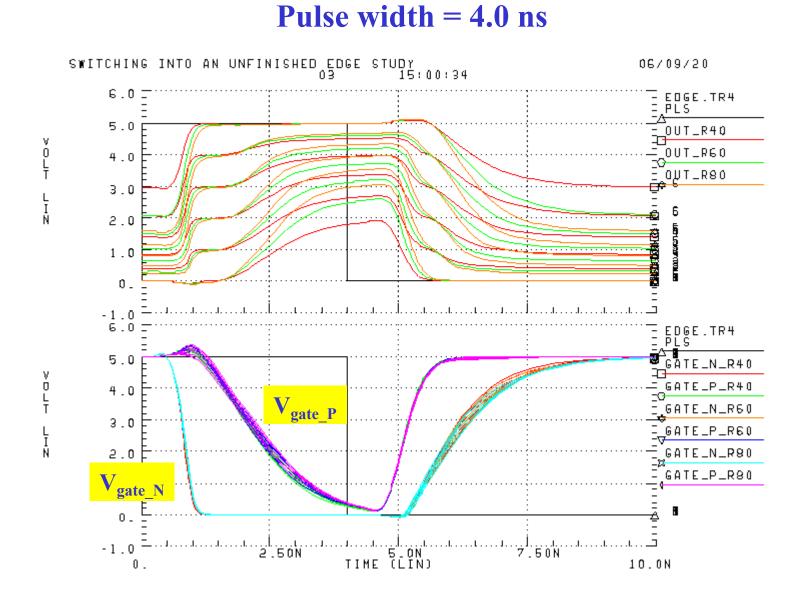

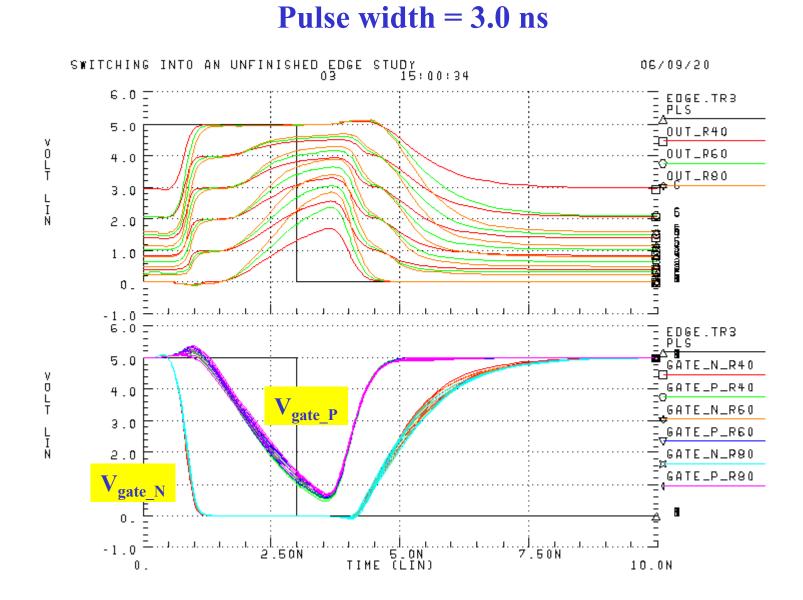

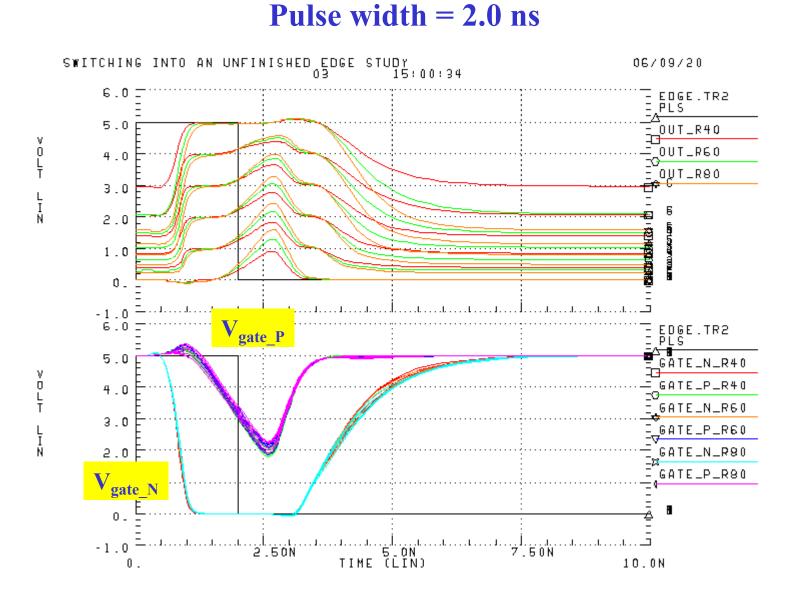

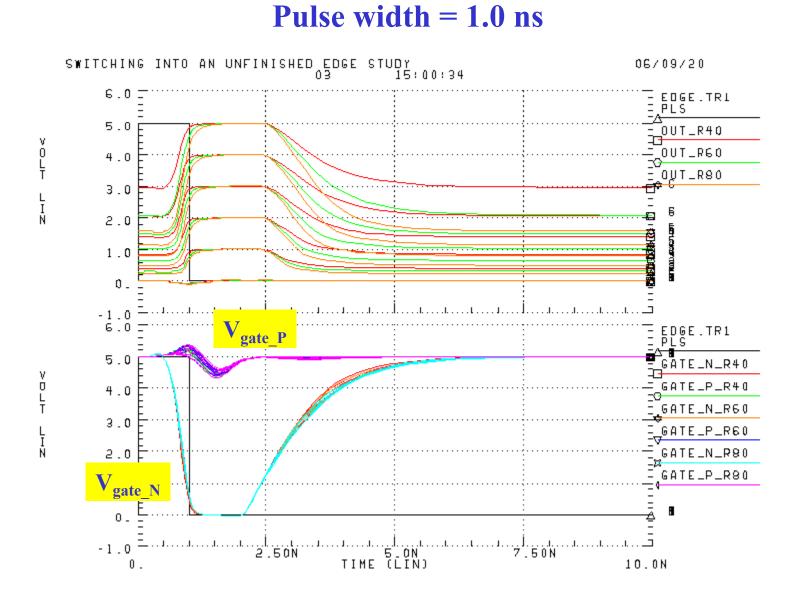

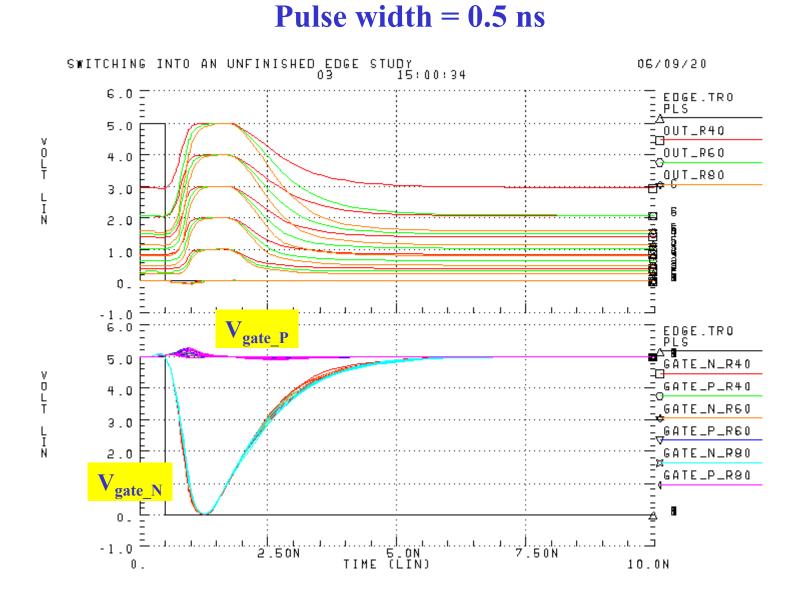

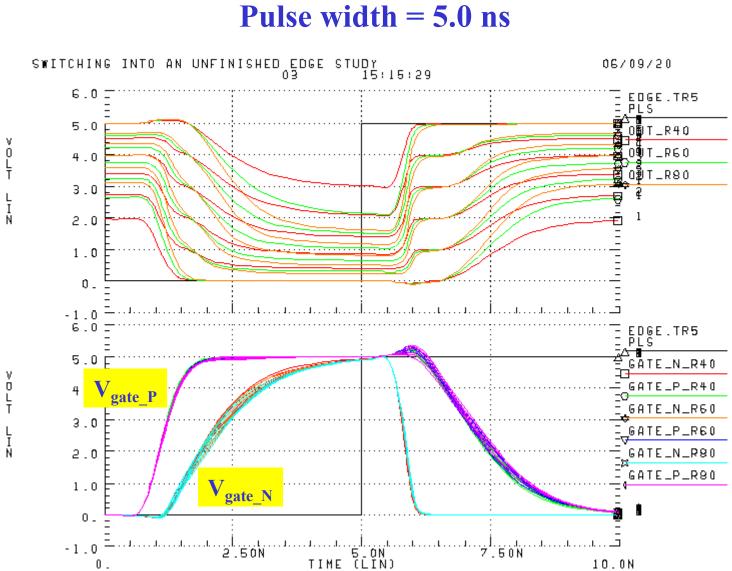

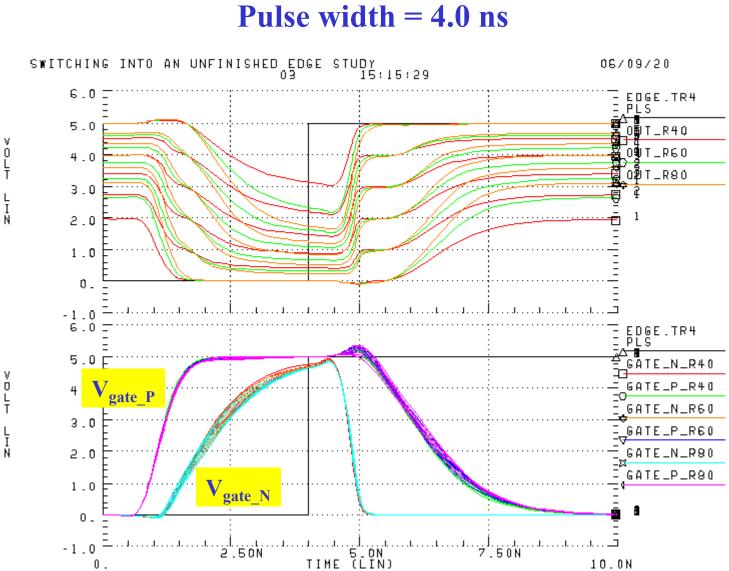

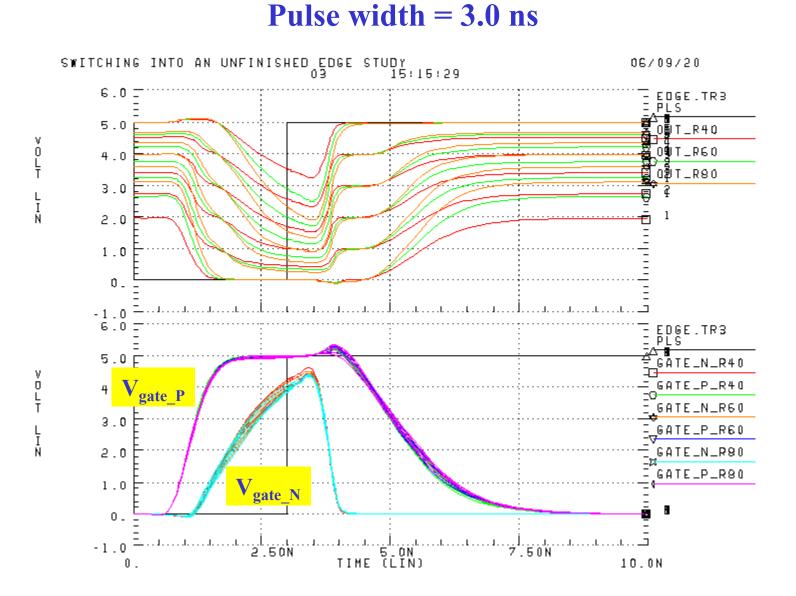

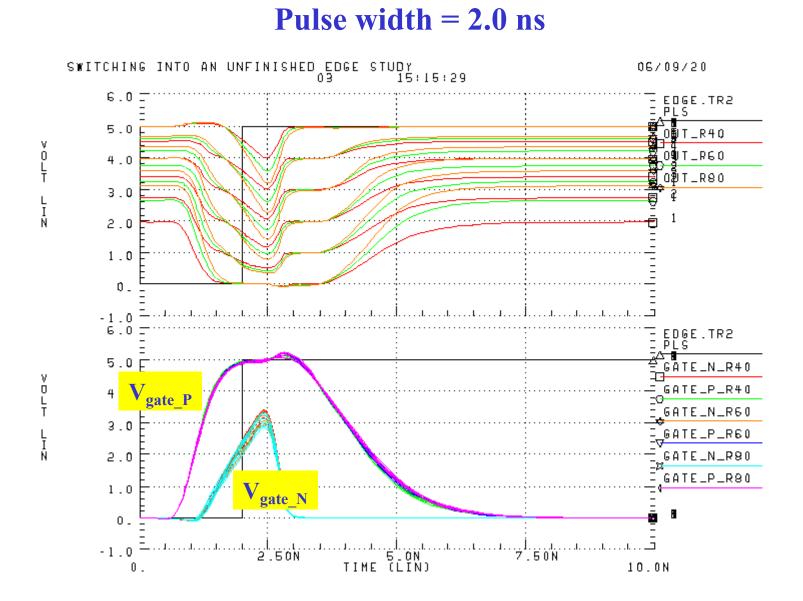

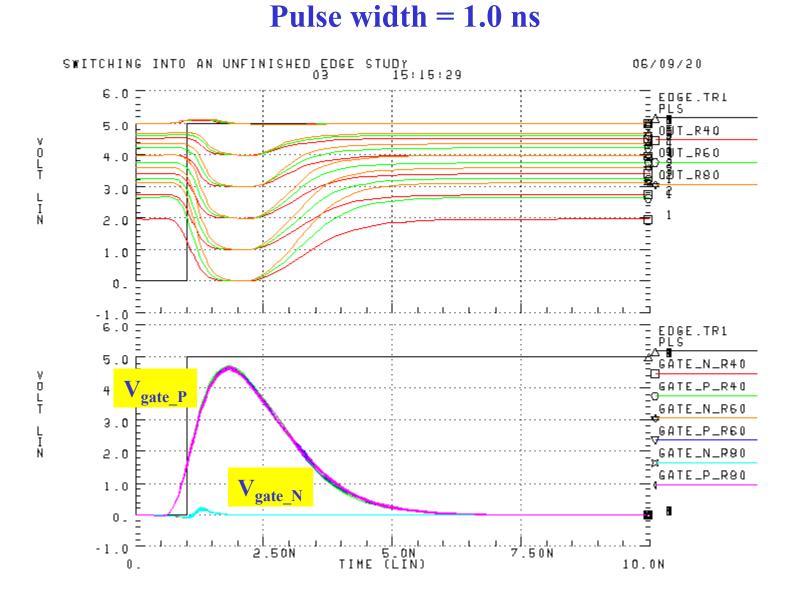

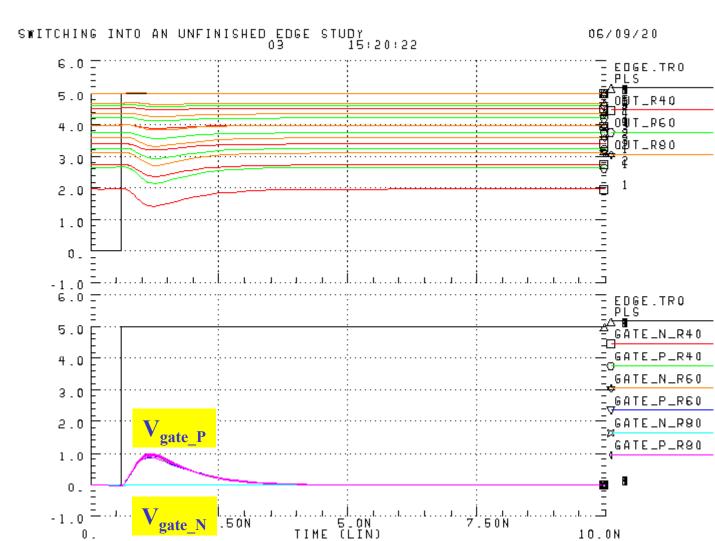

- We will look at two groups of six waveform sets.

- Rising edge followed by a falling edge

- Falling edge followed by a rising edge

- The second edge is brought closer to the first edge successively on each plot to watch the effects of over-clocking.

- The top plot shows waveforms on the output pad loaded by various  $R_{fixture} V_{fixture}$  combinations.

- 40, 60, 80 Ω

- 0, 1, 2, 3, 4, 5 V

- The bottom plot shows the pre-driver output waveforms for the N and P-channel output transistors (gate voltages).

- Watching the output and pre-driver waveforms relative to the stimulus pulse we can make some observations.

- There is a constant delay from the pulse to the pre-driver waveform

- This explains the need for a delay element to keep the duration of the lead in portion of the Vt curves (i.e. internal delay of buffer)

- The pre-driver waveforms turn around from the point they reached when over-clocking occurs

- This explains the need for "turning around" on the Vt curves also

SI

int<sub>e</sub>l.

• This page is put here only to serve as a separator page.

SV

**Pulse width = 0.6 ns**

Ŭ L T L N

٧

Ŭ L T

L I N

### Conclusions

- Looking at derivatives of the waveform could reveal the location where the output of the buffer really begins to switch

- The shape of the Vt curve may not always be usable for this purpose as a general solution

- A new parameter representing the internal delay(s) of a buffer may be a better way to do it.

- Need to develop a technique for model makers to measure this number

- Need to add a new keyword or sub-parameter to the IBIS specification associated with the waveforms