# Graphis

# **Driver Schedule Modeling**

Christopher E. Reid and Bob Ross

IBIS Summit Meeting

Las Vegas, Nevada

June 21, 2001

### **Contents**

- Driver Schedule Enhancement and Reduction Setups

- Possible Improvement for Over-clocked mode where start of next transition if before the finish of previous transition

- Application for SCSI

- Illustration of Driver Schedule for Discrete Waveform Shaping

# Driver Schedule Examples (D6 is not legal - ambiguous)

| Name       | Rise-on | Rise-off | Fall-on | Fall-off |

|------------|---------|----------|---------|----------|

| <b>D</b> 1 | 0       | na       | 0       | na       |

| <b>D2</b>  | na      | 0        | na      | 0        |

| <b>D3</b>  | 0       | 5ns      | na      | na       |

| <b>D4</b>  | 5ns     | 0        | na      | na       |

| <b>D5</b>  | na      | na       | 3ns     | 5ns      |

| <b>D6</b>  | 0       | 5ns      | 0       | 5ns      |

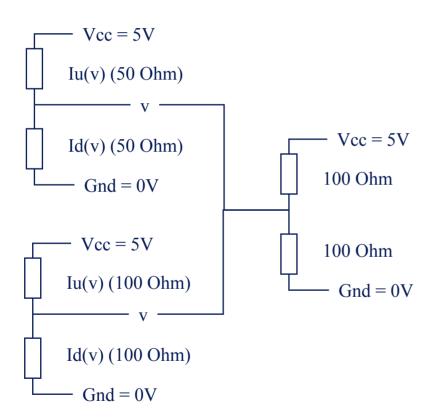

# Driver Schedule Test Circuit (Produces 1, 2, 3, 4 V outputs)

| Name | 50-Ohm | 100-Ohm | V |

|------|--------|---------|---|

| Ls   | Low    | Low     | 1 |

| Lw   | Low    | High    | 2 |

| Hw   | High   | Low     | 3 |

| Hs   | High   | High    | 4 |

# Valid Setup Examples for Enhancement and Reduction

| Driver | Rise-on | Rise-off | Fall-on | Fall-off |

|--------|---------|----------|---------|----------|

| D_50   | 0ns     | na       | 0ns     | na       |

| D_100  | 1ns     | na       | 1ns     | na       |

| Driver | Rise-on | Rise-off | Fall-on | Fall-off |

|--------|---------|----------|---------|----------|

| D_50   | 0ns     | na       | 0ns     | na       |

| D_100  | na      | 1ns      | na      | 1ns      |

| Driver | Rise-on | Rise-off | Fall-on | Fall-off |

|--------|---------|----------|---------|----------|

| D_50   | 0ns     | na       | 0ns     | na       |

| D_100  | 1ns     | 4ns      | na      | na       |

| Driver | Rise-on | Rise-off | Fall-on | Fall-off |

|--------|---------|----------|---------|----------|

| D_50   | 0ns     | na       | 0ns     | na       |

| D_100  | 4ns     | 1ns      | na      | na       |

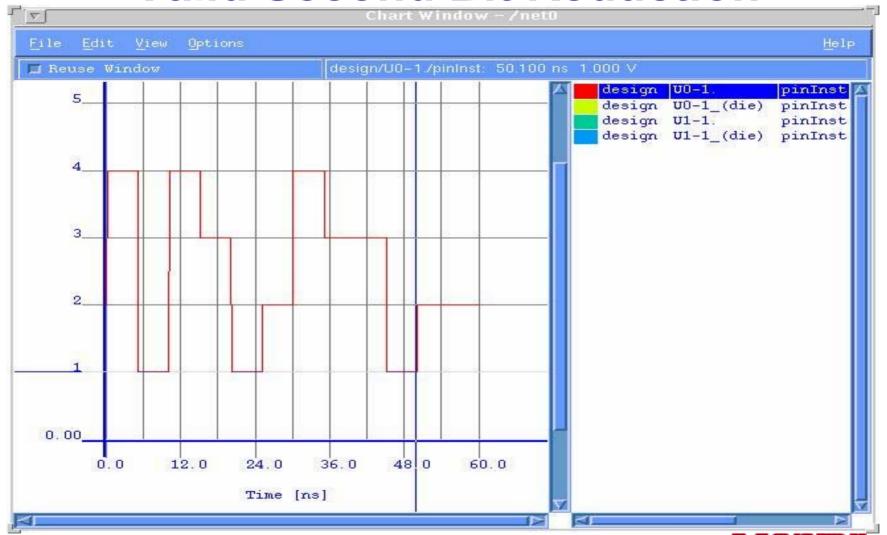

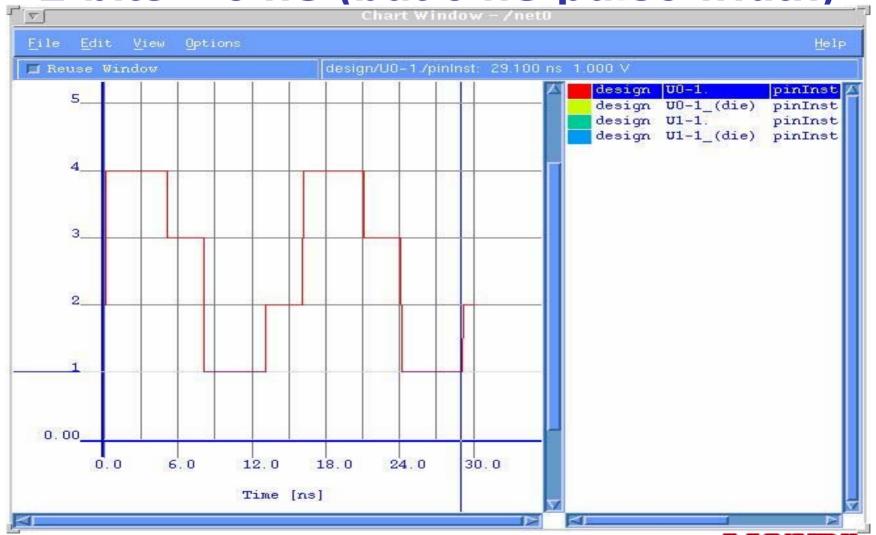

# SCSI Driver Example Using Reduced Strength Driver

| Driver | Rise-on | Rise-off | Fall-on | Fall-off |

|--------|---------|----------|---------|----------|

| D_50   | 0ns     | na       | 0ns     | na       |

| D_100  | na      | 5ns      | na      | 5ns      |

| Driver | Rise-on | Rise-off | Fall-on | Fall-off |

|--------|---------|----------|---------|----------|

| D_50   | 0       | na       | 0ns     | na       |

| D_100  | 0       | 5ns      | 0       | 5ns      |

#### **■** Two versions of the SCSI Driver

- Version 1 is legal IBIS next page

- Version 2 is not legal, but responds more cleanly to over-clocking. However the pulse widths are not made narrower and are wrong page after next.

### Valid Second Bit Reduction

## 2-bits = 8 nS (but 5 nS pulse width)

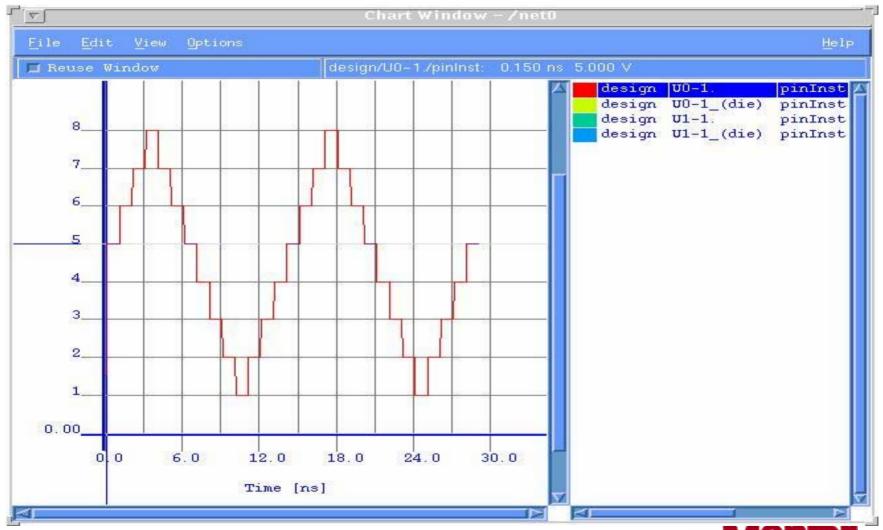

# Stair Step Waveform Showing Enhancement and Reduction

- Drivers (9 V)

- **U0 25 Ohm Output**

- U1 50 Ohm Open\_drain and Open\_source

- U2 100 Ohm Open\_drain and Open\_source

- Open\_\* used because of several transitions in "Rise\_\*" and "Fall\_\*" pulse

- Terminator 100 Ohm 9V, 100 Ohm Gnd

- 1 V to 8 V in 1 V Steps

```

min

typ

max

9V

[Voltage range]

NA

NA

[Driver Schedule]

Rise on Rise off Fall_on Fall_off

Model

U0

7n

NA

NA

U1 UP

2n

5n

NA

NA

U1 DOWN

2n

0 n

NA

NA

U1 DOWN

7n

5n

NA

NA

U1 UP

NA

2n

NA

0 n

U1 UP

NA

NA

7n

5n

U1 DOWN

NA

2n

5n

NA

U2 UP

2n

NA

NA

1n

U2 UP

3n

4 n

NA

NA

U2 UP

5n

6n

NA

NA

U2 DOWN

1n

0 n

NA

NA

U2 DOWN

3n

2n

NA

NA

U2 DOWN

5n

4 n

NA

NA

U2 DOWN

7n

6n

NA

NA

U2 UP

NA

NA

1n

0 n

U2 UP

NA

NA

3n

2n

U2 UP

NA

NA

5n

4 n

U2 UP

NA

NA

7n

6n

U2 DOWN

1n

2n

NA

NA

U2 DOWN

NA

NA

3n

4 n

U2 DOWN

NA

NA

5n

6n

```

# Pulse Width 7 nS, Period 14 nS

### **Driver Schedule Observations**

- Existing Driver Schedule can be used for second bit reduction for SCSI applications for a given clock rate.

- Allowing another Driver Schedule mode produces some improvement, but produces other distortions. This improvement is not recommended.

- Driver Schedules with Open\_\* modes can be used for discrete pulse shaping.