Model Connection Protocols for Chip-Package-Board System-level Analysis

IBIS Summit Design Automation Conference San Francisco, CA, USA July 28, 2009

Brad Brim Sigrity bradb@sigrity.com

# Agenda

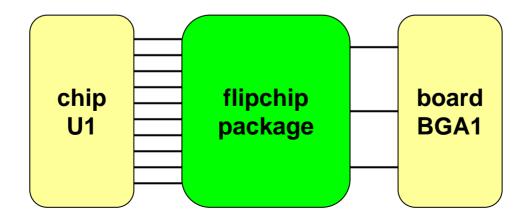

- Discuss concepts related to electrical model connectivity for chip/package/board system-level analysis

- Review existing solutions

- no standards exist

- some existing solution specifications are under NDA

- An example protocol specification and physical example

- Observations

### NOTE:

The Sigrity model connection protocol discussed in this presentation is not being proposed as a standard, merely as an example of an existing solution created in reaction to short term need and lack of existing standard protocols.

# The challenge

#### Assume I have ...

- a chip/package/board system with hundreds or thousands of physical connections (pins)

- individual electrical models for each chip, package and board

- I did not generate each of these models myself, therefore I do not have full knowledge of the pin mapping information for each model.

### How do I ...

- 1. know which pins of one model to connect to the pins of another model?

- 2. reliably and in reasonable time connect these models in a netlist or a schematic?

# Requirements

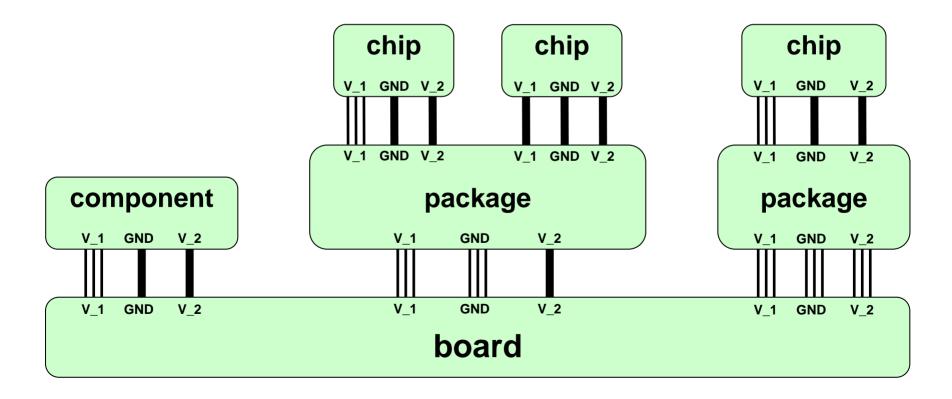

- Chip/package/board systems have many physical connections (pins)

- chip-package boundary ≈ 100 5000

package-board boundary ≈ 100 2000

- Not all electrical models can have pin-level resolution

- models may be too large to compute, store, etc.

- difficult to connect in EDA tools

- Adequate modeling may not be possible with net-level resolution

- especially, if this low resolution is applied throughout the entire system

- NOTE: "net-level resolution" groups all pins for each net at a domain boundary

#### Support is required for

- arbitrarily pin-grouped models

- automated connection amongst models in EDA tools

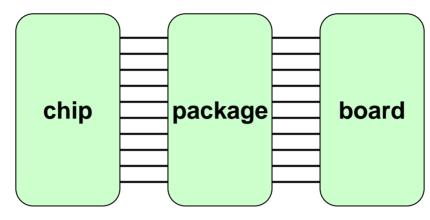

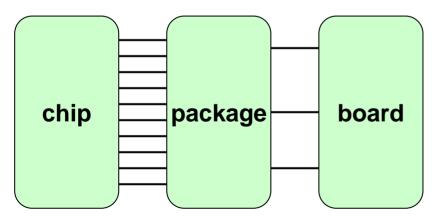

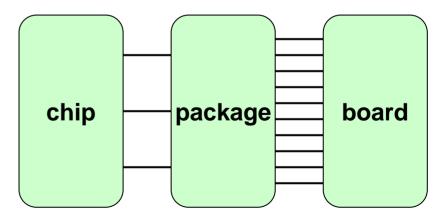

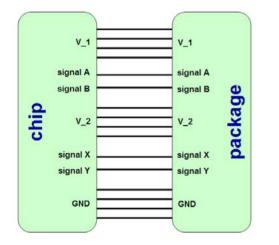

### **System Analysis**

**Physical connectivity**

**Chip-centric model abstraction**

**Board-centric model abstraction**

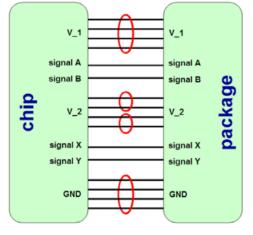

### **System Analysis**

A bit more detailed view of electrical model resolution through pin grouping, for one domain boundary

#### pin grouping

decreasing model resolution

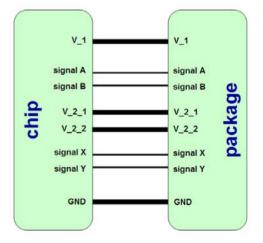

# **System Analysis**

modern system designs requires various levels of model resolution throughout the system, with pin-level, net-level and arbitrarily grouped pins applied to the same component

# Existing Model Connection Protocols for Chip/Package/Board Analysis

#### Sigrity MCP (Model Connection Protocol)

- defined by Sigrity

- publicly available definition

- objective to support chip/package/board system analysis

- presently Version 1.0

- 1.1 available soon with user-requested pin locations

### Apache CPP

- defined by Apache

- definition covered under NDA

- Implemented as "headers"

- Contained within model-native comment lines

- model could be either subcircuit or data file

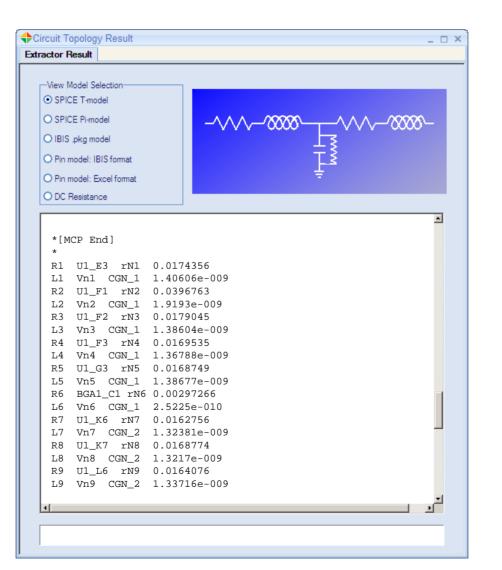

# A Typical Model Connection Protocol (Sigrity MCP)

| * | [MCP Begin]                                             |               |         |   |   |  |  |  |  |

|---|---------------------------------------------------------|---------------|---------|---|---|--|--|--|--|

| * | [MCP Ver] 1.1                                           |               |         |   |   |  |  |  |  |

| * | [Structure Type] {DIE PKG PCB}                          |               |         |   |   |  |  |  |  |

| * | [MCP Source] source text                                |               |         |   |   |  |  |  |  |

| * | [Coordinate Unit] <i>unit</i>                           |               |         |   |   |  |  |  |  |

| * | [Connection] connectionName partName numberPhysicalPins |               |         |   |   |  |  |  |  |

| * | [Connection Type] {DIE   PKG   PCB }                    |               |         |   |   |  |  |  |  |

| * | [Power Nets]                                            |               |         |   |   |  |  |  |  |

| * | pinName                                                 | modelNodeName | netName | X | У |  |  |  |  |

| * | •••                                                     |               |         |   |   |  |  |  |  |

| * | pinName                                                 | modelNodeName | netName | X | У |  |  |  |  |

| * | [Ground Nets]                                           |               |         |   |   |  |  |  |  |

| * | pinName                                                 | modelNodeName | netName | X | У |  |  |  |  |

| * | •••                                                     |               |         |   |   |  |  |  |  |

| * | pinName                                                 | modelNodeName | netName | X | У |  |  |  |  |

| * | [Signal Nets]                                           |               |         |   |   |  |  |  |  |

| * | pinName                                                 | modelNodeName | netName | X | У |  |  |  |  |

| * | •••                                                     |               |         |   |   |  |  |  |  |

| * | pinName                                                 | modelNodeName | netName | X | У |  |  |  |  |

| * | [MCP End]                                               |               |         |   |   |  |  |  |  |

# **A Typical Model Connection Protocol**

- Only one instance of [Structure Type]

- Multiple instances of [Connection] are possible

- for a single-die package there will be one die-type connection and one pcb-type connection

- for a pcb there may be many package type connections

- for a multi-die SiP package there may be multiple die-type connections

- Only one instance of [Connection Type] per [Connection]

- For power integrity applications there may be no signal nets in the model

- Not all physical pins must be documented, only those included in the electrical model

- For power integrity applications there may be no signal nets

- For Touchstone data files there may only be signal nets

- the reference terminal is implicit for the data file

- For SPICE subcircuits there are likely grounds net but maybe no power nets

- the reference terminal must be explicit

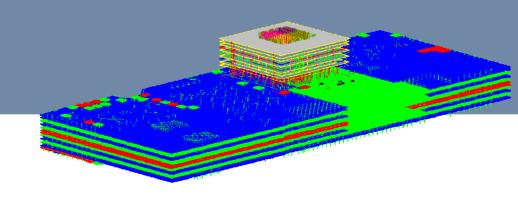

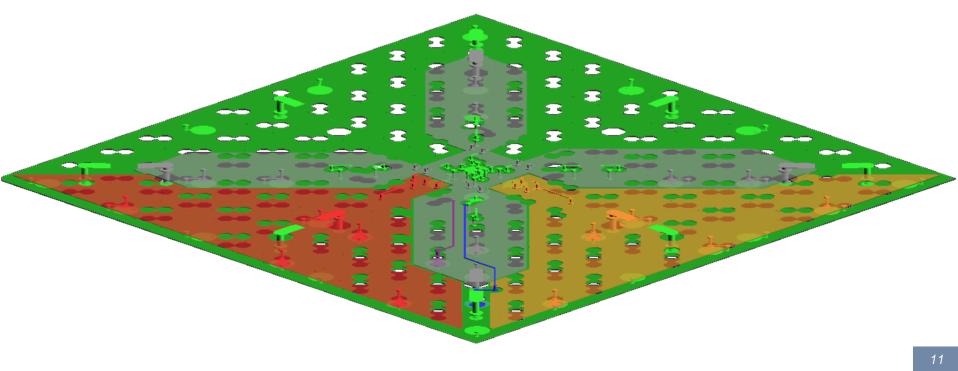

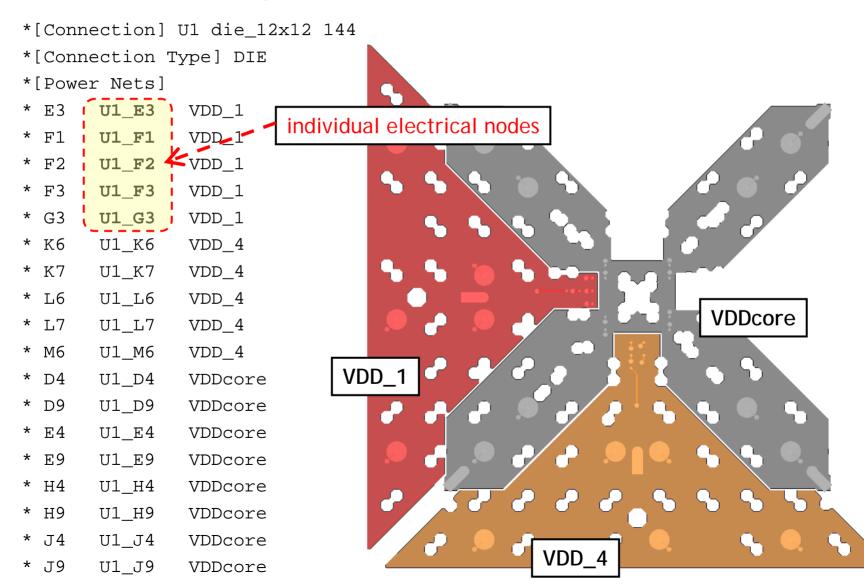

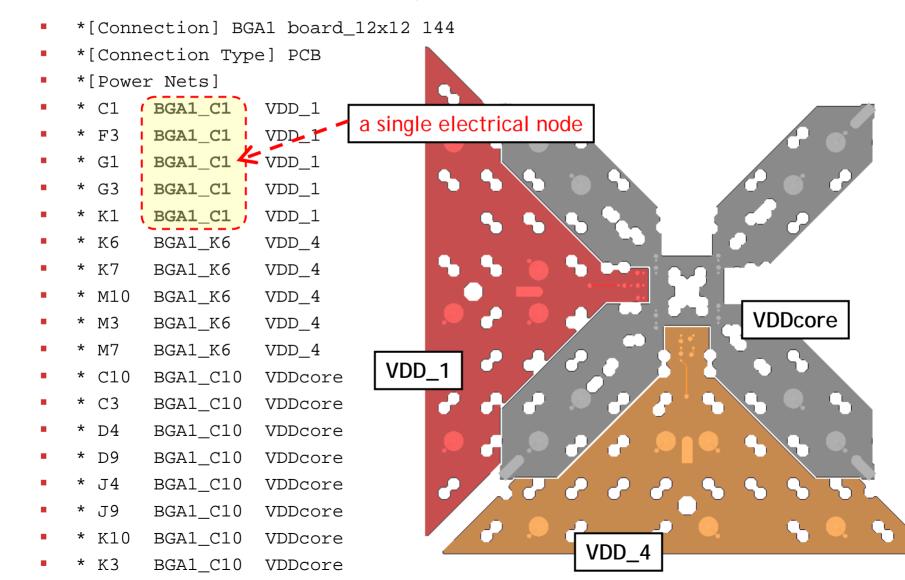

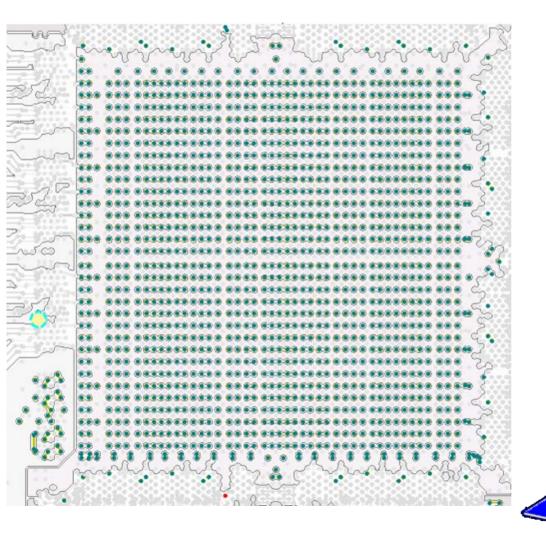

# A Physical Example

- a few nets in a small 4-layer flipchip BGA package (so the MCP sections fin on a single page)

- 3 power nets

- 1 ground net

- 2 signal nets

### 12-by-12 bump and ball arrays (for active nets)

die-side solder bumps

board-side solder balls

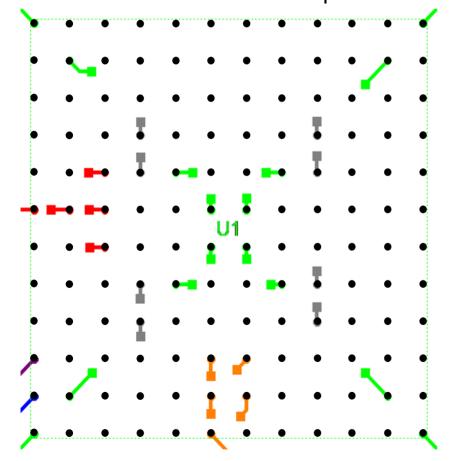

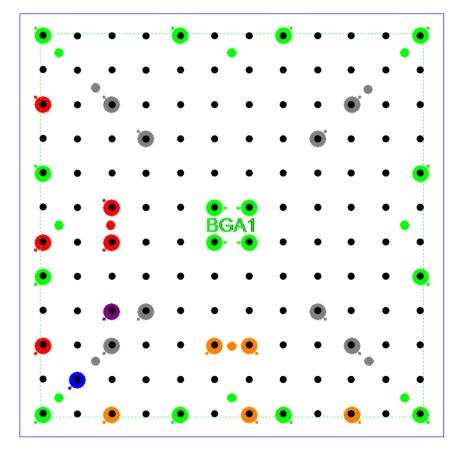

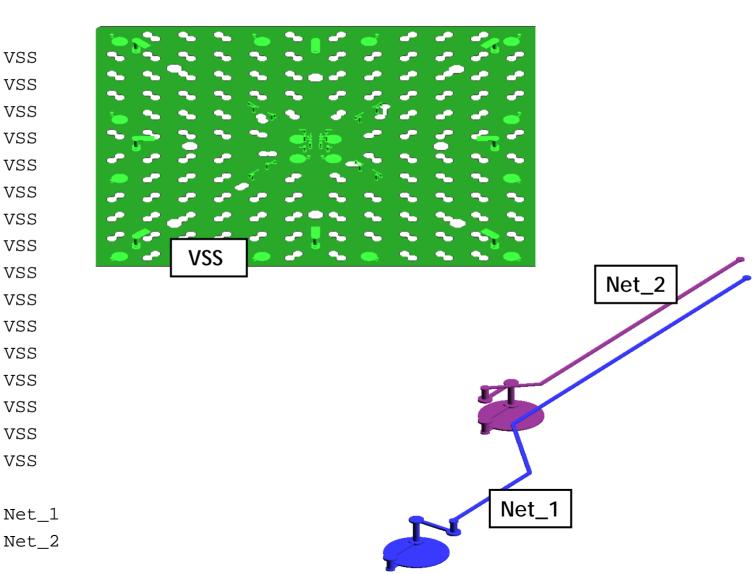

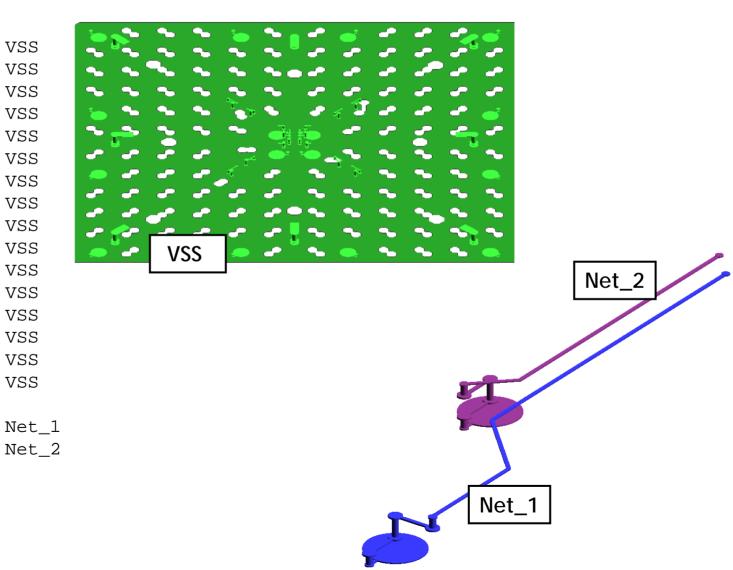

# Model Resolution

- pin-level at the chip-package boundary

- 36 physical pins 36 electrical nodes

- 18 power nodes -

- 16 ground nodes -

- 2 signal nodes -

- net-level at the package-board boundary

-

-

- 36 physical pins

- 3 power nodes

- 1 ground nodes -

- 2 signal nodes

Net\_1, Net\_2

- 6 electrical nodes

- 1 VDD\_1, 1 VDD\_4, 1 VDDcore

5 VDD\_1, 5 VDD\_4, 8 VDDcore

1 VSS

16 VSS

Net\_1, Net\_2

# **Model Extraction Setup**

die-side setup for pin-level model extraction

| Simulation Setup -> Simulation Type                                                                                                                                                                                                                                        |                                                          |  | ×                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|-----------------------------------------------------------------------------------------------------------------------------------------|

| Simulation Setup -> Simulation Type         Model Extraction         O Net-Based         Electrical Performance Assessment         O Signal Net Impedance and Coupling         O Power/Ground Net Loop Inductance         O Power/Ground Per Pin Resistance and Inductance | Layer Circuit Name<br>Signal \$M1 U1<br>Signal \$M4 BGA1 |  | Port Reference Reference Net: VSS OUse Reference Net OUse Reference Node OUse Reference Element Element ID: (0, 0) Pin Groups: 1 X 1 ~C |

| From die-side     O From board-side     OK     Cancel                                                                                                                                                                                                                      |                                                          |  |                                                                                                                                         |

- board-side setup for net-based model extraction

- equivalent to pin-level model extraction with 1-by-1 grid-based pin grouping

| Model Extraction O Net-Based Pin-Based Electrical Performance Assessment O Signal Net Impedance and Coupling O Power/Ground Net Loop Inductance O Power/Ground Per Pin Resistance and Inductance O From die-side O From board-side | Layer<br>Signal\$M1<br>Signal\$M4 | Circuit Name<br>U1<br>BGA1 | Port Reference<br>Reference Net:<br>VSS<br>VUse Reference Node<br>OUse Reference Element Element ID: (0, 0)<br>Pin Groups: 1 X 1 ~© |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

### A SPICE circuit with MCP header (a mixed pin-level/net-level model)

```

.SUBCKT FlipChip pkg SPICE

U1 E3 U1 F1 U1 F2 U1 F3 U1 G3

+

U1 K6 U1 K7 U1 L6 U1 L7 U1 M6

+

+ U1 D4 U1 D9 U1 E4 U1 E9 U1 H4 U1 H9 U1 J4 U1 J9

+ U1 A1 U1 A12 U1 B11 U1 B2 U1 E5 U1 E8 U1 F7 U1 G6

+ U1 G7 U1 H5 U1 H8 U1 L11 U1 L2 U1 M1 U1 M12 U1 F6

+ U1 L1 U1 K1

BGA1 C1 BGA1 K6 BGA1 C10 BGA1 A1 BGA1 L2 BGA1 J3

+

*

* The following is the Sigrity MCP Section

*[MCP Begin]

*[MCP Ver] 1.0

*[Structure Type] PKG

*[MCP Source] Sigrity XtractIM 3.0.2.07061 7/18/2009

```

### A SPICE circuit with MCP header (a pin-level die-side connection)

### A SPICE circuit with MCP header (a pin-level die-side connection)

| *[Ground Nets] |     |        |     |  |  |  |

|----------------|-----|--------|-----|--|--|--|

| *              | A1  | U1_A1  | VSS |  |  |  |

| *              | A12 | U1_A12 | VSS |  |  |  |

| *              | B11 | U1_B11 | VSS |  |  |  |

| *              | В2  | U1_B2  | VSS |  |  |  |

| *              | E5  | U1_E5  | VSS |  |  |  |

| *              | E8  | U1_E8  | VSS |  |  |  |

| *              | F7  | U1_F7  | VSS |  |  |  |

| *              | G6  | U1_G6  | VSS |  |  |  |

| *              | G7  | U1_G7  | VSS |  |  |  |

| *              | Н5  | U1_H5  | VSS |  |  |  |

| *              | Н8  | U1_H8  | VSS |  |  |  |

| *              | L11 | U1_L11 | VSS |  |  |  |

| *              | L2  | U1_L2  | VSS |  |  |  |

| *              | Ml  | U1_M1  | VSS |  |  |  |

| *              | M12 | U1_M12 | VSS |  |  |  |

| *              | Fб  | U1_F6  | VSS |  |  |  |

| *[Signal Nets] |     |        |     |  |  |  |

| *              | L1  | U1_L1  | Net |  |  |  |

| *              | Kl  | U1_K1  | Net |  |  |  |

### A SPICE circuit with MCP header (a net-base pcb-side connection)

### A SPICE circuit with MCP header (a net-level pcb-side connection)

- \*[Ground Nets]

- \* A1 BGA1\_A1

\* A12 BGA1\_A1

\* A5 BGA1\_A1

\* A8 BGA1\_A1

\* E1 BGA1\_A1

\* E12 BGA1\_A1

BGA1 A1

BGA1 A1

BGA1 A1

BGA1\_A1

BGA1\_A1

BGA1 A1

BGA1\_A1

BGA1\_A1

BGA1\_A1

BGA1\_A1

BGA1 L2

BGA1 J3

\*[Signal Nets]

\*[MCP End]

Fб

F7

G7

\* G6

\* H1

\* M1

\* M8

\* L2

\* J3

\*

\*

\* H12

\* M12

М5

\*

\*

\*

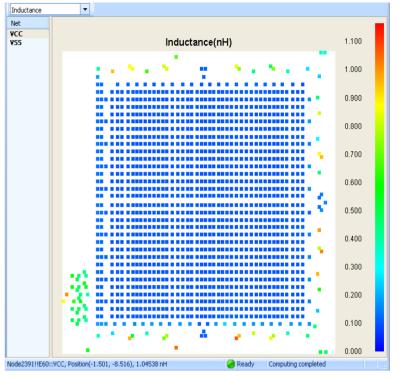

#### A SPICE circuit with MCP header

# A Typical Package (*one power net*)

3D inductance map

### **Observations**

- Chip/package/board designs may have thousands of pins

- Chip/package/board system analysis requires

- user-definable model resolution

- automated connection support for EDA tools

- Circuit and data models are commonly applied

- both should be supported by any connection protocol

- Model connection protocols are much more than simply "port names"

- Proprietary model connection protocols are currently being applied

- An industry standard model connection protocol should be defined

- user and EDA vendor participation will be required to agree on a standard

- active participation by more than a few individuals will be required

# Thank You!