### **Rantings of an IBIS Minimalist**

Ken Willis Product Engineering Director – High Speed Analysis Products IBIS Summit – DesignCon 2014 Santa Clara January 2014

#### cādence<sup>®</sup>

#### Agenda

- In the beginning ...

- Then what happened?

- What did we learn in 20 years?

- How should we handle interconnect?

- What is still missing?

#### In the Beginning ...

- Donald Telian (Intel) visited Cadence in 1993, to drum up support for a new standard called "IBIS"

- It meant "I/O Buffer Information Sheet"

- The focus was on:

- Replacing proprietary transistor-level IO models with industry standard IO models

- Providing a huge simulation speed-up, enabling much more system simulation to be performed

- Lumped package parasitics were OK

- Power was considered ideal

#### **Original IBIS Focus**

#### **Original Line of Demarcation for IBIS's Focus**

• IO Buffer

Interconnect

**IBIS spec domain**

EDA tool domain

#### Then what happened?

- Data rates went up ... and up ... and up

- IO buffer keywords were added to handle the new complexities

- We decided to model entire PCB signal paths (not power) with "EBD"

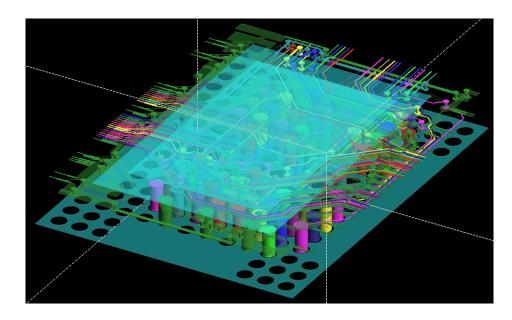

- Lumped package parasitics became distributed "Package Models" with IBIS-specified formats

- It turned out that some IO buffers didn't fit the IBIS cookie cutter template so well, and [External Model] was born, so you could use Spice subcircuits

- Key lesson here is "keyword explosion" vs. "general syntax"

- Packages became more and more custom, and were sometimes better represented with Spice subcircuits as [External Circuit]s

- Non-ideal power effects made it necessary to include on-die parasitics for some applications, leading to more [External Circuit]s

- Algorithmic modeling was invented to handle adaptive equalization

- Defined "ISS" so we could just use Spice to model anything custom

#### What did we learn in 20 years?

- Totally achieved the original focus:

- Replaced proprietary transistor-level IO models with industry-standard IBIS

- Got a huge simulation speed-up, simulation coverage skyrocketed

- You can standardize a small subcircuit if you can hard-code its top-level terminals

- Ex. in out power ground for an IO buffer

- Sometimes you just have to invent something new (but it is rare)

- Ex. algorithmic modeling for adaptive SerDes EQ

- Standardizing interconnect modeling is pretty difficult:

- Arbitrary number of terminals

- Hard to hard-code that

- As complexity goes up, keyword-driven specification breaks down, and we flank back to general Spice syntax

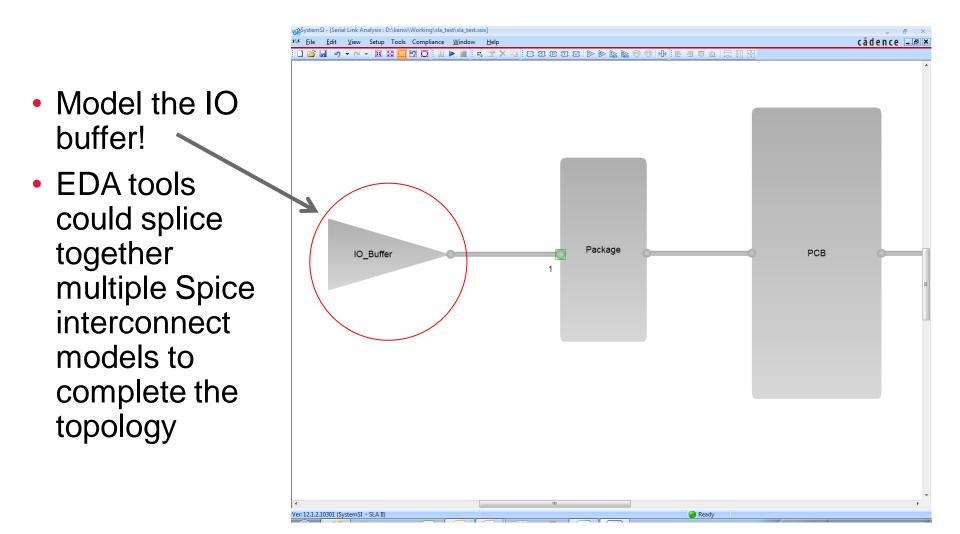

#### How should we handle interconnect?

- You need an interconnect model to simulate a whole driverreceiver path

- Interconnect can come from 2 main places:

- Your physical layout (if you have it), using EDA extraction tools

- From a supplier (internal or external)

- Do we need to invent a new format for interconnect modeling?

#### The Rant Page

#### [Begin Rant]

- NO!!!!!!! This is a solved problem!

- Interconnect model format is NOT some new thing we need to invent!

- We have modeled complex custom PCB interconnect in EDA tools for decades!

- Why are packages/interposers/RDL any different?

- You can model any interconnect in Spice!

- Now it is even standardized as "ISS"!

[End Rant]

#### What is Still Missing in IBIS?

A standard, convenient way to define connectivity between big interconnect Spice subcircuits

|                                                                                                                                                                                                                | llel Bus Analysis - D:\kenw\Working\pba_t                                                                                                                                                                                                                                                                                      | est/pba_test.ssixj                    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | - 8                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|                                                                                                                                                                                                                | <u>V</u> iew Setup Tools <u>W</u> indow <u>H</u> e                                                                                                                                                                                                                                                                             |                                       |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | cādence 🗕               |

| ) 📬 🖬 🔊                                                                                                                                                                                                        | - (* - H II 🗆 🖸 🚺 🕨                                                                                                                                                                                                                                                                                                            | • 🔳 🔼 🚰 🗙 🖣 🖽 🖾 🖻                     |     | 을 해 <u>때 때 다</u> 해 다                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                         |

|                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                | C<br>Controller                       | РСВ | M<br>Memory1<br>M<br>Memory2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                         |

|                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                |                                       |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                         |

|                                                                                                                                                                                                                | [a + 1                                                                                                                                                                                                                                                                                                                         |                                       | m   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                         |

| lock Name:                                                                                                                                                                                                     | Controller                                                                                                                                                                                                                                                                                                                     |                                       | m   | Block Name: PCB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                         |

| lock Name:<br>ionn. Port:                                                                                                                                                                                      | to_PCB                                                                                                                                                                                                                                                                                                                         |                                       |     | Conn. Port: U20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                         |

| lock Name:<br>ionn. Port:<br>PinName / Cktf                                                                                                                                                                    | to_PCB<br>NodeName / NetName (Sort By Net)                                                                                                                                                                                                                                                                                     | · · · · · · · · · · · · · · · · · · · |     | Conn. Port: U20 PinName / CktNodeName / NetName                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                         |

| llock Name:<br>Conn. Port:                                                                                                                                                                                     | to_PCB<br>NodeName / NetName (Sort By Net)<br>/ DQ6                                                                                                                                                                                                                                                                            |                                       |     | Conn. Port: U20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                         |

| llock Name:<br>Conn. Port:<br>PinName / Cktf<br>64 / 64                                                                                                                                                        | to_PCB<br>NodeName / NetName (Sort By Net)<br>/ DQ6<br>/ DQ7                                                                                                                                                                                                                                                                   | · · ·                                 |     | Conn. Port: U20 PinName / CktNodeName / NetName 64 / U20_AD18 / DDR_MDQ<6>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |

| llock Name:<br>Conn. Port:<br>PinName / Cktt<br>64 / 64<br>67 / 67<br>94 / 94<br>101 / 10                                                                                                                      | to_PCB<br>NodeName / NetName (Sort By Net)<br>/ DQ6<br>/ DQ7<br>/ DQ8<br>0 1 / DQ9                                                                                                                                                                                                                                             |                                       |     | Conn. Port:         U20           PinName / CktNodeName / NetName         64 / U20_AD18 / DDR_MDQ <6>           67 / U20_AD18 / DDR_MDQ <7>         94 / U20_AG10 / DDR_MDQ <1>           94 / U20_AG10 / DDR_MDQ <1>         101 / U20_AP19 / DDR_MDQ <1>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |

| Nock Name:<br>Conn. Port:<br>PinName / Cktt<br>64 / 64<br>67 / 67<br>94 / 94<br>101 / 10<br>96 / 96                                                                                                            | to_PCB<br>NodeName / NetName (Sort By Net)<br>/ DQ6<br>/ DQ7<br>/ DQ8<br>01 / DQ9<br>/ DQ10                                                                                                                                                                                                                                    |                                       |     | Conn. Port:         U20           PriName / CktNodeName / NetName            64 / U20_AD18 / DOR_MQQ<6>            67 / U20_AF19 / DDR_MQQ<7>            94 / U20_AF19 / DDR_MQQ<16>            101 / U20_AF19 / DDR_MQQ<16>            96 / U20_AF18 / DDR_MQQ<18>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |

| Block Name:<br>Conn. Port:<br>PinName / Cktt<br>64 / 64<br>67 / 67<br>94 / 94<br>101 / 10<br>96 / 96<br>99 / 99                                                                                                | to_PCB<br>NodeName / NetName (Sort By Net)<br>/ DQ6<br>/ DQ7<br>/ DQ8<br>11 / DQ9<br>/ DQ10<br>/ DQ10<br>/ DQ11                                                                                                                                                                                                                | · · · · · · · · · · · · · · · · · · · |     | Corn. Port:         U20           PinName / CktNodeName / NetName         64 / U20 _AD18 / DDR _MDQ <6>           67 / U20 _AD18 / DDR _MDQ <6>         67 / U20 _AD18 / DDR _MDQ <6>           94 / U20 _AG19 / DDR _MDQ <16>         101 / U20 _AH9 / DDR _MDQ <17>           96 / U20 _AH8 / DDR _MDQ <18>         99 / U20 _AD11 / DDR _MDQ <18>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                         |

| Nock Name:<br>Conn. Port:<br>PinName / Cktt<br>64 / 64<br>67 / 67<br>94 / 94<br>101 / 10<br>96 / 96<br>99 / 99<br>118 / 13                                                                                     | to_PCB<br>NodeName / NetName (Sort By Net)<br>/ DQ6<br>/ DQ7<br>/ DQ9<br>/ DQ10<br>/ DQ11<br>B / DQ12                                                                                                                                                                                                                          | <br><br>                              |     | Conn. Port:         U20           PinName / CktNodeName / NetName         64 / U20_AD18 / DDR_MDQ <6>           67 / U20_AD18 / DDR_MDQ <7>         94 / U20_AG10 / DDR_MDQ <1>           94 / U20_AF19 / DDR_MDQ <1>>         101 / U20_AF19 / DDR_MDQ <1>>           99 / U20_AD11 / DDR_MDQ <1>>         118 / U20_AF7 / DDR_MDQ <1>>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                         |

| lock Name:<br>conn. Port:<br>PinName / Cktt<br>64/64<br>67/67<br>94/94<br>101/10<br>96/96<br>99/99<br>118/11<br>111/13                                                                                         | to_PCB<br>NodeName / NetName (Sort By Net)<br>/DQ6<br>/DQ7<br>/DQ8<br>DJ1/DQ9<br>/DQ10<br>/DQ11<br>18 /DQ12<br>L1/DQ13                                                                                                                                                                                                         |                                       |     | Conn. Port:         U20           PinName / CktNodeName / NetName         64 / U20_AD18 / DDR_MQ<6>           67 / U20_AD18 / DDR_MDQ<7>         94 / U20_AG10 / DDR_MDQ<15>           101 / U20_AG10 / DDR_MDQ<15>         101 / U20_AG10 / DDR_MDQ<15>           96 / U20_AH8 / DDR_MDQ<15>         118 / U20_AH8 / DDR_MDQ<15>           118 / U20_AH1 / DDR_MDQ<20>         118 / U20_AH7 / DDR_MDQ<20>           111 / U20_AG7 / DDR_MDQ<21>         118 / U20_AH7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                         |

| lock Name:<br>ionn. Port:<br>PinName / Cktt<br>64 / 64<br>67 / 67<br>94 / 94<br>101 / 10<br>96 / 96<br>99 / 99<br>118 / 11<br>111 / 11<br>116 / 11                                                             | to_PCB<br>NodeName / NetName (Sort By Net)<br>/ DQ6<br>/ DQ7<br>/ DQ9<br>/ DQ10<br>/ DQ11<br>B / DQ12                                                                                                                                                                                                                          |                                       |     | Conn. Port:         U20           PinName / CktNodeName / NetName         64 / U20_AD18 / DDR_MDQ <6>           67 / U20_AD18 / DDR_MDQ <7>         94 / U20_AG10 / DDR_MDQ <1>           94 / U20_AF19 / DDR_MDQ <1>>         101 / U20_AF19 / DDR_MDQ <1>>           99 / U20_AD11 / DDR_MDQ <1>>         118 / U20_AF7 / DDR_MDQ <1>>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                         |

| lock Name:<br>ionn. Port:<br>PinName / Cktt<br>64 / 64<br>67 / 67<br>94 / 94<br>101 / 11<br>96 / 96<br>99 / 99<br>118 / 11<br>111 / 11<br>116 / 11<br>113 / 11<br>77 / 77                                      | to_PCB           VodeName / NetName (Sort By Net)           /DQ6           /DQ7           /DQ8           01 /DQ9           /DQ10           /DQ11           18 /DQ12           11 /DQ13           16 /DQ14           13 /DQ15           /DQ5                                                                                    |                                       |     | Corn. Port:         U20           PinName / CktNodeName / NetWame         64 / U20 _AD18 / DOR _MDQ <6>           67 / U20 _AD18 / DOR _MDQ <7>         94 / U20 _AD18 / DOR _MDQ <1>           94 / U20 _AG19 / DOR _MDQ <16>         101 / U20 _AH9 / DOR _MDQ <12>           95 / U20 _AH9 / DOR _MDQ <12>         118 / U20 _AH7 / DOR _MDQ <12>           118 / U20 _AH7 / DOR _MDQ <12>         111 / U20 _AF7 / DOR _MDQ <2>           113 / U20 _AF7 / DOR _MDQ <2>         113 / U20 _AF7 / DOR _MDQ <2>           113 / U20 _AF7 / DOR _MDQ <2>         113 / U20 _AF7 / DOR _MDQ <2>           113 / U20 _AF7 / DOR _MDQ <2>         113 / U20 _AF7 / DOR _MDQ <2>           114 / U20 _AF7 / DOR _MDQ <2>         114 / U20 _AF7 / DOR _MDQ <2>           115 / U20 _AF7 / DOR _MDQ <2>         114 / U20 _AF7 / DOR _MDQ <2>                                                                                                                                                                             |                         |

| Nock Name:<br>conn. Port:<br>PinName / Cktt<br>64 / 64<br>64 / 64<br>67 / 67<br>94 / 94<br>101 / 10<br>96 / 96<br>99 / 99<br>118 / 11<br>116 / 11<br>113 / 11<br>77 / 77<br>75 / 75                            | to_PCB           VkodeName / NetName (Sort By Net)           / DQ6           / DQ7           / DQ8           D1 / DQ9           / DQ11           18 / DQ12           11 / DQ13           16 / DQ14           13 / DQ15           / LDQ5                                                                                        |                                       |     | Corn. Port:         U20           PinName / CktNodeName / NetName         64 / U20 _AD18 / DDR _MDQ <6>           67 / U20 _AD18 / DDR _MDQ <6>         67           94 / U20 _AD19 / DDR _MDQ <7>         94 / U20 _AD19 / DDR _MDQ <1>           94 / U20 _AD19 / DDR _MDQ <1>>         99 / U20 _AD11 / DDR _MDQ <1>>           99 / U20 _AH47 / DDR _MDQ <1>>         118 / U20 _AH47 / DDR _MDQ <2>           118 / U20 _AF7 / DDR _MDQ <2>         113 / U20 _AF8 / DDR _MDQ <2>           113 / U20 _AF8 / DDR _MDQ <2>         113 / U20 _AF17 / DDR _MDQ <2>           77 / U20 _AG21 / DDR _MDQ <5                                                                                                                                                                                                                                                                                                                                                                                                          |                         |

| Nock Name:<br>Conn. Port:<br>PinName / Cktt<br>64 / 64<br>67 / 67<br>94 / 94<br>101 / 11<br>96 / 96<br>99 / 99<br>118 / 11<br>111 / 11<br>113 / 11<br>77 / 77<br>75 / 75<br>104 / 10                           | to_PCB VodeName / NetVame (Sort By Net) /DQ6 /DQ7 /DQ8 01/DQ9 /DQ10 18/DQ12 11/DQ11 18/DQ12 11/DQ13 16/DQ14 13/DQ15 /LQQ8 /LDQS#                                                                                                                                                                                               |                                       |     | Conn. Port:         U20           PinName / CktNodeName / NetName         64 / U20_AD18 / DDR_MDQ <6>           67 / U20_AD18 / DDR_MDQ <6>         101 / U20_AP19 / DDR_MDQ <1>           94 / U20_AG10 / DDR_MDQ <1>         96 / U20_AP19 / DDR_MDQ <1>           99 / U20_AP19 / DDR_MDQ <1>         116 / U20_AP1 / DDR_MDQ <1>           116 / U20_AP7 / DDR_MDQ <2>         116 / U20_AP6 / DDR_MDQ <2>           111 / U20_AP7 / DDR_MDQ <2>         113 / U20_AP7 / DDR_MDQ <2>           113 / U20_AP7 / DDR_MDQ <2>         113 / U20_AP7 / DDR_MDQ <2>           113 / U20_AP7 / DDR_MDQ <2>         113 / U20_AP7 / DDR_MDQ <2>           113 / U20_AP7 / DDR_MDQ <2>         113 / U20_AP7 / DDR_MDQ <2>           114 / U20_AP7 / DDR_MDQ <2>         113 / U20_AP7 / DDR_MDQ <2>           115 / U20_AP7 / DDR_MDQ <2>         113 / U20_AP7 / DDR_MDQ <2>           75 / U20_AF7 / DDR_MDQS1         104 / U20_A97 / DDR_MDQS1           104 / U20_A97 / DDR_MDQS2         104 / U20_A97 / DDR_MDQS1 |                         |

| Nock Name:<br>Conn. Port:<br>PinName / Cktt<br>64 / 64<br>67 / 67<br>94 / 94<br>101 / 10<br>96 / 96<br>99 / 99<br>118 / 11<br>116 / 11<br>116 / 11<br>117 / 77<br>75 / 75<br>104 / 10<br>106 / 10              | to_PCB<br>NodeName / NetName (Sort By Net)<br>/DQ6<br>/DQ7<br>/DQ8<br>01 /DQ9<br>/DQ10<br>10 /DQ11<br>16 /DQ11<br>13 /DQ13<br>16 /DQ14<br>13 /DQ15<br>/LQQ5<br>04 /LQQ5<br>06 /LQQ5≠<br>06 /LQQ5≠                                                                                                                              |                                       |     | Corn. Port:         U20           PinName / CktNodeName / NetName         64 / U20 _AD18 / DDR _MDQ <6>           67 / U20 _AD18 / DDR _MDQ <6>         65           67 / U20 _AD18 / DDR _MDQ <6>         6           94 / U20 _AD19 / DDR _MDQ <16>         91           95 / U20 _AD11 / DDR _MDQ <18>         99 / U20 _AD11 / DDR _MDQ <18>           99 / U20 _AD11 / DDR _MDQ <2>         111 / U20 _AF8 / DDR _MDQ <2>           113 / U20 _AF7 / DDR _MDQ <2>         111 / U20 _AF8 / DDR _MDQ <2>           113 / U20 _AF8 / DDR _MDQ <2>         116 / U20 _AF8 / DDR _MDQ <2>           114 / U20 _AF8 / DDR _MDQ <2>         114 / U20 _AF8 / DDR _MDQ <2>           114 / U20 _AF8 / DDR _MDQ <2>         114 / U20 _AF8 / DDR _MDQ <2>           116 / U20 _AF8 / DDR _MDQ <2>         111 / U20 _AF8 / DDR _MDQ <2>           116 / U20 _AF8 / DDR _MDQ <2>         111 / U20 _AF8 / DDR _MDQ <2>           116 / U20 _AF8 / DDR _MDQ <2>         111 / U20 _AF8 / DDR _MDQ <2>                      |                         |

|                                                                                                                                                                                                                | to_PCB<br>NodeName / NetName (Sort By Net)<br>/DQ6<br>/DQ7<br>/DQ8<br>01 /DQ9<br>/DQ10<br>10 /DQ11<br>16 /DQ11<br>13 /DQ13<br>16 /DQ14<br>13 /DQ15<br>/LQQ5<br>04 /LQQ5<br>06 /LQQ5≠<br>06 /LQQ5≠                                                                                                                              |                                       |     | Corn. Port:         U20           PinName / CktNodeName / NetName         64 / U20 _AD18 / DDR _MDQ <6>           67 / U20 _AD18 / DDR _MDQ <6>         65           67 / U20 _AD18 / DDR _MDQ <6>         101 / U20 _AP19 / DDR _MDQ <1>           96 / U20 _AP19 / DDR _MDQ <1>>         101 / U20 _AP19 / DDR _MDQ <1>>           99 / U20 _AP19 / DDR _MDQ <1>>         118 / U20 _AP17 / DDR _MDQ <2>           118 / U20 _AP17 / DDR _MDQ <2>         113 / U20 _AP17 / DDR _MDQ <2>           113 / U20 _AP17 / DDR _MQQ <2>         113 / U20 _AP17 / DDR _MQQ <2>           114 / U20 _AP3 / DDR _MQQ <2>         114 / U20 _AP3 / DDR _MQQ <2>           115 / U20 _AP3 / DDR _MQQ <2>         114 / U20 _AP3 / DDR _MQQ <2>           120 _AD21 / DDR _MQQ <2>         113 / U20 _AP3 / DDR _MQQ <2>           13 / U20 _AP3 / DDR _MQQ <2>         104 / U20 _AP3 / DDR _MQQ <2>           13 / U20 _AP3 / DDR _MQQ <2>         104 / U20 _AP3 / DDR _MQQ <2>           138 / U20 _AP3 / DDR _MQQ <3      |                         |

| Block Name:<br>Conn. Port:<br>PinName / Cktt<br>64 / 64<br>67 / 67<br>94 / 94<br>101 / 10<br>96 / 96<br>99 / 96<br>99 / 118 / 11<br>116 / 11<br>113 / 11<br>77 / 77<br>75 / 75<br>106 / 10<br>88 / 38          | to_PCB<br>NodeName / NetName (Sort By Net)<br>/DQ6<br>/DQ7<br>/DQ8<br>01 /DQ9<br>/DQ10<br>10 /DQ11<br>16 /DQ11<br>13 /DQ13<br>16 /DQ14<br>13 /DQ15<br>/LQQ5<br>04 /LQQ5<br>06 /LQQ5≠<br>06 /LQQ5≠                                                                                                                              |                                       |     | Corn. Port:         U20           PinName / CktNodeName / NetName         64 / U20 _AD18 / DDR _MDQ <6>           67 / U20 _AD18 / DDR _MDQ <6>         65           67 / U20 _AD18 / DDR _MDQ <6>         101 / U20 _AP19 / DDR _MDQ <1>           96 / U20 _AP19 / DDR _MDQ <1>>         101 / U20 _AP19 / DDR _MDQ <1>>           99 / U20 _AP19 / DDR _MDQ <1>>         118 / U20 _AP17 / DDR _MDQ <2>           118 / U20 _AP17 / DDR _MDQ <2>         113 / U20 _AP17 / DDR _MDQ <2>           113 / U20 _AP17 / DDR _MQQ <2>         113 / U20 _AP17 / DDR _MQQ <2>           114 / U20 _AP3 / DDR _MQQ <2>         114 / U20 _AP3 / DDR _MQQ <2>           115 / U20 _AP3 / DDR _MQQ <2>         114 / U20 _AP3 / DDR _MQQ <2>           120 _AD21 / DDR _MQQ <2>         113 / U20 _AP3 / DDR _MQQ <2>           13 / U20 _AP3 / DDR _MQQ <2>         104 / U20 _AP3 / DDR _MQQ <2>           13 / U20 _AP3 / DDR _MQQ <2>         104 / U20 _AP3 / DDR _MQQ <2>           138 / U20 _AP3 / DDR _MQQ <3      |                         |

| 3lock Name:<br>Conn. Port:<br>PinName / Cktt<br>64 / 64<br>67 / 67<br>94 / 94<br>101 / 12<br>96 / 96<br>99 / 99<br>118 / 11<br>116 / 11<br>115 / 11<br>115 / 11<br>117 / 77<br>75 / 75<br>104 / 10<br>106 / 12 | to_PCB           VodeName / NetName (Sort By Net)           /DQ6           /DQ7           /DQ8           01 /DQ9           /DQ1           18 /DQ12           11 /DQ13           16 /DQ14           13 /DQ15           /LDQ5           1/DQ5           1/DQ5           1/DQ5           /LDQ5           /LDQ5           16 /DQ14 |                                       |     | Corn. Port:         U20           PinName / CktNodeName / NetName         64 / U20 _AD18 / DDR _MDQ <6>           67 / U20 _AD18 / DDR _MDQ <6>         65           67 / U20 _AD18 / DDR _MDQ <6>         101 / U20 _AP19 / DDR _MDQ <1>           96 / U20 _AP19 / DDR _MDQ <1>>         101 / U20 _AP19 / DDR _MDQ <1>>           99 / U20 _AP19 / DDR _MDQ <1>>         118 / U20 _AP17 / DDR _MDQ <2>           118 / U20 _AP17 / DDR _MDQ <2>         113 / U20 _AP17 / DDR _MDQ <2>           113 / U20 _AP17 / DDR _MQQ <2>         113 / U20 _AP17 / DDR _MQQ <2>           114 / U20 _AP3 / DDR _MQQ <2>         114 / U20 _AP3 / DDR _MQQ <2>           115 / U20 _AP3 / DDR _MQQ <2>         114 / U20 _AP3 / DDR _MQQ <2>           120 _AD21 / DDR _MQQ <2>         113 / U20 _AP3 / DDR _MQQ <2>           13 / U20 _AP3 / DDR _MQQ <2>         104 / U20 _AP3 / DDR _MQQ <2>           13 / U20 _AP3 / DDR _MQQ <2>         104 / U20 _AP3 / DDR _MQQ <2>           138 / U20 _AP3 / DDR _MQQ <3      |                         |

| Block Name:<br>Conn. Port:<br>PinName / Cktt<br>64 / 64<br>67 / 67<br>94 / 94<br>101 / 11<br>96 / 96<br>99 / 99<br>118 / 11<br>116 / 11<br>116 / 11<br>117 / 77<br>75 / 75<br>104 / 10<br>38 / 38<br>▼         | to_PCB           VodeName / NetName (Sort By Net)           /DQ6           /DQ7           /DQ8           01 /DQ9           /DQ1           18 /DQ12           11 /DQ13           16 /DQ14           13 /DQ15           /LDQ5           1/DQ5           1/DQ5           1/DQ5           /LDQ5           /LDQ5           16 /DQ14 |                                       |     | Corn. Port:         U20           PinName / CktNodeName / NetName         64 / U20 _AD18 / DDR _MDQ <6>           67 / U20 _AD18 / DDR _MDQ <6>         65           67 / U20 _AD18 / DDR _MDQ <6>         101 / U20 _AP19 / DDR _MDQ <1>           96 / U20 _AP19 / DDR _MDQ <1>>         101 / U20 _AP19 / DDR _MDQ <1>>           99 / U20 _AP19 / DDR _MDQ <1>>         118 / U20 _AP17 / DDR _MDQ <2>           118 / U20 _AP17 / DDR _MDQ <2>         113 / U20 _AP17 / DDR _MDQ <2>           113 / U20 _AP17 / DDR _MQQ <2>         113 / U20 _AP17 / DDR _MQQ <2>           114 / U20 _AP3 / DDR _MQQ <2>         114 / U20 _AP3 / DDR _MQQ <2>           115 / U20 _AP3 / DDR _MQQ <2>         114 / U20 _AP3 / DDR _MQQ <2>           120 _AD21 / DDR _MQQ <2>         113 / U20 _AP3 / DDR _MQQ <2>           13 / U20 _AP3 / DDR _MQQ <2>         104 / U20 _AP3 / DDR _MQQ <2>           13 / U20 _AP3 / DDR _MQQ <2>         104 / U20 _AP3 / DDR _MQQ <2>           138 / U20 _AP3 / DDR _MQQ <3      | V<br>V<br>OK Cancel Apr |

## One Approach is MCP – Model Connection Protocol

- "Connection" refers to a group of subcircuit terminals

- Classifies terminals by signal, power, or ground

- Allows simple description

- Pin name

- Subcircuit terminal name

- Signal name

- Makes it easy to hook one subcircuit to another

- \* [MCP Begin]

- \* [Connection] BGA

- \* [Connection Type]

- \* [Power Nets]

- \* [Ground Nets]

- \* Lumped(38) U20\_A3 GND

- \* [Signal Nets]

- \* 101 U20\_AH9 DDR\_MDQ<17>

- \* 104 U20\_AG9 DDR\_MDQS2

If IBIS doesn't want to use MCP (welcome to it), let's define something better

#### Summary

- Let the "I/O Buffer Information Sheet" be for I/O Buffers!

- Don't dilute its focus by trying to make it a standard for modeling arbitrary interconnect as well

- Today's systems have complex interconnect, which can be modeled with Spice subcircuits

- same with yesterday's systems b.t.w.

- It is a complete waste of time inventing any new interconnect modeling format inside IBIS!

- All that is missing is a standard way to define connectivity between Spice interconnect subcircuits

- This is essentially a mapping table

- We have certainly solved bigger challenges

# cādence®