# IBIS Package Modeling Proposal with [External Circuit]

IBIS Summit, DesignCon, January 31, 2014 Santa Clara, CA

Arpad Muranyi, Mentor Graphics Corporation Ambrish Varma, Cadence Design Systems

cādence

#### **Introduction**

- The existing package modeling features in the IBIS specification are way outdated and desperately need improvements

- Several proposals have been submitted in recent years and are currently being evaluated/discussed in the ATM Task Group

```

BIRD 125.1 Make IBIS-ISS Available for Package Modeling

BIRD 145.3 Cascading IBIS I/O buffers with [External Circuit]s

BIRD 163 Instantiating and Connecting [External Circuit] Package Models with [Circuit Call]

BIRD 164 Allowing Package Models to be defined in [External Circuit]

BIRD 165 Parameter Passing Improvements for [External Circuit]s

BIRD ??? SiSoft's EBD/EMD proposal

BIRD ??? SiSoft's package modeling proposal

```

■ This presentation will focus on BIRDs 163-164 to familiarize the audience with one of the latest (and greatest ②) proposals

#### The basic idea

- The main idea is to make use of the [External Circuit] keyword for package modeling

- [External Circuit] was available for on-die interconnect modeling since its introduction in IBIS v4.1 (January 2004)

- There is practically no difference between an on-die interconnect and a package model, so why not use [External Circuit] for both?

# Why is [External Circuit] not popular?

[External Circuit] existed in the IBIS specification for ten years, yet it hasn't been widely used so far

#### Why?

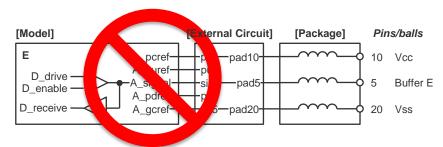

- Currently, [External Circuit] cannot be cascaded with [Model]

- if someone wanted to model an on-die interconnect with [External Circuit]

today, they would also need to use an [External Circuit] model for the buffer

- But buffer modeling in [External Circuit] is a challenging task

- need to use Verilog-A(MS), VHDL-A(MS) or Berkeley-SPICE

- Berkeley-SPICE does not support T-line or S-parameter models

- Consequently, [External Circuit] is not very useful in real life as it stands in the current IBIS specification

#### Major improvements in IBIS v6.0

- IBIS-ISS was added as a new language option to [External Circuit] (and [External Model]) in IBIS v6.0 (September 2013)

- IBIS-ISS offers many useful capabilities which were previously not available

- W-element, S-parameter, etc...

- IBIS v6.0 also introduced parameter passing into [External Circuit] (and [External Model])

#### The last obstacle

- There is nothing in the IBIS specification that prevents [External Circuit] from being used for package modeling, other than a small statement in Table 11 (pg. 90)

- "References enhanced descriptions of structures on the die, including digital and/or analog, active and/or passive circuits"

- The IBIS specification doesn't allow [Model] and [External Circuit] to be cascaded

- most people would like to keep using [Model] for buffers

- but there is a great need for on-die interconnect and improved package modeling in IBIS

- BIRD 145 proposed a method to cascade [Model] with [External Circuit]

- requires a [Model Call] keyword for every single instance of a [Model], making .ibs files potentially very large

#### The purpose of BIRD 165

- BIRD 165 proposes to extend the parameter passing mechanism from [External Circuit] to [Circuit Call]

- same syntax as in IBIS v6.0 for [External Circuit], except it can be placed under [Circuit Call] as well

- This would allow independent parameter values to be passed into each instance of the same [External Circuit]

- It is not directly related to BIRDs 163 and 164, but it improves the flexibility of package and on-die interconnect modeling by allowing independent parameter values to be passed into the different instances of the same IBIS-ISS package and on-die interconnect models

#### The purpose of BIRD 164

BIRD 164 proposes to change the statement in Table 11 (pg. 90) so that [External Circuit]s wouldn't be limited to describe only "structures on the die"

#### change:

"References enhanced descriptions of structures on the die, including digital and/or analog, active and/or passive circuits"

#### to:

- "References enhanced descriptions of structures on the die or package including digital and/or analog, active and/or passive circuits"

- In addition, it proposes a subparameter for [External Circuit] to be able mark an [External Circuit] as a package model

- When this subparameter is present, the package model using [External Circuit] will supersede any other package model definition for the component

### The purpose of BIRD 163

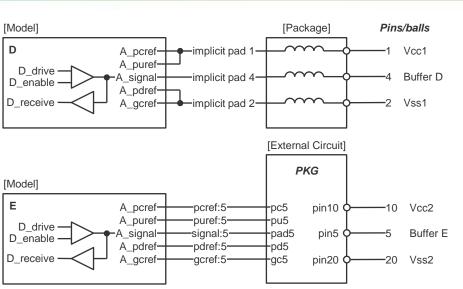

- BIRD 163 deals with instantiating [External Circuit] package models, and proposes new syntax and rules for connecting any [External Circuit] instances to each other or to buffer models described by the [Model] keyword

- Note that the [Model] instantiation from the [Pin] keyword is not changed in this proposal

- Also, nothing is changed for [External Model]s inside [Model]

- BIRD 163 is fairly big because Section 6.3 needs to be modified is numerous places, but the concept in the proposal is relatively simple and straightforward

### How does the proposal work?

```

signal name

model name

R pin

L pin

C pin

Vcc1

POWER

Vss1

GND

Buffer D

MyBufferModel

MyBufferModel

Buffer E

10

Vcc2

POWER

20

Vss2

GND

Instantiating external circuit PKG

[Circuit call]

Port map

pin10 10

| Connection to pin 10

pin5

| Connection to pin 5

Port map

pin20 20

| Connection to pin 20

Port map

| to A pcref on [Model] of pin 5

Port map

ac5

gcref:5

| to A puref on [Model] of pin 5

puref:5

Port map

pd5

signal:5

| to A signal on [Model] of pin 5

Port map

pad5

| to A pdref on [Model] of pin 5

Port map

pu5

pdref:5

gcref:5

| to A gcref on [Model] of pin 5

Port map pc5

[End circuit call]

Defining the external circuit for PKG

[External Circuit]

Language IBIS-ISS

Corner Typ PackageModelFile.sp PKG subcircuitName

Ports pin10 pin5 pin20 gc5 pd5 pad5 pu5 pc5

[End External Circuit]

[Model] MyBufferModel

Model type I/O

```

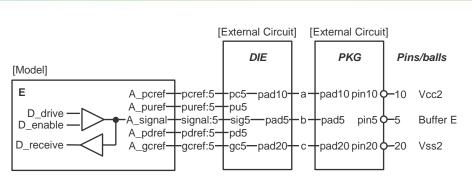

## Adding an on-die interconnect model

```

signal name

model name

[Pin]

R pin

L pin

C pin

Buffer E

MyBufferModel

Vcc2

POWER

Vss2

GND

[Node Declarations] | Must appear before [Circuit Call]

| Instantiating external circuit PKG

[Circuit call] PKG

Port map pin10 10

| Connection to pin 10

pin5 5

| Connection to pin 5

Port map

| Connection to pin 20

pin20 20

Port map

| Connection to explicit pad c

pad20 c

Port map

| Connection to explicit pad b

Port map

pad5 b

| Connection to explicit pad a

Port map pad10 a

[End circuit call]

```

```

Instantiating external circuit DIE

[Circuit call] DIE

| Connection to explicit pad a

Port map pad10 a

Port map pad5 b

| Connection to explicit pad b

pad20 c

| Connection to explicit pad c

Port map

| to A pcref on [Model] of pin 5

gcref:5

Port map

ac5

| to A puref on [Model] of pin 5

puref:5

Port map

pd5

signal:5

| to A signal on [Model] of pin 5

Port map

sig5

| to A pdref on [Model] of pin 5

pu5

pdref:5

Port map

gcref:5

| to A gcref on [Model] of pin 5

Port map pc5

[End circuit call]

Defining the external circuit for PKG

[External Circuit]

Language IBIS-ISS

Corner Typ PackageModelFile.sp PKG subcircuitName

Ports pin10 pin5 pin20 pad20 pad5 pad10

[End External Circuit]

Defining the external circuit for DIE

[External Circuit] DIE

Language IBIS-ISS

Corner Typ PackageModelFile.sp PKG subcircuitName

Ports pad10 pad5 pin20 gc5 pd5 sig5 pu5 pc5

[End External Circuit]

[Model] MyBufferModel

Model type I/O

```

# Thank you

**Questions?**