# **Capacitance Compensation**

Bob Ross IBIS Summit Meeting DesignCon 2009 Santa Clara, California February 5, 2009

bob@teraspeed.com

© 2009 Teraspeed Consulting Group LLC

# **Typical Problems**

- Driver schedule

- Differential buffer

- External capacitance refinement

- Many other presentations either considered loading interactions or appeared to be impacted that interactions

© 2009 Teraspeed Consulting Group LLC

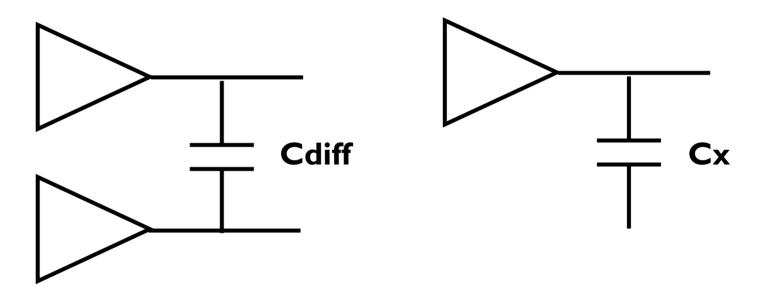

# **Differential Buffer Cdiff or Load Cx**

Cdiff or Cx are extra capacitors that need compensation. They might be non-linear, but first order compensation better than no compensation

CONSULTING

GROUP

© 2009 Teraspeed Consulting Group LLC

# **Possible Solutions**

- Solutions

- Ignore

- Well within the range of expected drivers

- Input is of primary concern

- Adjusting V-T waveforms

- Compensate by "C\_fixture"

- Also (not covered)

- Other presentations

- Or non-linear mathematical de-convolution a whole new topic

# **Other Solutions Not Covered**

- Language solutions

- A. Muranyi,"Pre/de-emphasis Buffer Modeling with IBIS," March 11, 2005, European IBIS Summit – programmable state machine for each V-T combination

- N. Rao, "De-emphasis Buffer Modeling Issues with IBIS", Nov. 14, 2008, Asian IBIS Summit (Japan) – Verilog AMS equation based model

- General problem and investigations several presentations by M. Mirmak and A. Muranyi

# **Compensate by Adjusting V-T**

- B. Ross, "IBIS Die V-T Tables from Part or Board Measurements," Feb. 9, 2004, DesignCon IBIS Summit

- Apply technique for Cx instead of just package or board

- A time-domain approximation solution that would give first order correction for non-linear C

#### **Could use Capacitor Instead of Package** or Board Measurement (50 $\Omega$ to Gnd)

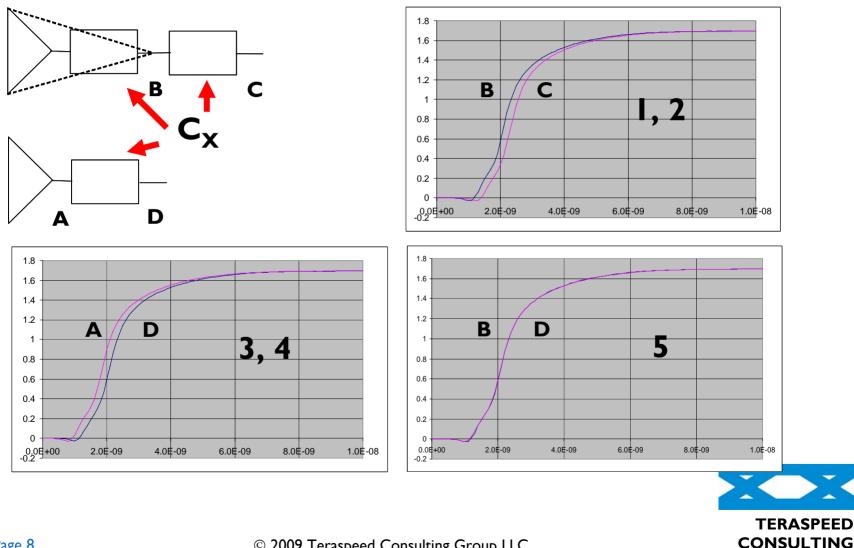

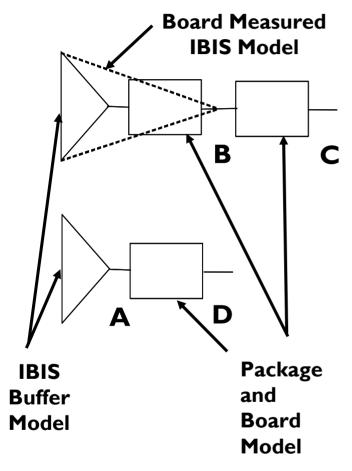

#### Steps for "Delta" Process IBIS Die V-T Tables from Pin/Board V-T Tables

- I. Create IBIS model using MEASURED V-T tables at B

- 2. Simulate **B**, then add package/ board and simulate "delta" **C**

- Use inverse of linear transform of **B** time axis to derive new IBIS model DIE V-T table **A**

- Add package/board to simulate

V-T response at **D**

- 5. Compare **B** and **D**

TERASPEED CONSULTING GROUP

#### Step 3: Inverse Linear Transform to Find V-T table A from B

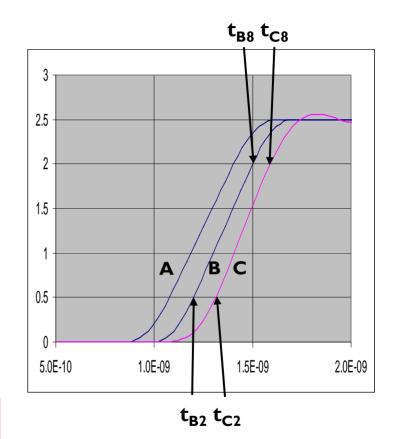

- Find times for 80% and 20% points of B, C: t<sub>B8</sub>, t<sub>B2</sub>, t<sub>C8</sub>, t<sub>C2</sub> (interpolate for accuracy)

- Solve transform for p and q:

t<sub>c</sub> = p \* t<sub>B</sub> + q

(& assume t<sub>B</sub> = p \* t<sub>A</sub> + q)

- Inverse transform time axis  $t_B$ to time axis  $t_A$  using:  $t_A = (t_B - q) / p$

•

$$\mathbf{t}_{\mathbf{A}} = \mathbf{t}_{B8} + (\mathbf{t}_{B} - \mathbf{t}_{C8}) * (\mathbf{t}_{B8} - \mathbf{t}_{B2}) / (\mathbf{t}_{C8} - \mathbf{t}_{C2})$$

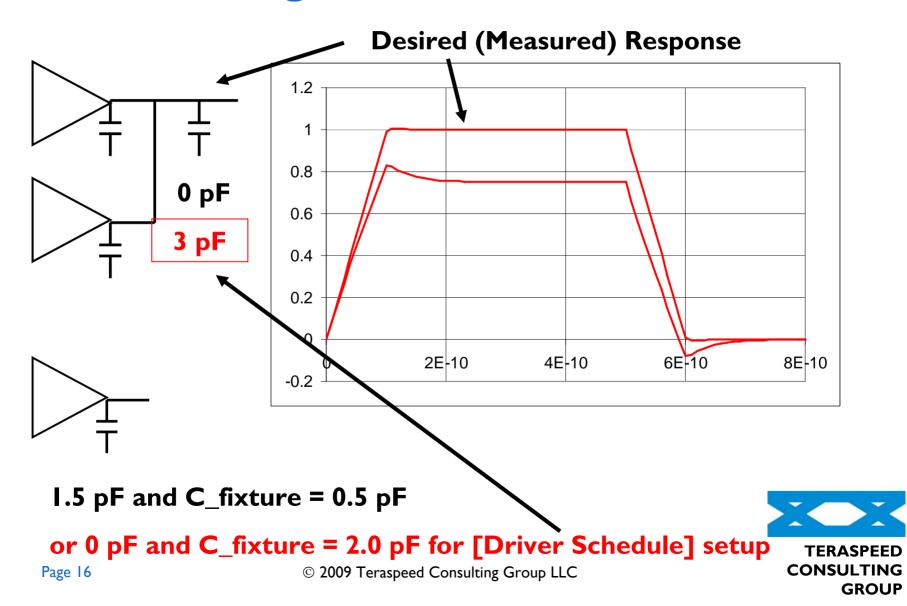

# **Compensate with C\_fixture**

- B. Ross, "C\_comp and Buffer Scaling Observations," Feb. 9, 2006, DesignCon IBIS Summit

- X.F. Chen, "IBIS Algorithm Including Reactive Loads," Sept. 11, 2007, Asian IBIS Summit (China)

- Shows C\_fixture support algorithm

• C\_fixture provides peaking without changing the actual buffer capacitance

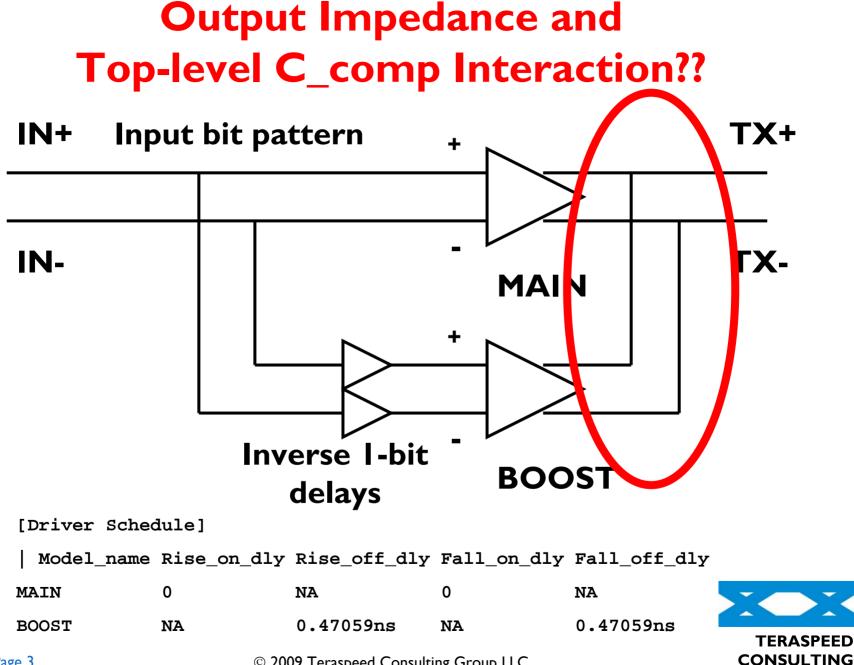

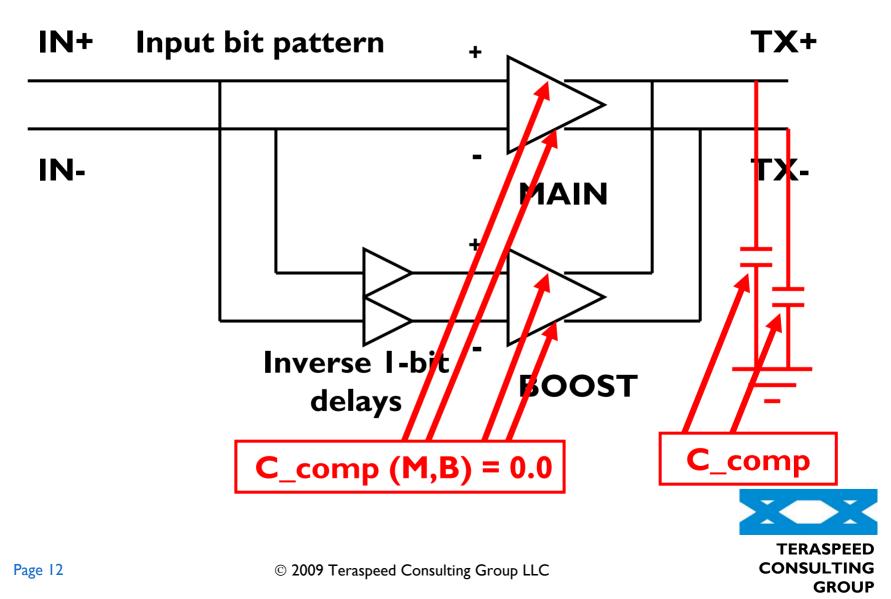

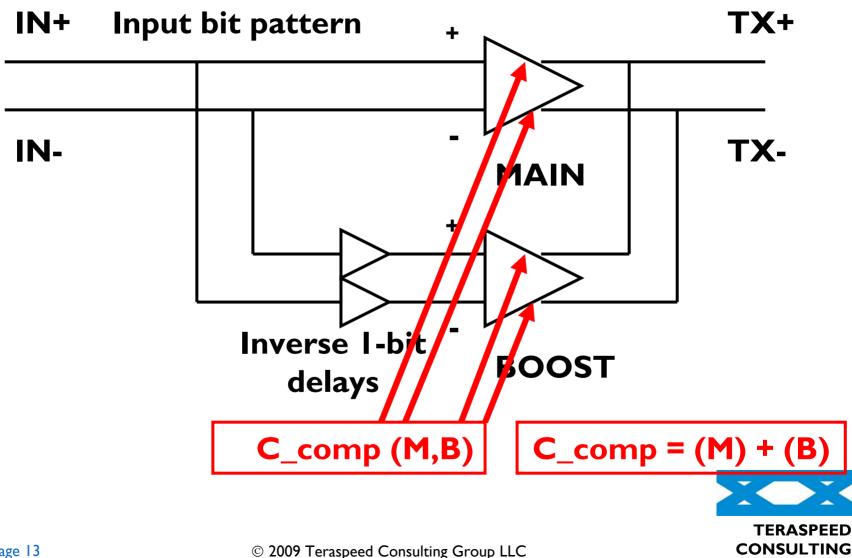

#### IBIS Solution - C\_comp as Load with [Driver Schedule]

#### Macro Model – Buffer Scaling Solution

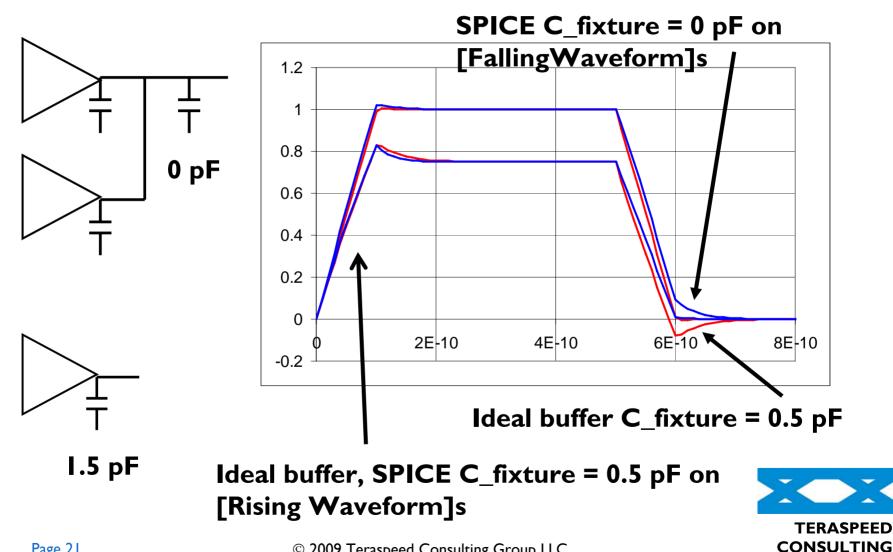

#### Both Approaches Have Limits -Ideal Buffer Test Case

- Summation

- 100 ps ideal ramp

- 25  $\Omega$  ideal buffer (in connected mode)

- $C_{comp} = 3.0 pF$

- Vcc = 1.5 V

- Each one-half scaled

- 50  $\Omega$  ideal buffer

- 100 ps ideal ramp

- 50  $\Omega$  R\_fixture

- 50  $\Omega$  load

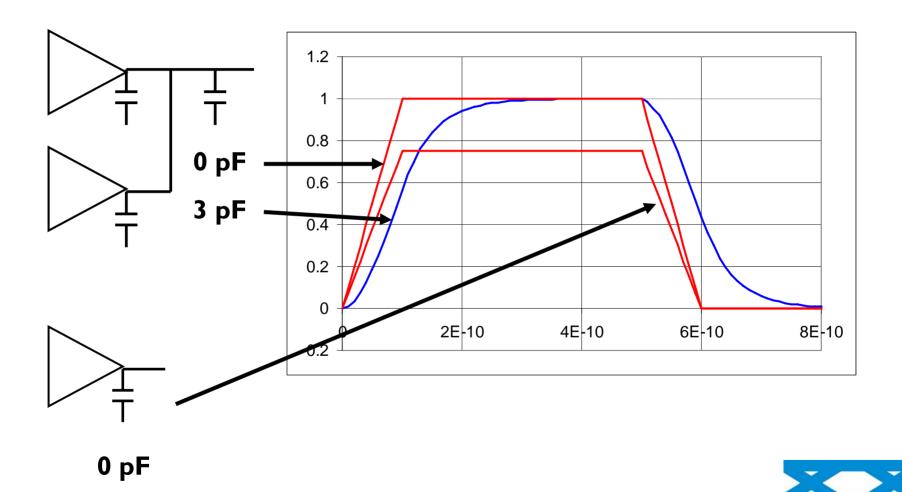

# IBIS [Driver Schedule] Setup with/without C\_comp = 3 pF

TERASPEED CONSULTING

#### C\_fixture Peaking Works in All Cases with Original Scaled Waveforms

#### Proposed Expanded Subset of IBIS Version 2.1

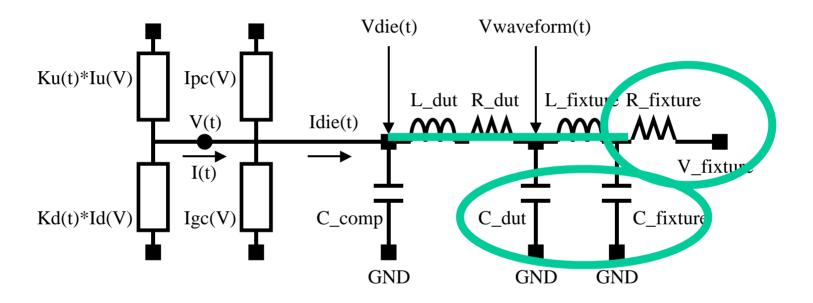

C\_comp\* = C\_comp + C\_dut + C\_fixture

#### K-table Extraction algorithm UNCHANGED

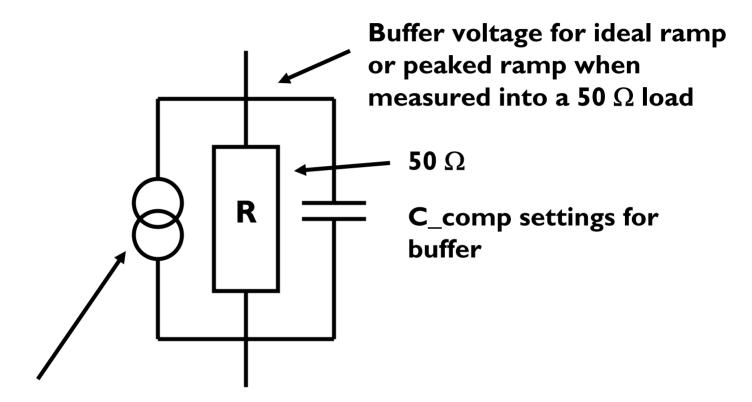

### One Node Norton Equivalent of Ideal 2-waveform Buffer Used for Testing

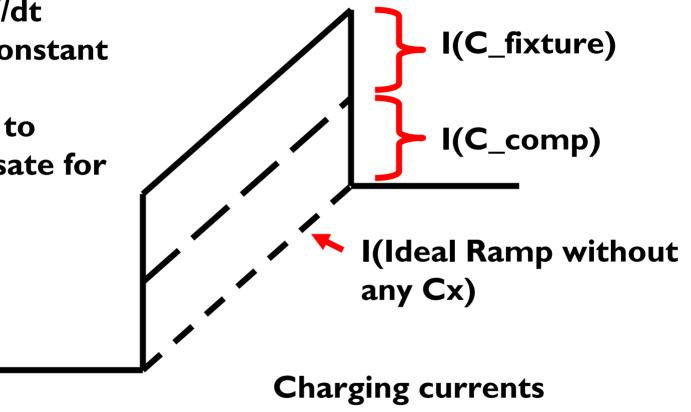

SPICE PWL Current source ramp plus fixed switched charging current for buffer C\_comp and any additional C\_fixture

# **I-Source (Current Source Driver)**

I = C\*dV/dt means constant current addition to compensate for Cx

#### calculated or found by experimentation

# **Comments on Simple Model**

- Current source was one PWL

- Separate PULSE adding together could have been used

- Parameterized input could have been used

- Overshoot/Undershoot implies do NOT clip K tables in IBIS model

- Even C\_comp not fully compensated leading to rolled up responses (charging current starvation)

- So would not work with C\_fixture

- Could work for relatively constant high impedance current mode logic

- Open\_drain, Open\_source buffers non-linear, best done with real buffer for ramp (but constant charging current addition)

### Ideal Test Buffer (Red) Duplicated in SPICE (Blue)

© 2009 Teraspeed Consulting Group LLC

### Conclusions

- Driver needs to compensate for external Cx load

- Change V-T waveform

- Use C\_fixture (but inconsistent industrial support)

- Techniques still keep correct input C\_comp or Cx or Cdiff

- Do NOT clip K-tables can cause IBIS simulation error with correct IBIS model