David Banas, *Sr. Staff Applications Engineer* IBIS Summit DesignCon 2009 Santa Clara, CA February 5, 2009

- → Correlation to Spice models

- Correlation to bench measurements

- Virtex-5<sup>™</sup> model IQS conformance

- New activities

## **Correlation to Spice models**

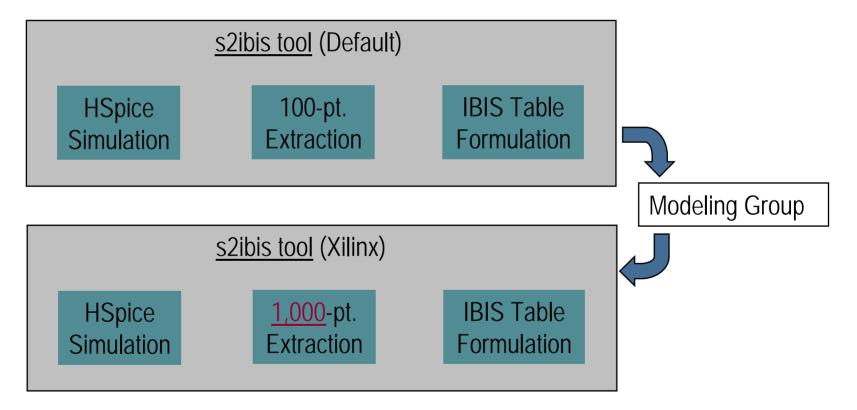

Improved s2ibis extraction procedure

Finer granularity yields smoother curves and better correlation.

# Xilinx IBIS Model Quality Update Correlation to Spice models

- Automation of correlation testing

- do\_sims.pl Perl script that governs the process of fetching, patching, and running the standard I/O Spice models, for a given set of standards, in order to make automated "IBIS vs. Spice" comparison measurements.

- do\_patch Bash shell script that does the actual patching of the Spice decks.

- get\_results.pl Perl script that fetches the results of the Spice simulations run by do\_sims.pl, and reformats them into \*.CSV format for import into MSExcel.

Automation has saved much time and prevented many errors.

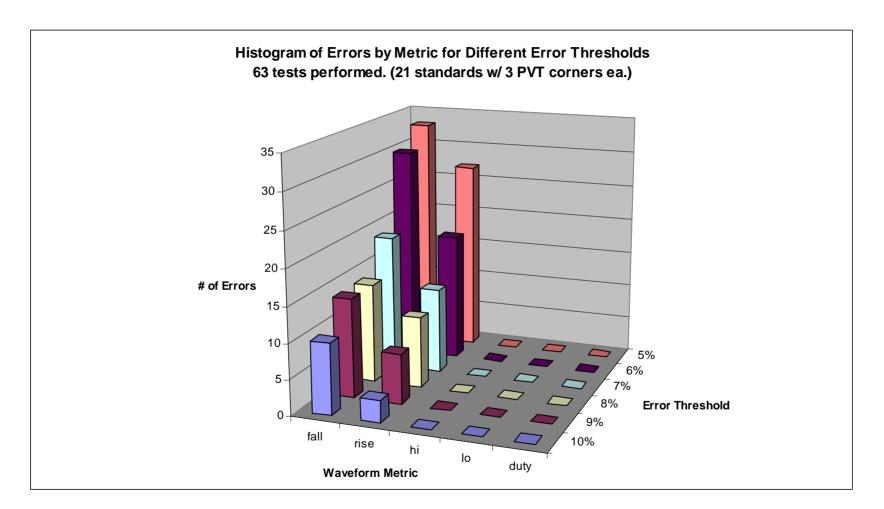

Correlation to Spice models for virtex5.ibs v1.9

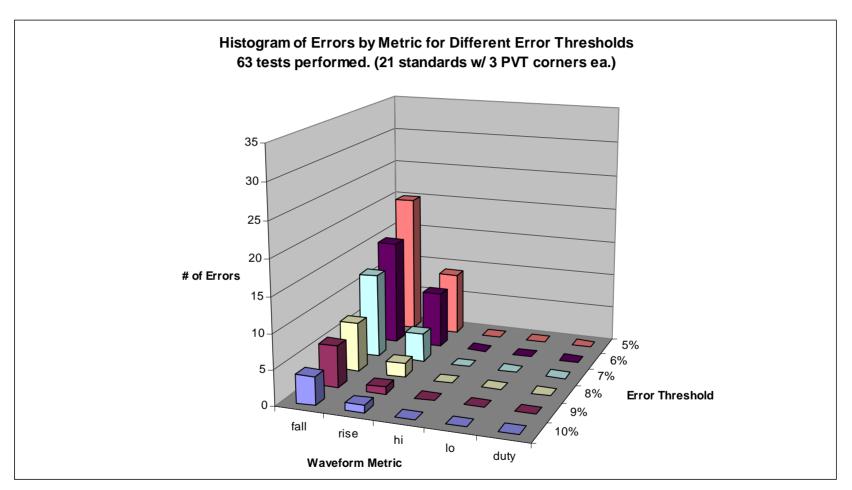

Correlation to Spice models for virtex5.ibs v2.6

Showing improved correlation to Spice models. Questions?

- Correlation to Spice models

- Correlation to bench measurements

- V5 model IQS conformance

- New activities

**Correlation to bench measurements - Methodology**

• IBIS-to-Spice:

• IBIS-to-Bench:

Two fundamentally different methodologies are used.

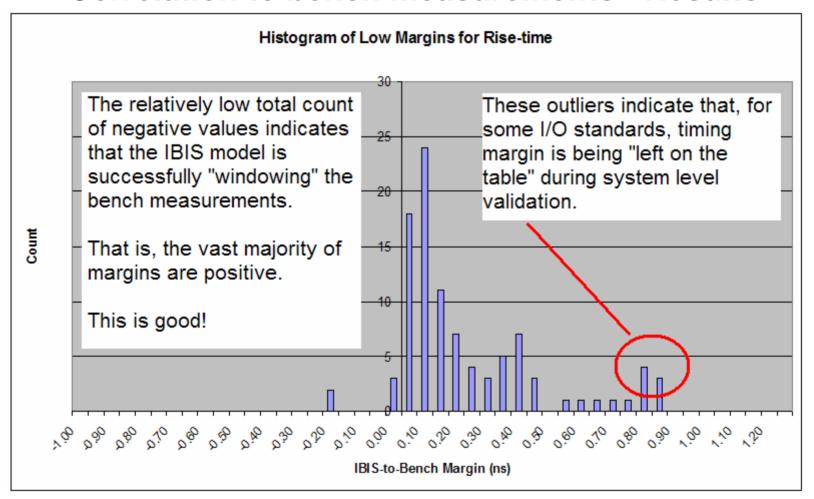

### **Correlation to bench measurements - Results**

With the exception of the large positive outliers, this histogram is ideal.

## **Correlation to bench measurements - Results**

Negative LOW margins indicate that silicon is FASTER than the model.

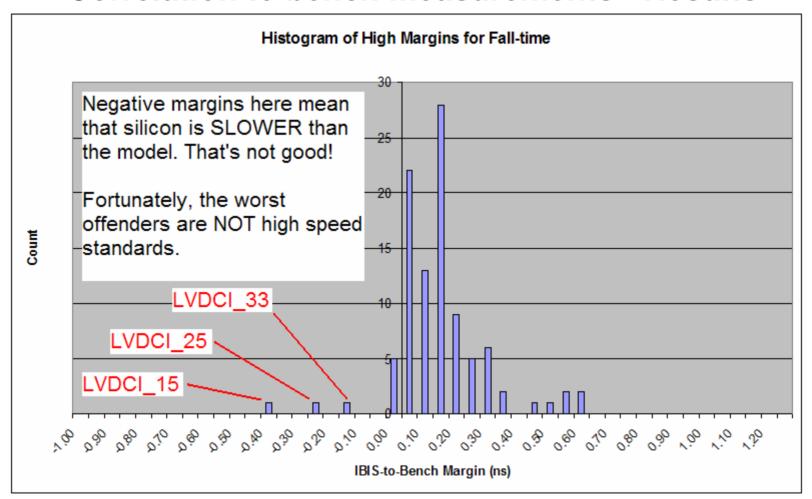

### **Correlation to bench measurements - Results**

Negative HIGH margins indicate that silicon is SLOWER than the model.

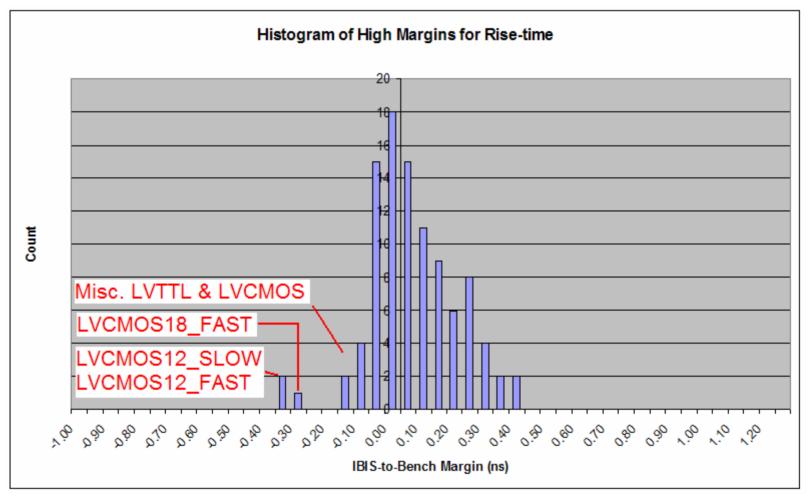

### **Correlation to bench measurements - Results**

Again, none of the offenders are high speed standards.

**Correlation to bench measurements - Results**

Questions?

- Correlation to Spice models

- Correlation to bench measurements

- → V5 model IQS conformance

- New activities

## Xilinx IBIS Model Quality Update **IQS** conformance

- The new standard ("v1.1") defines 5 levels:

- IQ0 No checking at all.

- IQ1 Passes IBISCHK without errors or unexplained warnings.

- IQ2 IQ1 + data for basic simulation checked.

- IQ3 IQ2 + data for timing analysis checked

- IQ4 IQ3 + data for power analysis checked

- and 4 modifiers:

- M correlated against hardware measurements

- S correlated against Spice simulation

- G Has "golden" waveforms.

- X Has exceptions, commented in file.

# Xilinx IBIS Model Quality Update IQS conformance

- According to IQS v1.1ah, our current Virtex-5™

IBIS models file qualifies as <u>IQ3SM</u>:

- IQ3) We pass all requirements, up to and including the new level 3 checks.

- 'S') We have correlated against Spice.

- 'M') We have correlated against bench measurements.

**IQS** conformance

Questions?

- Correlation to Spice models

- Correlation to bench measurements

- V5 model IOS conformance

- → New activities

## New activities – release report automation

Xilinx IBIS models file release report for: virtex5.ibs v2.6

Produced by: /virtex5\_ibis/gen\_report.pl v1.6 (Rel\_2008-07-10-01)

Produced on: Tue Sep 9 12:36:07 PDT 2008

#### **Contents:**

- · IBIS Parser Results

- Spice Correlation Results

- Bench Correlation Results

Tool version/label identified.

File name and version identified.

Hyperlinks to report sections.

#### **IBIS Parser Results:**

Checking virtex5.ibs for IBIS 3.2 Compatibility...

File Passed

IBISCHK4 V4.2.0

Back to top

Results of parser run.

## New activities - release report automation

### Spice Correlation Results:

Produced by: /V5\_IBIS\_Spice\_Correlation/OUTPUTS\_ONLY/SINGLE-ENDED/spice\_tools/get\_results.pl v1.2 (Rel\_2008-07-10-01)

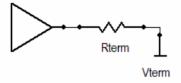

The following effective schematic was used to perform the simulations that generate the results in this section:

Tool version/label identified.

Simulation model shown, for reference.

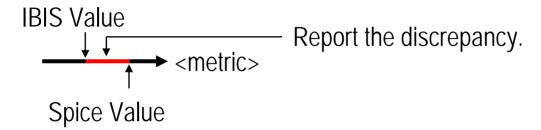

The numbers in the following table give the error in the IBIS model predictions, relative to the Spice model predictions, for certain *features* or *metrics* of the test waveform.

Errors are normalized to the Spice prediction, and expressed as a percentage of that value. In cases where the low settling values were below 1 mV, no meaningful error calculations could be made. These cases are indicated by "(n/a)".

Meaning of tabulated data is explained.

| Standard/Corner            | High Level | Low Level | Rise Time | Fall Time | Duty Cycle |  |  |  |  |  |  |

|----------------------------|------------|-----------|-----------|-----------|------------|--|--|--|--|--|--|

| GTL                        |            |           |           |           |            |  |  |  |  |  |  |

| tt                         | +00.00%    | +00.02%   | -00.80%   | +03.19%   | +00.17%    |  |  |  |  |  |  |

| SS                         | +00.00%    | -00.00%   | -05.97%   | -13.60%   | -00.04%    |  |  |  |  |  |  |

| ff                         | +00.00%    | +00.10%   | -02.87%   | +05.09%   | +00.27%    |  |  |  |  |  |  |

| *** Error reading data *** |            |           |           |           |            |  |  |  |  |  |  |

Per-standard data, with large discrepancies highlighted in red.

Back to top

## New activities - release report automation

#### **Bench Correlation Results**:

$Produced\ by: \ /V5\_IBIS\_Bench\_Correlation/OUTPUTS\_ONLY/SINGLE-ENDED/spice\_tools/get\_results.pl\ v1.2\ (Rel\_2008-07-10-01)$

The following effective schematics were used to perform the simulations that generate the results in this section:

IBIS-to-Bench Correlation Default Topology Vterm TL71 Rterm 17.000 ps **TL43 TL45** R13 C9 50.0 ohms 20.0 K ohms TL49 TL50 TL41 TL42 3.000 ps Simple .850.0 fF 50.0 ohms 25.0 ohms **TL44** 5.000 ps 154.000 ps L5 뎽 50.0 ohms 25.0 ohms R14 10.0 millio. IBIS-to-Bench Correlation Alternate Topology; used for Vterm **TL81** - HSTL\_I{\_12, \_DCI, \_18, \_DCI\_18} - HSTL\_II[\_T]\_DCI[\_18] - HSTL III\* Rterm 50.0 ohms 16.000 ps - HSTL\_IV\_DCI[\_18] Simple SSTL\* TI 7/ **D**27

Simulation models shown, with relevant standards identified.

## New activities – release report automation

The numbers in the following table give the min/max IBIS model predictions, and bench measurements, for 4 waveform *metrics*:

- · High settling level

- · Low settling level

- Rise-time

- Fall-time

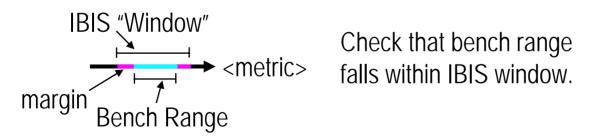

Additionally, the *margins* between the IBIS model predictions and the bench measurements are also given. A positive margin indicates that the IBIS model prediction successfully encompassed the bench measurements, while a negative margin indicates that the bench measurements fell outside the IBIS *window.*

Finally, where available in the bench data, the predictions of the IBIS model, when run in HyperLynx, are compared to those, when run in HSpice. This provides some check on how differently the IBIS models behave when interpreted by two different IBIS simulators (i.e. – HyperLynx and HSpice's  $\mathcal{B}$  element). The errors between the two are calculated as:

Error = (HyperLynx - HSpice) / HSpice

Note) voltages in Volts, and times in ns, throughout

| Standard/Metric            | Low<br>Margin            | IBIS<br>Low | Bench<br>Low | Bench<br>High | IBIS<br>High | High<br>Margin | Low<br>Error | High<br>Error |  |  |

|----------------------------|--------------------------|-------------|--------------|---------------|--------------|----------------|--------------|---------------|--|--|

| GTL                        |                          |             |              |               |              |                |              |               |  |  |

| Vol:                       | (-0.039)                 | (+0.191)    | (+0.152)     | (+0.241)      | (+0.314)     | (+0.073)       | (-<br>22.0%) | (-<br>7.3%)   |  |  |

| Voh:                       | No bench data available. |             |              |               |              |                |              |               |  |  |

| Trise:                     | (+0.108)                 | (00.147)    | (00.255)     | (00.282)      | (00.194)     | (-0.088)       | [n/a]        | [n/a]         |  |  |

| Tfall:                     | (+0.199)                 | (00.152)    | (00.351)     | (00.399)      | (00.248)     | (-0.151)       | [n/a]        | [n/a]         |  |  |

| *** Error reading data *** |                          |             |              |               |              |                |              |               |  |  |

Per-standard

Meaning of

tabulated data is

explained.

data, with negative margins highlighted in red.

### End of Report.

Back to top

# Xilinx IBIS Model Quality Update New Activities

Questions?