# IBIS Advanced Technology Modeling Group (IBIS-ATM)\* Status Report

Todd Westerhoff, SiSoft DesignCon IBIS Summit Feb 1, 2007

## **Agenda**

- Updated Group Charter

- Peak Distortion Analysis

- HSpice investigations

- Cadence's Proposal / BIRD

- Circuit vs. Signal Simulation

- DLL / Executables / Encrypted Source, AMS / SystemC / Other Languages

- Terminology Presentations

- Current Status

## **Updated Group Charter**

- Changed name to IBIS Advanced Technology Modeling Group (IBIS-ATM)

- Current goal:

- Define a transmitter/receiver modeling standard for SERDES channel analysis that encompasses equalization and clock recovery

- The solution must:

- Support multiple EDA vendors

- Support multiple IC vendors

- Protect semiconductor vendor IP

- Support combined transmitter/receiver design

- Support design optimization

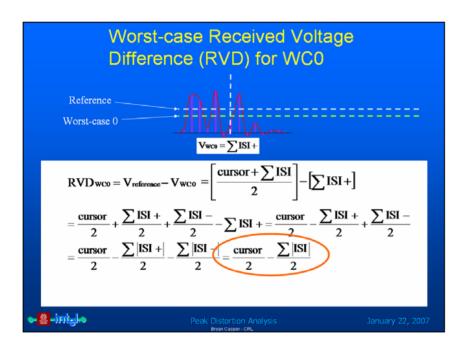

## **Peak Distortion Analysis**

- Analytical method for predicting maximum eye closure based on channel pulse response

- Implemented in VHDL-AMS and demonstrated by Arpad Muranyi of Intel

### Reference presentation:

http://download.intel.com/education/highered/signal/ELC T865/Class2\_15\_16\_Peak\_Distortion\_Analysis.ppt

## **HSpice Investigations**

- Request from Cadence at Asian IBIS Summit to extend [External Model] Spice syntax to allow parameter passing

- Berkeley Spice [currently supported] does not provide this

- Asked Synopsys if they would make HSpice syntax publicly available [de facto standard]

- Synopsys declined, not wanting to restrict future extensions to HSpice's syntax

- Issue currently considered closed

- Open invitation to group to propose specific syntax for parameter passing

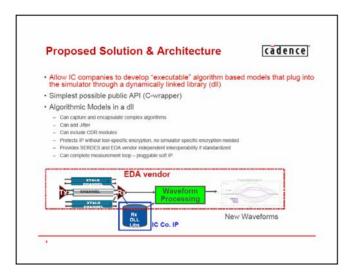

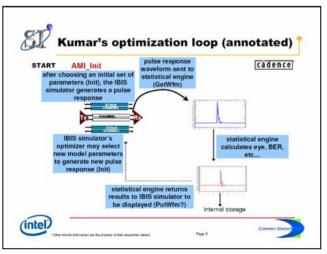

## Cadence's AMI Proposal

- Multiple presentations at:

- http://www.vhdl.org/pub/ibis/macromodel\_wip/

- Ongoing discussions of Cadence's proposal and algorithms therein

- Related discussions on details of channel characterization and modeling

- Cadence presented proposal as draft IBIS BIRD

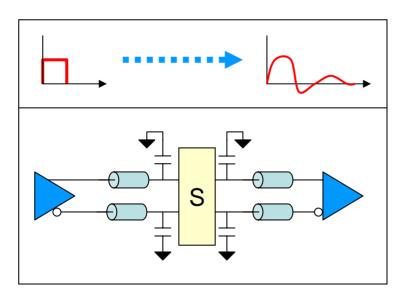

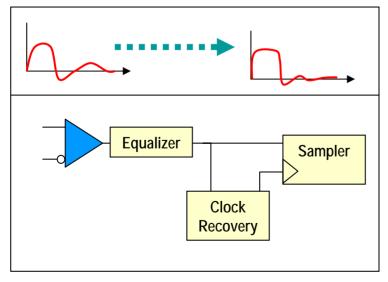

## Circuit Simulation vs. Signal Processing

- Circuit Modeling/Simulation

- Interconnect models

- Network characterization

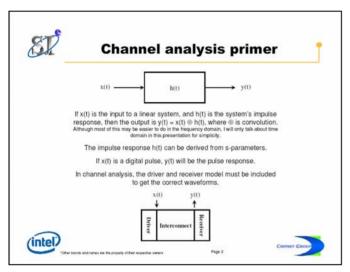

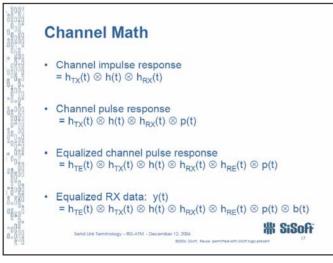

- Impulse Response

- Pulse Response

- Signal Processing Analysis

- Transmitter equalization

- Receiver equalization

- Time-domain waveform generation (convolution)

- Clock recovery

## DLL / Executables / Encrypted Source, AMS / SystemC / Other Languages

- Secondary / deployment issue

- Extensively discussed model development and distribution:

- Tradeoffs between different development languages

- System language trends

- Advantages / disadvantages of different distribution methods (.dll vs. executable vs. encrypted source)

- Strengths and weaknesses of different IP-protection schemes

## **Terminology Presentations**

### Intel

- http://www.vhdl.org/pub/ibis/macromodel\_wip/arc hive/20061024/arpadmuranyi/Channel%20analysi s%20flow%20with%20IBIS/IBIS\_API\_flow.pdf

- TinyURL version:

- http://tinyurl.com/238mdw

### SiSoft

- http://www.vhdl.org/pub/ibis/macromodel\_wip/arc hive/20061212/toddwesterhoff/Serial%20Link%2 0Terminology/serial\_link\_terminology.pdf

- TinyURL version:

- <a href="http://tinyurl.com/yuhxn9">http://tinyurl.com/yuhxn9</a>

### **Current Status**

- Still need better definition of target audience

- Silicon/circuit designers?

- Model developers?

- System designers?

- Network characterization terminology still unclear

- Impulse response vs. pulse response vs. transfer function vs. pole/zero representations

- Cadence's proposal under review

- Ongoing discussions of detailed implications

- SiSoft recommendations for enhancement

- Mechanism to publish model parameters for EDA tool

- Need analysis methodology-independent models

- Still exploring different analytical approaches

## **For More Information**

#### IBIS Advanced Technology Modeling Task Group

The Advanced Technology Modeling Task Group exists to create and promote a system for modeling advanced electronic interfaces, with a current emphasis on SerDes-based designs.

The Task Group began as the Macromodeling Library Task Group, but a new name was agreed to after it became apparent that the group was expending significant effort on several other advanced modeling topics, and joined forces with the <u>IBIS Futures Task Group</u>.

The chair of the Task Group is Arpad Muranyi (arpad.muranyi@intel.com).

- IBIS-ATM / IBIS-Macro Website

- www.eda.org/pub/ibis/macromodel\_wip/

- IBIS-Macro mail reflector

- Mail to: <u>ibis-macro-request@freelists.org</u>

- Subject: subscribe

- IBIS-Macro mail archives

- www.freelists.org/archives/ibis-macro