# HDL and IBIS 4.1 Models in a Functional DDR Memory Interface Analysis

#### Randy Wolff, Micron Technology

©2005 Micron Technology, Inc. All rights reserved. Products are warranted only to meet Micron's production data sheet specifications. Information, products and/or specifications are subject to change without notice. All information is provided on an "AS IS" basis without warranties of any kind. Dates are estimates only. Drawings not to scale. Micron and the Micron logo are trademarks of Micron Technology, Inc. All other trademarks are the property of their respective owners.

#### **Project Definition**

- Analyze a complete DDR memory interface in one simulation

- Simulation should consider:

- Overshoot/Undershoot violations

- Setup and hold timing violations

- Include pattern dependant crosstalk between address, command, control, and data signals

- Slew dependant timing calculations

#### **Project Approach**

- Combine HDL functional models and IBIS I/O models

- HDL code takes care of timing checks

- IBIS model contains basic electrical checks

- How does it all work?

# **IBIS 4.1!**

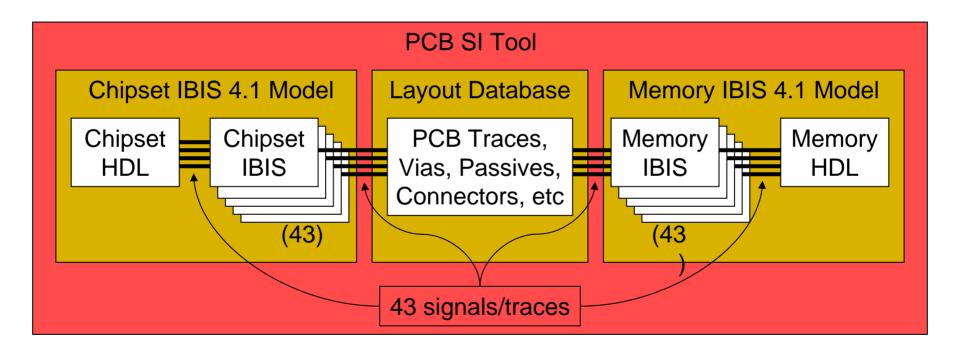

#### **Simulation Diagram**

Connection of HDL functional models and IBIS I/O models to the physical board layout

#### Analysis Details

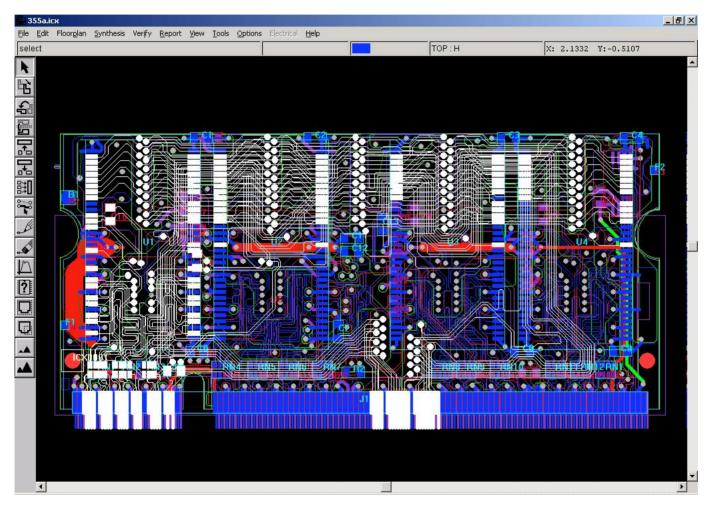

#### • Memory module (simulated traces highlighted in white)

2/1/2006 ©2005 Micron Technology, Inc. All rights reserved.

#### Analysis Details

- Digital code from the chipset testbench generates the system stimulus

- Random address and data pattern generators ensure realistic stimulus patterns for the Write cycle

- Memory responds to chipset commands, thus automating Read cycle data patterns

- Single simulation completes a Read and Write Cycle multiple cycles can be run to simulate realistic bus utilization

- HDL models contain timing checks

- Timing violations caused by PCB effects are flagged

#### C:\WINDOWS\system32\cmd.exe

Warning:tRP violation during Activate Bank 0 Iteration: 2 in: Y\_J1\_MT46V64M16\_0.STATE\_REGISTER Time: 147.849.999 fs MT46V64M16(BEHAVE) Warning:tRFC violation during Activate Iteration: 2 in: Y\_J1\_MT46V64M16\_0.STATE\_REGISTER · Time: 147.849.999 fs MT46U64M16(BEHAUE) Warning:RAS# Setup time violation -- tIS 147.849.999 fs Iteration: 2 in: Y\_J1\_MT46V64M16\_0.SETUP\_CHECK - MT Time: 46U64M16(BEHAUE) Warning:WE# Setup time violation -- tIS - 147,849,999 fs Iteration: 2 in: Y\_J1\_MT46V64M16\_0.SETUP\_CHECK - MT Time: 46U64M16(BEHAVE) Warning:RAS# Hold time violation -- tIH 148,749.999 fs Iteration: 0 in: Y\_J1\_MT46V64M16\_0.HOLD\_CHECK - MT4 Time: 6V64M16(BEHAVE) Warning:RAS# Setup time violation -- tIS Iteration: 2 in: Y\_J1\_MT46V64M16\_0.SETUP\_CHECK - MT Time: 151.250 ps 46U64M16(BEHAUE) Warning:WE# Setup time violation -- tIS Iteration: 2 in: Y\_J1\_MT46V64M16\_0.SETUP\_CHECK - MT Time: 151,250 ps 46U64M16(BEHAUE) Warning:CAS# Hold time violation -- tIH Iteration: 0 in: Y\_J1\_MT46V64M16\_0.HOLD\_CHECK - MT4 152.150 ns Time: 6V64M16(BEHAVE) Warning:RAS# Hold time violation -- tIH

\_ []

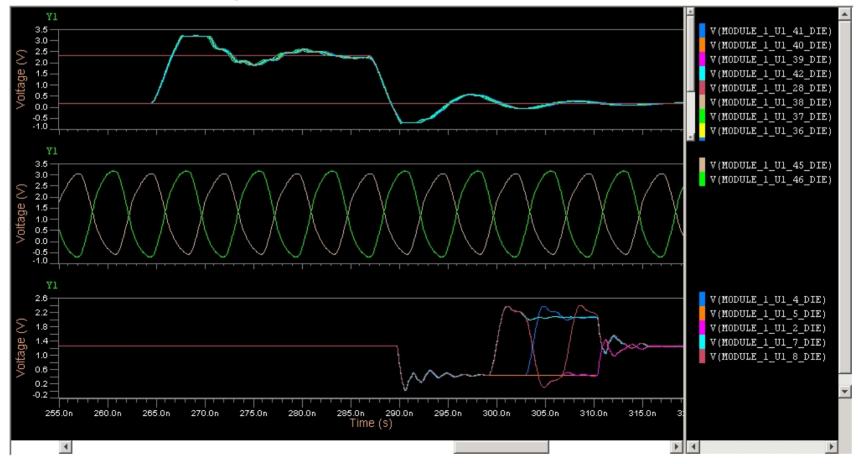

- Analog Address, Clock, and Data signals at memory during a burst write from the chipset

- Simulation easily changed to generate pseudo-random or fixed address and data patterns

M

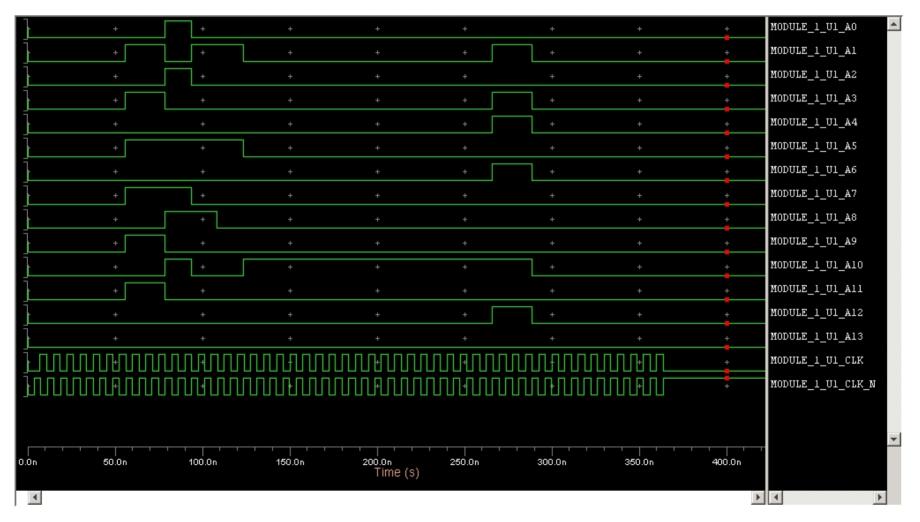

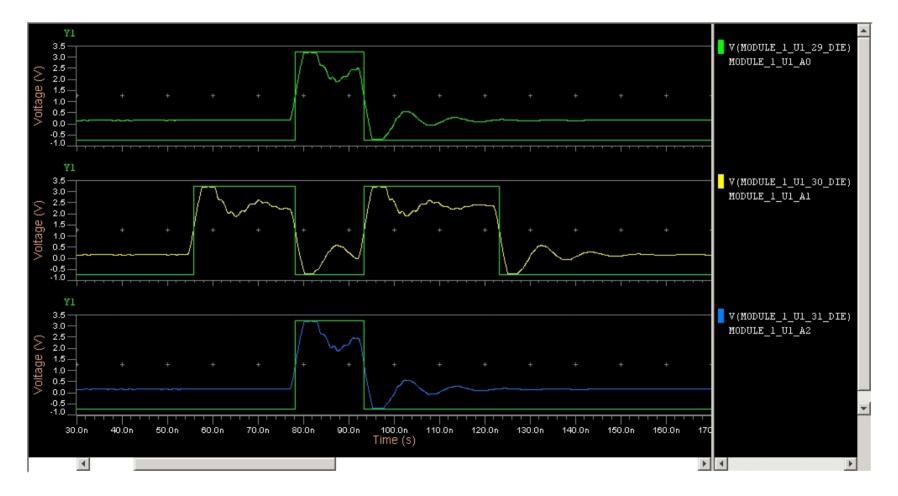

Digital Address and Clock signals at the memory die during a burst write from the chipset

M

- Combined analog and digital Address signals at the memory die during a burst write from the chipset

- Provides a useful visualization of the logical analog equivalent

M

#### **Future Enhancements**

- Exercise all 64 DQ signals in the system (instead of 8)

- Use AMS to analyze slew dependant timing outputting results on separate signal

- Model DDR2 system including ODT effects

- Include S-parameter models to replace PCB physical information for enhanced crosstalk analysis

- IBIS enhancements:

- Instantiating a [Model] in a [Circuit Call] statement

- Corner-specific Parameters passing

### **Project Contributors**

- **Gary Pratt, Mentor Graphics**

- Mark Kniep, Micron Technology lacksquare

- Pavani Jella, Micron Technology lacksquare

- Randy Wolff, Micron Technology