# **IBIS** and Behavioral Modeling

Michael Mirmak

Intel Corporation

Chair, EIA IBIS Open Forum

IBIS Summit Shenzhen, China December 6, 2005 迈克尔.莫马克 英特尔公司 IBIS 委员会主席

亚洲 IBIS 技术研讨会 中国深圳 2005 年 12 月 6 日

## **Legal Disclaimers**

- THIS DOCUMENT AND RELATED MATERIALS AND INFORMATION ARE PROVIDED "AS IS" WITH NO WARRANTIES, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, NON-INFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION, OR SAMPLE. INTEL ASSUMES NO RESPONSIBILITY FOR ANY ERRORS CONTAINED IN THIS DOCUMENT AND HAS NO LIABILITIES OR OBLIGATIONS FOR ANY DAMAGES ARISING FROM OR IN CONNECTION WITH THE USE OF THIS DOCUMENT.

- Performance tests and ratings are measured using specific computer systems and/or components and reflect the approximate performance as measured by those tests. Any difference in system hardware or software design or configuration may affect actual performance.

- Intel may make changes to specifications, product descriptions, dates and plans at any time, without notice.

Page 2

Copyright © 2005, Intel Corporation. All rights reserved.

### What is IBIS?

- IBIS\* (I/O Buffer Information Specification)

- A standard format for expressing I/O buffer electrical behavior plus component pin and package information

- ANSI/EIA\* 656-A, IEC\* 62014

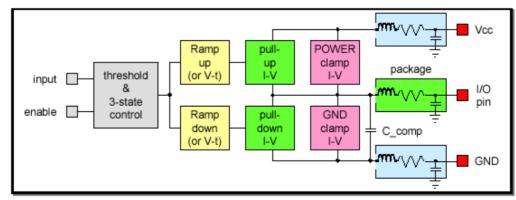

#### Most buffers expressed through

- Current vs. Voltage (I-V tables)

- Voltage vs. Time (V-T tables)

- Buffer capacitance (C\_comp)

### Components include

- Pin assignments and names

- Package information

CHIPSET GROUP

## **Behavioral Modeling**

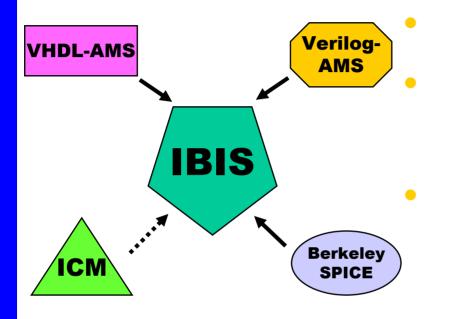

- IBIS is only one type of behavioral model

- Others include:

- ICM\* (IBIS Interconnect Modeling Specification)

- <u>IMIC</u>\* (I/O Model for Integrated Circuits, JEITA\* ED-5302)

- ICEM\* (Integrated Circuit Electrical Model, IEC 62014-3)

- VHDL-AMS\* (IEEE\* 1076.1)

- <u>Verilog-AMS</u>\* (Accelera\*)

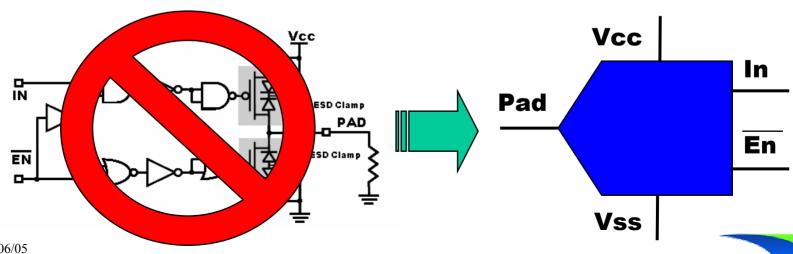

- Behavioral models replace internal design information with observations of electrical ports or terminals

CHIPSET GROUP

\*Other brands and names are the property of their respective owners

Page 4

# An Example

- IBIS, as a behavioral modeling standard, offers

- Protection of internal design information

- Availability under multiple software tools

- Increases in simulation speed over transistor-based models

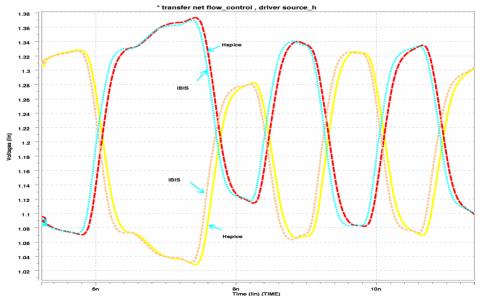

- IBIS behavioral vs. transistor-based models

- For a serial-differential design, IBIS can be 100 times faster!

- Careful model creation preserves accuracy

(time-shifted to show correlation)

Image from SiSoft\*:

IBIS Models at 2.5 GHz and Beyond;

used with permission

Speed quotation from Multi-Gigabit SerDes System Level Analysis...

by Huq/Dodd; used with permission

\*Other brands and names are the property of their respective owners

# The Future of Modeling

### Why behavioral instead of transistor-based models?

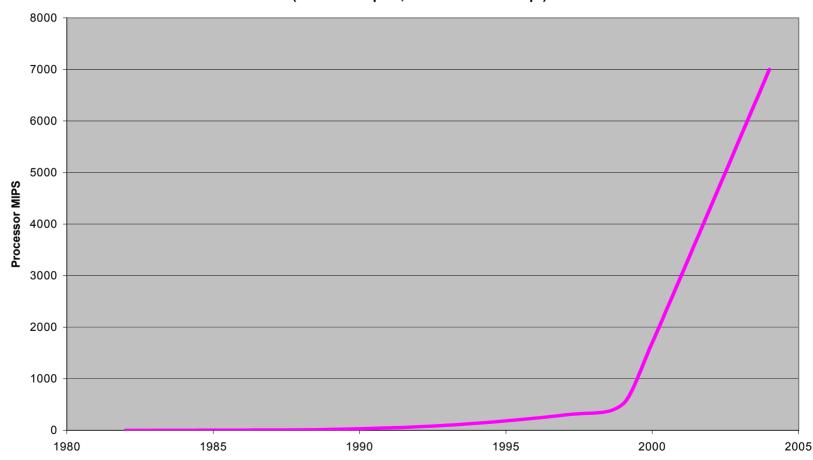

Processor MIPS per Year: 1982-2004 (smoothed plot; source: Intel Corp.)

Page 6

Year

CHIPSET GROUP

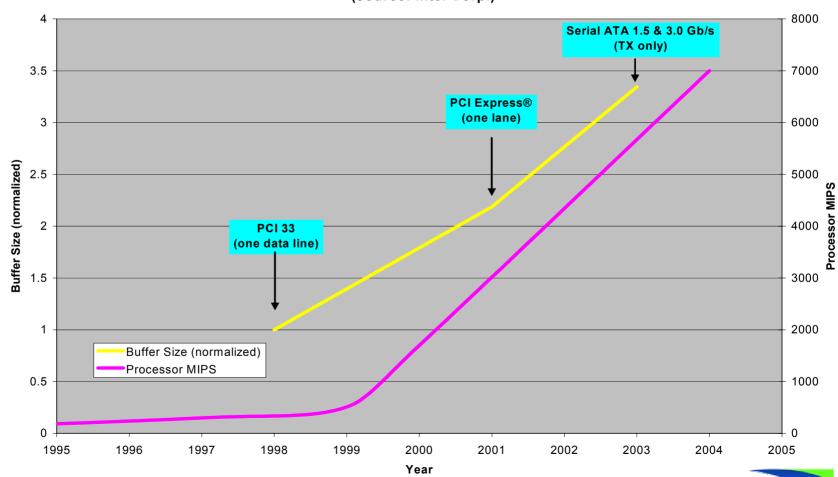

# The Future of Modeling

Buffer complexity is keeping pace with processor power!

I/O Buffer Size and Processor MIPS per Year: 1995-2004 (source: Intel Corp.)

12/06/05 \*Other brands and names are the property of their respective owners

Page 7

CHIPSET GROUP

# **Supporting Future Designs**

#### **Buffers** becoming more complex

Size is <u>tracking processing power</u>

### New designs need more analysis

- Power delivery and switching noise

- Pre-emphasis, active feedback and compensation

#### IBIS expanding to address needs

- New links to VHDL-AMS, Verilog-AMS, Berkeley SPICE\*

- Enable equations within IBIS

- Links to ICM are in development

The industry needs behavioral modeling for today <u>and</u> tomorrow

IBIS provides a standard, unified solution for behavioral buffer modeling

### You Are Invited!

IBIS Welcomes Worldwide Participation!

### **Specifications**

IBIS: <a href="http://www.eda.org/ibis/ver4.1/">http://www.eda.org/ibis/ver4.1/</a>

ICM: http://www.eda.org/ibis/icm\_ver1.1/

#### **Training**

- Including IBIS history and tutorials

- http://www.eda.org/ibis/training/

#### **IBIS Cookbook**

- Features explained plainly

- http://www.eda.org/ibis/cookbook/

#### **Task Groups**

- Futures, Macromodel Library, Quality

- Free Model Review service!

http://www.eigroup.org/ibis/ http://www.eda.org/ibis/

CHIPSET GROUP

IBIS appreciates your input and support!

### **BACKUP**

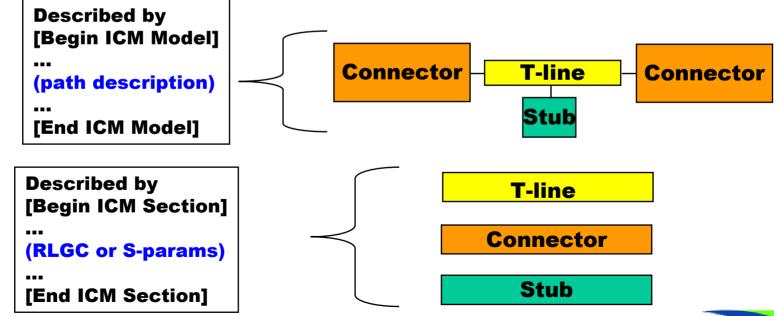

# A Related Specification: ICM

- ICM = IBIS Interconnect Modeling Specification

- Standard text format for interconnect modeling data

- "Interconnect" can be connector, cable, PCB traces or even an IC package

- Defines structure as path between "sections"

- Defines the electrical data for each section