IBIS Summit at 2020 IEEE Virtual Symposium on EMC+SIPI

# Standard Power Integrity Model (SPIM) and Unified PI Target (UPIT)

Presenter: Kinger Cai, Intel Corp. Contributors: Baolong Li, Ansys Suomin Cui, Cadence Ji Zheng, Aurora System Inc. Zhiping Yang and Songping Wu, Google

**ANSYS**

Google

August 28, 2020

# Presenter

# **Kinger Cai**

Platform Electrical Architect, CCG, Intel Corp. Kinger.Cai@intel.com

Kinger Cai has been driving I+I strategy for Notebook platforms, and strategic PI design tool evolution in Client Computing Group. Kinger was awarded Ph. D by Shanghai Jiao Tong University in 2001, and MBA degree by W.P. Carey business school in 2008. Kinger works in signal & power integrity domains for 20+ years. Kinger published 30+ papers and holds 7 granted patents.

# Agenda

- Industry Platform PI Design Challenges

- Platform PI design Architecture Standardization

- FastPI Platform PI design Framework

- SPIM Standard Power Integrity Model

- UPIT- Unified PI design Target

- SPIM with UPIT in FastPI Status Update

- IBIS BIRD Draft Example

- Call to Actions

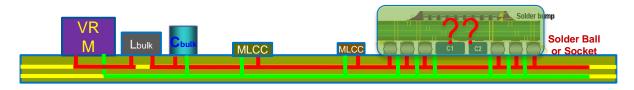

# Platform PI design: Beyond Conventional Methodology

- More flexibility, besides copy exactly from reference design with platform design guideline

- Effective platform PDN optimization, more than what-if simulation

- Efficient platform PI design review and sign-off process

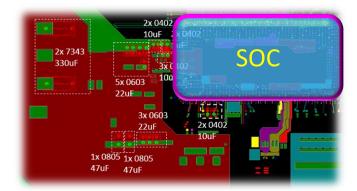

|           | 8L-T3-DS (SD  | ) BOM              |  |

|-----------|---------------|--------------------|--|

|           | Primary (TSC) | Secondary<br>(BSC) |  |

| VCCin     | 2x 7343-330uF | 4x 0402 1uF        |  |

|           | 3x 0805-47uF  |                    |  |

|           | 10x 0603-22uF |                    |  |

|           | 2x 0402-10uF  |                    |  |

|           |               |                    |  |

| VCCin_Aux | 2x 7343-220uF | 12x0402 -10uF      |  |

|           | 13x0402-10uF  |                    |  |

|           | 2x0603 -22uF  |                    |  |

| VDDQ      |               | 6x0402-1uF         |  |

|           | 2x0603-22uF   | 2x0402-10uF        |  |

|           | 1x0603 (PH)   | 3x0402 (PH)        |  |

|           |               |                    |  |

# Platform PI design: Collateral, Architecture and Tools

- > PI design collateral: Chip vendors to platforms designers

- Minimal and standardized

- ✓ Sufficient, while IP protected

- ✓ Flexibility, while accuracy guaranteed

- PI design Architecture, Framework and Tool

- ✓ Standard architecture

- ✓ Flexible framework

- ✓ Efficient tool

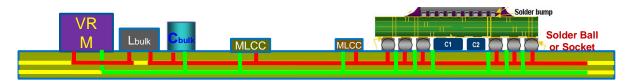

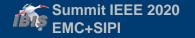

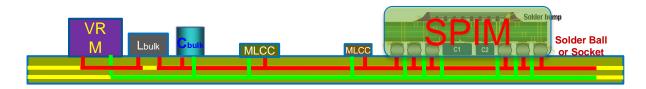

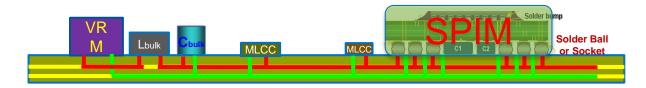

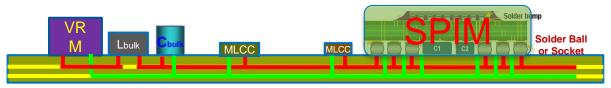

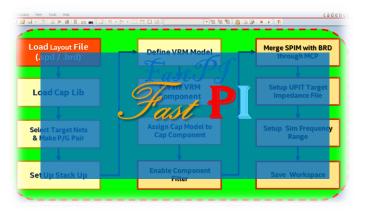

# Platform PI design: FastPI with SPIM and UPIT

- SPIM: Standardized PI Model, for each power rail in SoC/PKG, to customers

- UPIT: Unified PI design Target, an impedance target for each power rail

- FastPI: Platform PI design standard, to integrate with industry leading EDA

FastPI supports chip suppliers, EDA vendors and platform designers, with SPIM and UPIT.

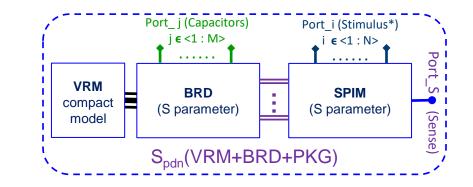

# Platform PI Design: SPIM- Standard Power Integrity Model

- SPIM: Standardized PI Model, for each power rail in SoC/PKG, to customers

- UPIT: Unified PI design Target, an impedance target for each power rail

- FastPI: Platform PI design standard, to integrate with industry leading EDA

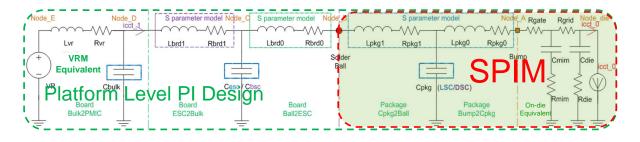

### Platform PI Design: SPIM with UPIT (Unified PI Target)

### SPIM- Standardized Power Integrity Model

#### Standardized PI model

- S parameter, BGA/pin to bump, and Caps

- Weighted/normalized AC source

- Impedance target, at observation port

- Pin(/BGA) awareness

#### • Usage model

- Directly merged as a virtual PKG database, with physical BRD database

- Backwards compatible to SPICE simulator

- IP information protection

#### Development

- Promote as industry standard

- Adopted by major EDA tools

- Scalable UPIT included

#### SPIM for platform PI design, while IBIS for platform SI design.

### FastPI PI Design Target Definition

- Impedance at Sense Port\_S

- −  $[S_{pdn}]$  →  $[Z_{pdn}]$ , in FastPI

- $\ [V] = [Z_{pdn}][I]$

- $[V] = [v_1, v_2, ..., v_{N_r} v_S]^T$

- $[I] = [w_1, w_2, ..., w_N, 0]^{\tau}$

- $-\sum_{i=1}^{i=N}w_i=1$  , weighted normalization

- $Z_{S} = V_{S} = \sum_{i=1}^{i=N+1} (Z_{pdn(N+1),i} * w_{i})$

- $\ \mathsf{Z}_{\mathsf{S}} = \sum_{i=1}^{i=N} (Z_{pdn(_{N} + _{1})_{,i}} * w_{i})$

#### Impedance target is generally defined at sensing/feedback port.

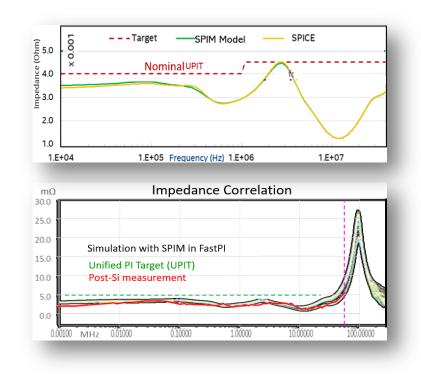

# UPIT - Unified Power Integrity (design) Target

- Extended to cover PD

- Conventionally PI covers >1MHz

- Traditionally PD target defined in TD

- Unified PD Target in FD

- Expanded to IO Power rails

- Started for computing rails

- Expanded as Z target, to IO power rails

- Extrapolated from time domain

- Correlation for UPIT

- Correlated in frequency domain

- SPIM vs. conventional SPICE

- Pre-Si simulation vs. Post-Si measurement

#### UPIT with SPIM has been well correlated with conventional SPICE, as well as post-Si measurement.

### Platform PI Design: SPIM with UPIT in FastPI

- SPIM and UPIT has become one of the standard PI collaterals

- FastPI has been fully supported by two leading EDA vendors

- > Proposing to make it 1<sup>st</sup> PI standard in the industry

### IBIS BIRD Draft Example, for SPIM with UPIT included in IBIS

| SPIM 1       | I                           | U1_1        |                    |  |

|--------------|-----------------------------|-------------|--------------------|--|

| SPIM] SPIM   | I-1                         | VCC1        | 2082 2207          |  |

| VCC_Net VCC1 |                             | VSS         | 2179 2180          |  |

| VSS Net VS   |                             |             |                    |  |

| [Port Group] |                             | U1_2        |                    |  |

| A1 1         |                             | VCC1        | 2085 2210          |  |

| _            | B28 B30 D28 D30 A28 A30 B26 | VSS         | 2182 2183          |  |

| VSS          | B31 C31 D26 A26             |             |                    |  |

|              |                             | [SnP Mod    | el] SnP_model_1    |  |

| A1_2         |                             | [Snp File I | -                  |  |

| VCC1         | E26 E28 E30 F28             | Icelake_V   | CC1_PKG.s58p       |  |

| VSS          | F26 F30 F31                 | [END SnF    |                    |  |

|              |                             | -           | -                  |  |

| A1 3         | i                           | [UPIT] UP   | чТ-1               |  |

| VCC1         | G26 G28 J27 J29 K28 K30     | [OB Port]   |                    |  |

| VSS          | F26 F30 G30 K26 K31         | OB_VCC1     |                    |  |

|              |                             | [S1P File   | Name]              |  |

| A1 4         |                             | Icelake_V   | CC1_OB_TargetZ.s1p |  |

| VCC1         | B22 B23 B25 D23 D25 A23 A25 | [END UPI    | T]                 |  |

| VSS          | D22 D26 A22 A26             | -           | -                  |  |

|              |                             | [END SPI    | M]                 |  |

|              |                             | -           | _                  |  |

EMC+SIPI

Summit IEEE 2020

# Call to Action:

- Call to form a platform PI design standardization WG

- Call chip vendors to support FastPI architecture

- Call EDA vendors to support FastPI framework

- Call platform designers to adopt SPIM and UPIT

- Call to submit IBIS BIRD for SPIM with UPIT

# Legal Disclaimer

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at Intel.com, or from the OEM or retailer.

No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at intel.com, or from the OEM or retailer.

All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or visit www.intel.com/design/literature.htm.

Intel, and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

© 2020 Intel Corporation. All rights reserved.

# THANK YOU!

Kinger.cai@intel.com