# **IBIS & ICM Interfacing Options Alternative Proposals**

## **IBIS & ICM**

What interfacing options require new syntax?

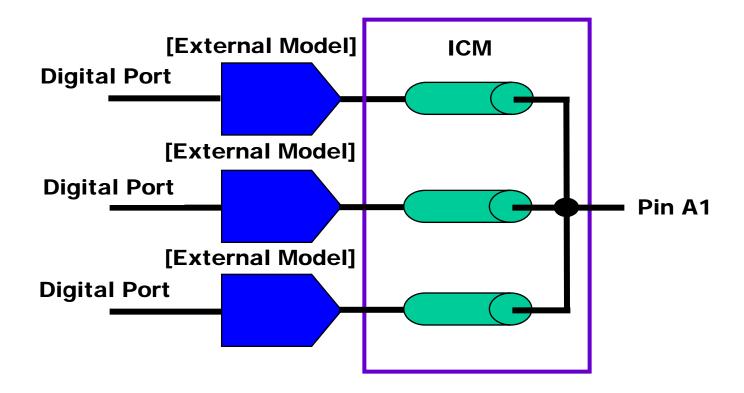

- 1. IBIS 3.2/4.0 + ICM

- Are we willing to limit the ICM models here to singlepath, pad-to-pin?

- 2. IBIS 4.1 + [External Model]

- Should be nearly identical to IBIS 3.2/4.0 treatment

- Again, should single path be kept as a limiter?

- IBIS 4.1 + [External Circuit]

- New syntax required for arbitrary ports

#### Linking ICM to IBIS [E. Circuit]

Use [Node Declarations] to list internal ICM map pin names

[Node Declarations]

|Die pads OR PIN NAMES

A1, A2, A3, A4

buff1, buff2, buff3, buff4

[End Node Declarations]

[ICM Pin Map] Example1\_external

Only downsides: Names must be matched; arbitrary packages not reusable

~

**ICM**

(IIRD8)

Num\_of\_columns = 4

Num\_of\_rows = 1

Pin\_list

|Pin Name

a1 an2

Pin order Row ordered

A1 AD2 A2 AD5 A3 AD7 A4 GND [ICM Pin Map] Example1\_internal

Both sides of ICM

interconnect are mapped

Pin order Row ordered

Num\_of\_columns = 4

Num of rows = 1

Pin\_list

|Pin Name

buff1 AD2

buff2 AD5

buff3 AD7

buff4 GND

**IBIS**

## Items (1) and (2)

- New proposal from Arpad Muranyi

- Concept: <u>assume 3.2 die pad names = 4.1 port names</u>

- [Model] ports are implicitly defined in 4.1

- Just make A\_signal, A\_puref, A\_pdref, etc. accessible for 3.2 models

- Instantiation is by component, pin name (one pin, one model)

- "Dot" syntax for names, tying ports to pins to nodes

- Use explicit names in the ICM file

- Example:

- Component.pin\_name in ICM on pinlist side

- Component.pin\_name.port\_name on die side

- Resembles existing tool approach, to some degree

- Analog port names appear in ICM pin, node lists

- Dangling nodes? OK!

- All connections are explicit (no tree path in this scheme)

- Digital ports disallowed

- Advantages

- Can use current [Package Model] syntax

- Can use ICM file just as we use PKG file

- Permits power, ground path modeling

- Disadvantages

- Do we need ICM/IBIS parser integration?

- [Pin Mapping] could potentially conflict

- Some of this can be cured in IBIS 5.0

### **IBIS & ICM Links**

- Linking ICM ISIS [Model]

- This ald cover [External Model] too

- U nate sues: [Model] ports have no names 1 3.2/4.0

- D\_drive, aren't actually used except in 4.1 exterions

- Power supply annections handled in [Pin Mapping]

- Need way to instant te [Model] separately from [Pir

- Careful! Could enable "loating" [Model]

- otions:

- New IBIS reserved word to separte [Model] from [F

- Also a keyword; example: ICMLINN

- Similar to CIRCUITCALL in [Pin]

- [ICN INK] would explicitly name

- ICM de/pin map, reserved port name, IP name if any

- Extended to CF models/[External officuit]s?

# [ICM Link] Example

CONN A2

**IBIS**

#### Format research two issues

- Multiple [Moder] an now be linked with one ICM

- Stubs and dangling st tures can be included in ICM description without naming/connection in [ICN Link]

- Permits instantiation of mu ble ses of the same [Model]

#### **Uglines**

st bypassed/ We have **J**laced [Pin]

A1 is Assun the only conne on to the outside work

Stubbed model or mo with no direct pip ection

rt

А١

[Er

gnal2

TCM Link]

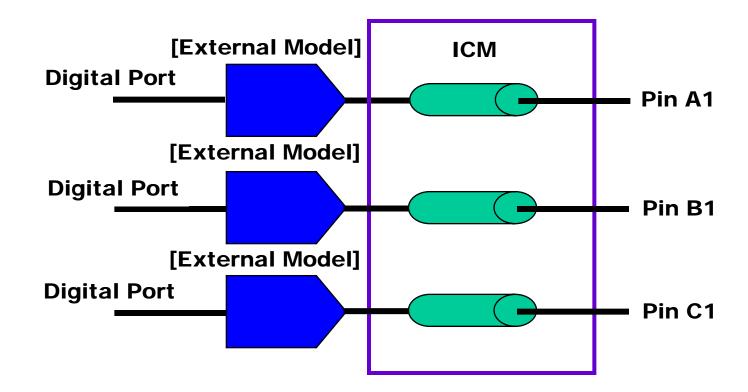

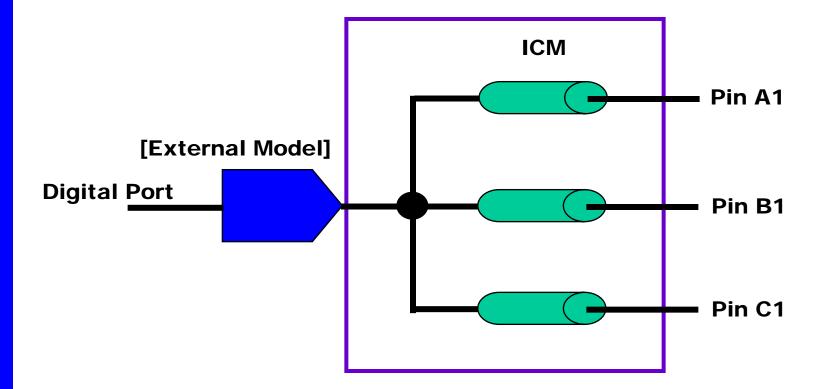

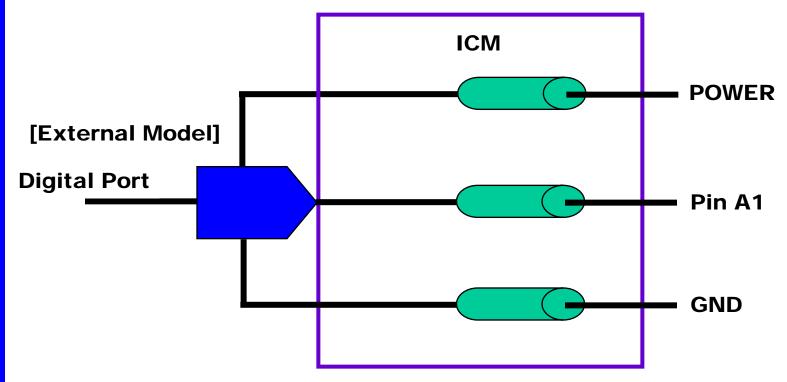

### **Four Cases**

- We must handle these four cases to be complete

- Case 1 ICM expresses coupling

- Case 2 ICM expresses wired-or or "mux"

- Multiple pins, single [Model]

- Case 3 ICM describes coupling & power distribution

- Single model, single signal pin

- Case 4 ICM expresses wired-or or "mux"

- Single pin, multiple [Model]s

## **BACKUP**

# Package Modeling Today

```

[IBIS Verl 3.2

[File name] example.ibs

{...}

Header

[Component] Example_chip

{...}

[Package Model] simple package

L_pin C_pin

[Pin] signal name

model name

R_pin

Pin/Model

io buffer

IO1

IO2

io buffer

assignment

IO3

io buffer

[Model]

io buffer

Model definition

Model type I/O

[Define Package Model] simple package

[Number of Pins] 3

Package Model

[Pin Numbers]

A1 Len=1.2 L=2.0n C=0.5p R=0.05/

definition/assignment

B1 Len=1.2 L=2.0n C=0.5p R=0.05/

C1 Len=1.2 L=2.0n C=0.5p R=0.05/

[End Package Model]

[End]

```

Page 12

http://www-fmec.fm.intel.com/sie

\*Other brands and names are the property of their respective owners

e owners

# Package Modeling Today

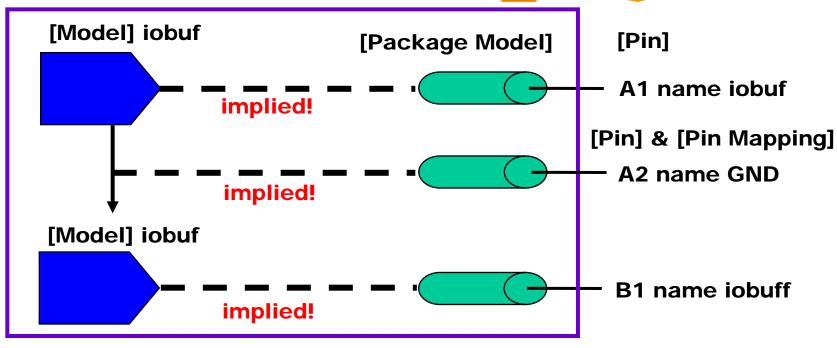

IBIS 3.2 & 4.0 Approach

[Pin Numbers]

- If [Pin] and [Pin Numbers] use the same values...

- Tools assume connections corresponding to values

- Tools infer connections between [Model] and package

- [Pin Mapping] can map supplies to package pins

Page 13

## Package Modeling Today

#### A Few Oddities

Package Pin attachment

"A package stub description starts at the connection to the die and ends at the point at which the package pin interfaces with the board or substrate the IC package is mounted on."

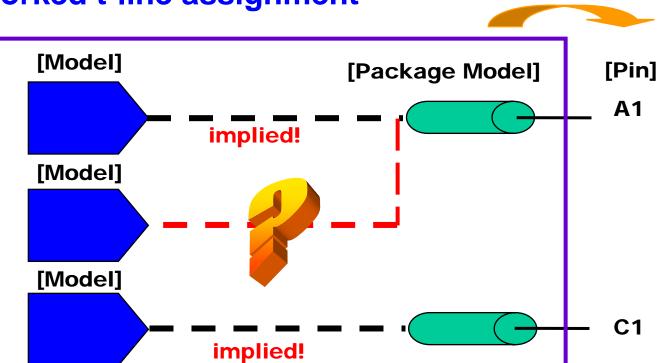

#### Package Pins vs. Fork/Endfork

"The package pin is connected to the last section of a package stub description not surrounded by a Fork/Endfork statements."

Forked t-line assignment

- This structure <u>cannot</u> be described using IBIS 3.2/4.0

- A fork can only end as an unterminated stub

[Pin Numbers]

The General Case... Need explicit link to [Model] instance

**Need explicit link to [Pin] instance**

## **IBIS & ICM**

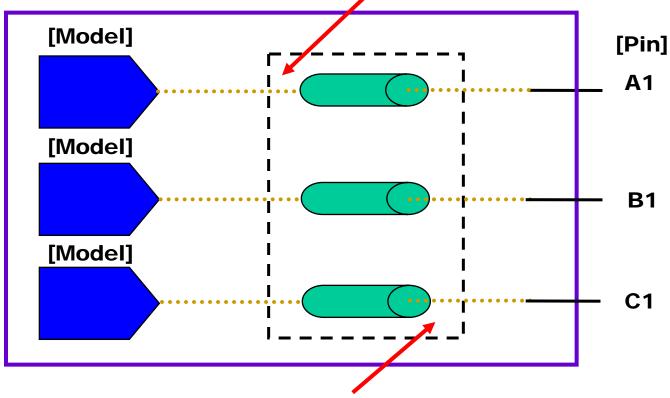

- How can we use ICM to describe packages?

- ICM can describe...

- interconnect RLGC or S-parameter characteristics

- coupling, if present, between interconnect segments

- pin (port) end-points and names

- ICM does not describe...

- connections between [Model], [Pin] and ICM end-points

- Changes Required

- IBIS: need explicit link between [Model] and [Pin]

- ICM can use node/pin map names from [Pin] listing

- [Model] link options listed below

- IBIS: explicit link between [E. Circuit] and [Pin]?

- [Node Declarations]! See below

- ICM: need differentiation between pin maps

- Currently, same pin map may be used for all end-points

- This is fixed in IIRD8 (Ross)