## IBIS Futures Subcommitte Special Meeting

July 8, 2005

Antonio Girardi Mernory Products Group - CAD Group Leader antonio.girardi@st.com

## **Summary**

- IBIS Simultaneous Switching Output Simulations

- Power Network Model Back-annotation

- IBIS "Gate Modulation Effect" Criticality and suggested Solution

- Results of the identified solution obtained by IBIS-VHDL-AMS implementation

- Conclusions

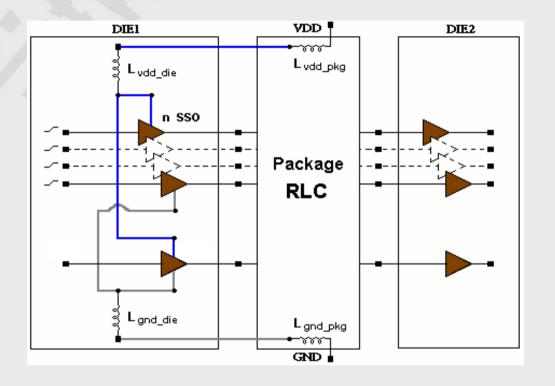

# **IBIS Simultaneous Switching Output Simulations**

The IBIS simultaneous switching outputs simulations are not accurate for two reasons:

1) The power network is not modelled in the standard IBIS model

### 2) Lack of the "Gate Modulation Effect"

IBIS Futures Subcommitte Special Meeting IBIS Simultaneous Switching Output Simulations Criticality Antonio Girardi - STMicroelectronics

**July 8, 2005**

V(DQ\_PAD\_I0)\_1:11 V(DQ\_PAD0)\_1:12

**IBIS**

2.5

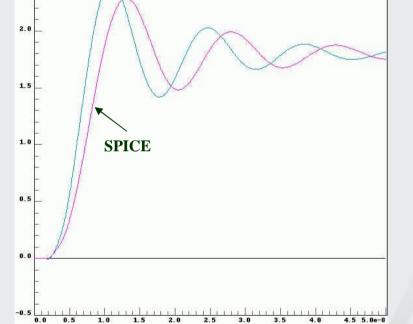

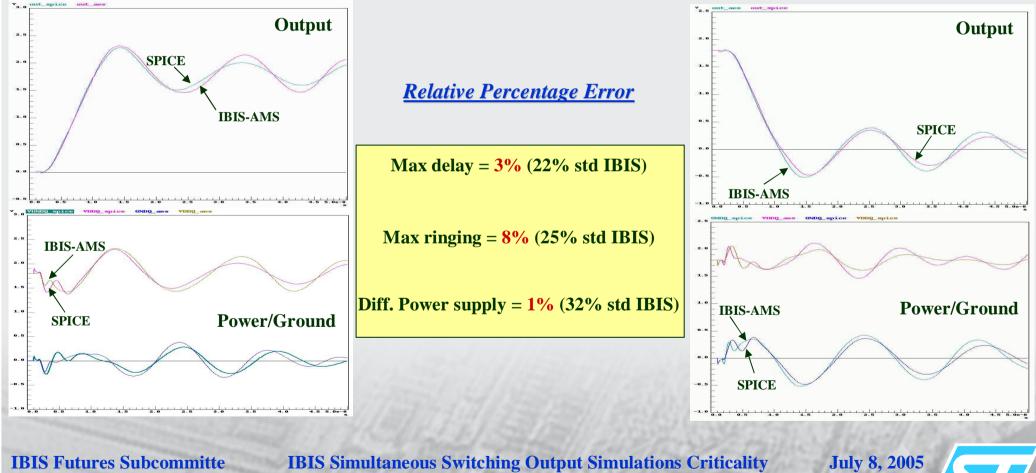

# **Benchmark SPICE vs IBIS(Standard)**

### High mismatching of both output and power/ground signals behaviour

### **SSO – Rise Transition**

#### **SSO – Fall Transition**

**Special Meeting**

**Antonio Girardi - STMicroelectronics**

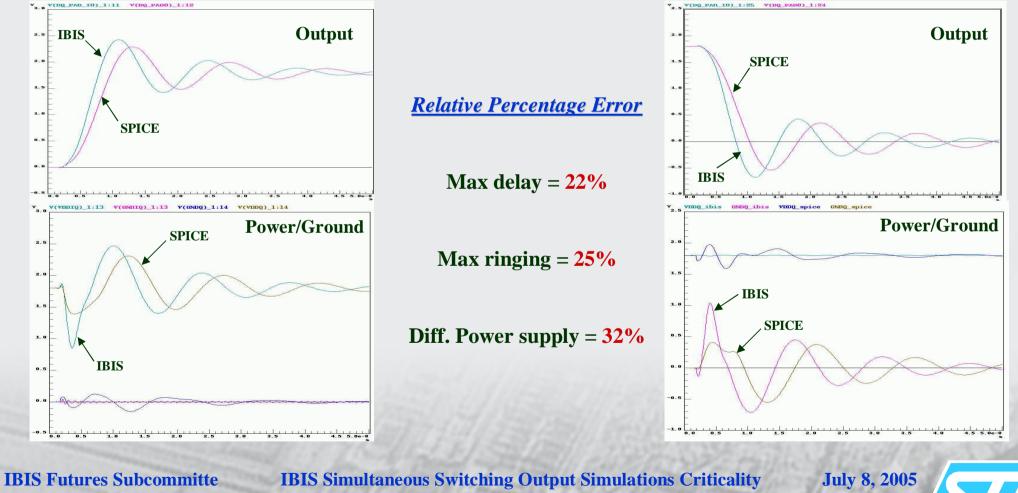

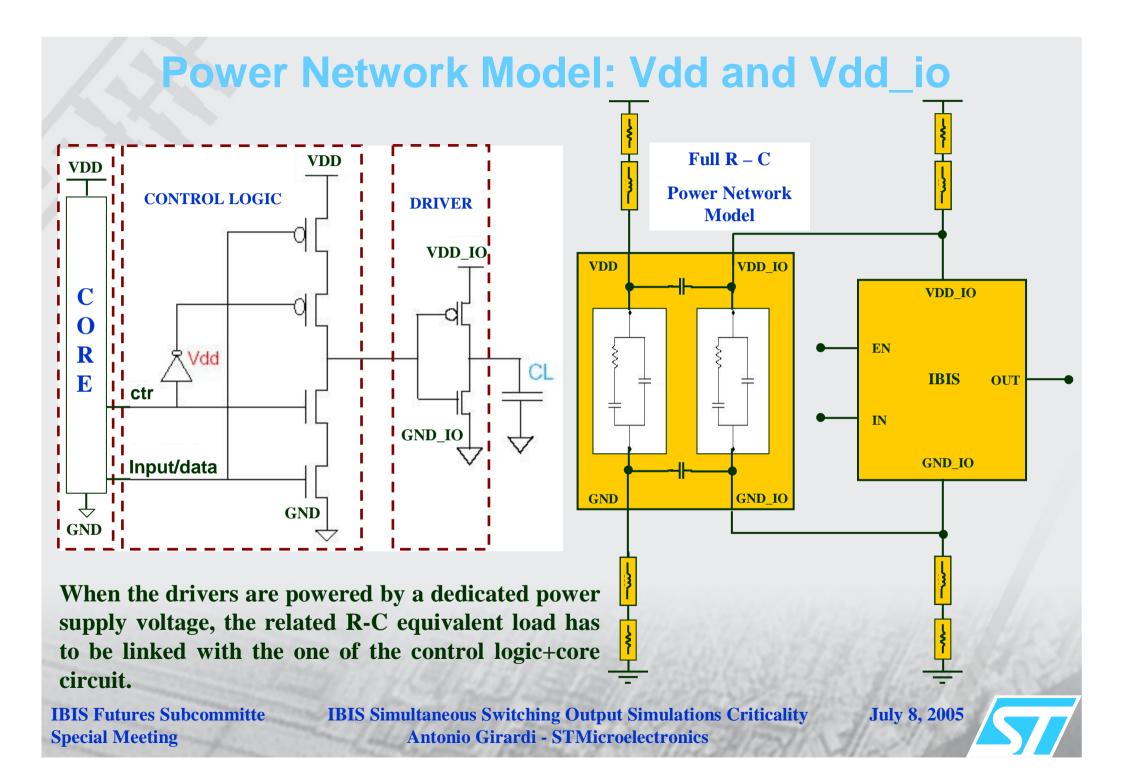

## **Power Network Model**

**IBIS Futures Subcommitte** Special Meeting IBIS Simultaneous Switching Output Simulations Criticality Antonio Girardi - STMicroelectronics

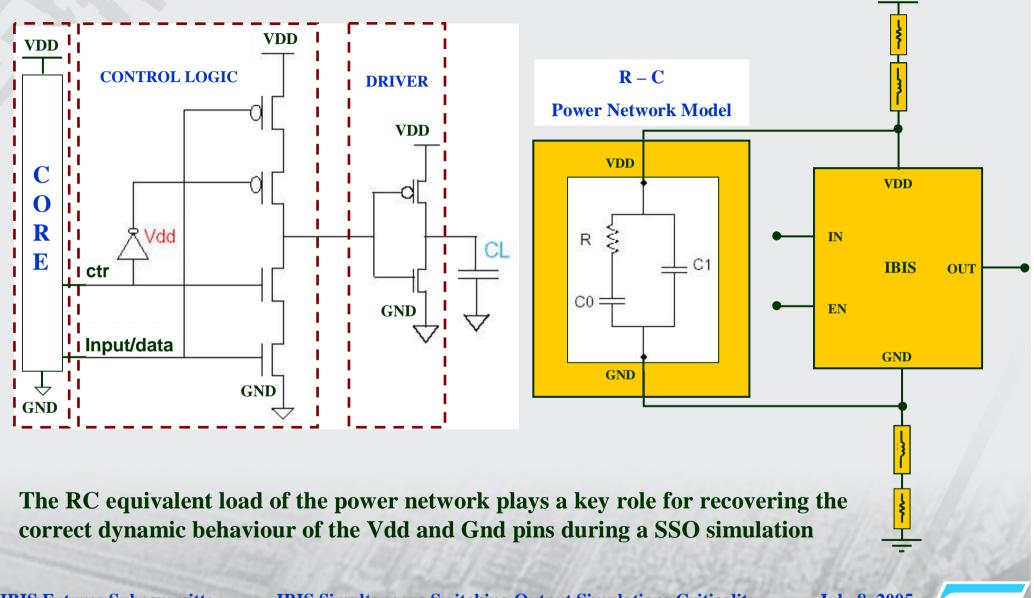

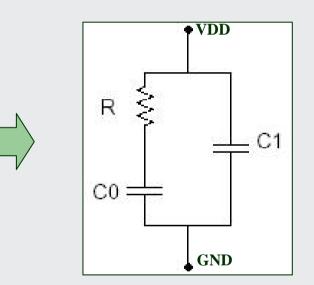

# **Power Network Model Extraction**

### Z(f) impedance between Vdd and Gnd nodes

**R-C equivalent model extracted**

The R-C equivalent model has been extracted by fitting the frequency-dependent impedance Z(f)

**IBIS Futures Subcommitte** Special Meeting IBIS Simultaneous Switching Output Simulations Criticality Antonio Girardi - STMicroelectronics

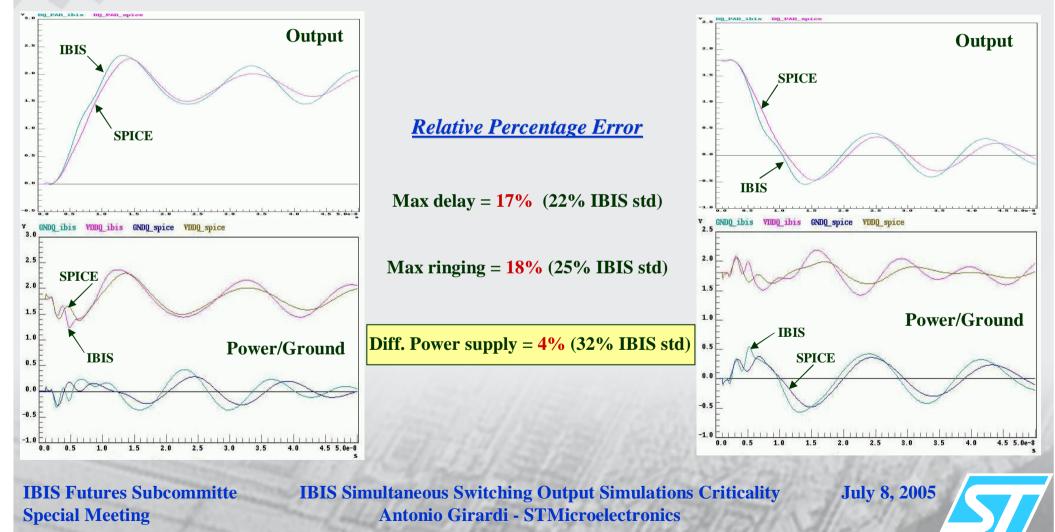

## **Benchmark SPICE vs IBIS(RC Power Model)**

**Good IBISvsSpice matching for power/ground signals by RC model back-annotation**

#### **SSO – Rise Transition**

#### **SSO – Fall Transition**

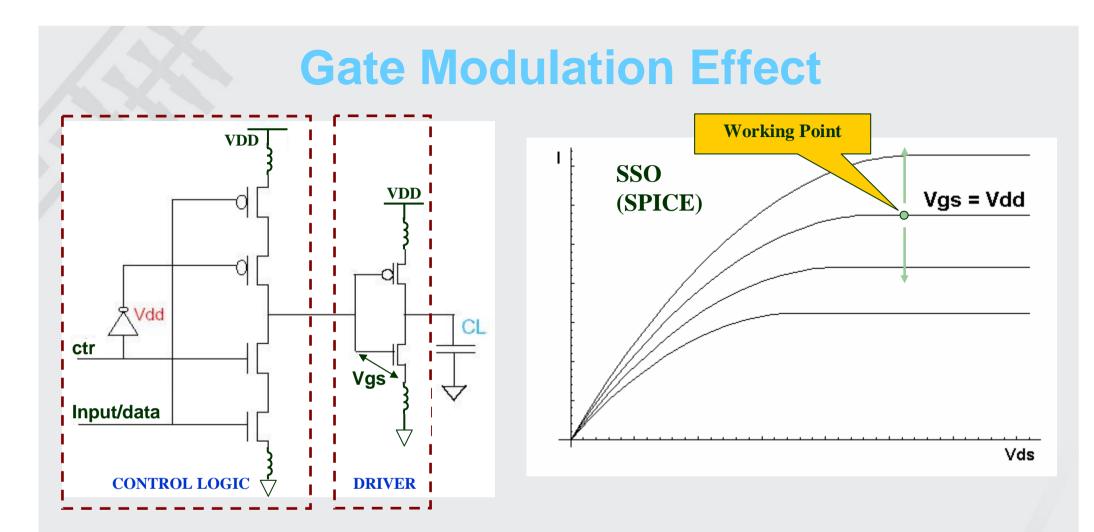

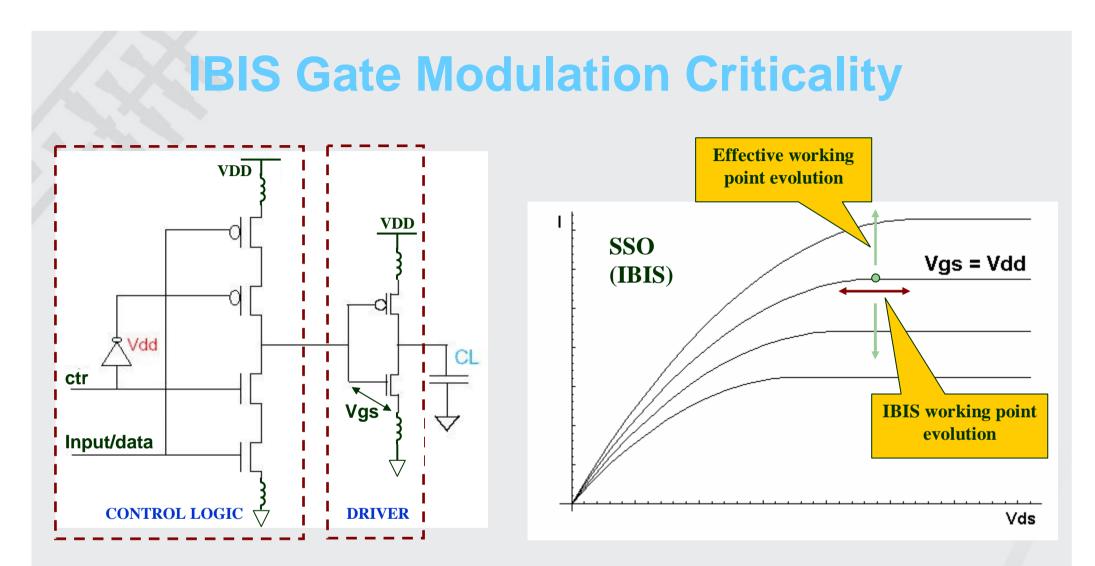

The simultaneous switching noise causes a change of the MOS Vgs voltage, therefore the working point will move along different Vgs characteristics

**IBIS Simultaneous Switching Output Simulations Criticality** Antonio Girardi - STMicroelectronics **July 8, 2005**

IBIS Futures Subcommitte Special Meeting

The IBIS simulation of a simultaneous switching noise does not model correctly the MOS Vgs voltage variation because the working point will move only along the same Vgs =Vdd characteristic. The higher is the bouncing noise, the higher is the mismatching between IBIS and Spice results

IBIS Futures Subcommitte Special Meeting IBIS Simultaneous Switching Output Simulations Criticality Antonio Girardi - STMicroelectronics

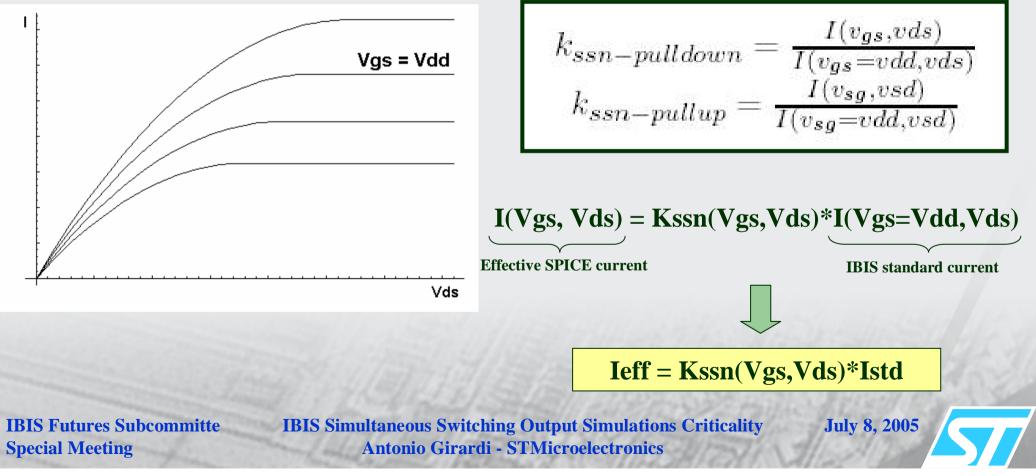

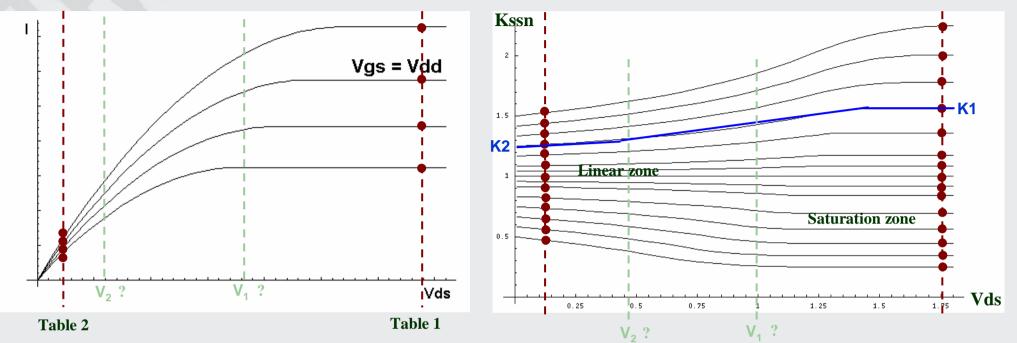

# **Gate Modulation Coefficients**

### **MOS Level 1 equation (threshold voltage 0.6V):**

$$y = \{ [2(v_{gs} - 0.6)x - x^2]u(v_{gs} - x - 0.6) + (v_{gs} - 0.6)^2u(x - v_{gs} + 0.6)\}u(v_{gs} - 0.6) + (v_{gs} - 0.6)^2u(x - v_{gs} + 0.6)\}u(v_{gs} - 0.6)u(x - v_{gs} + 0.6) \}u(v_{gs} - 0.6)u(x - v_{gs} + 0.6)u(x - v_$$

### **MOS Level 1 characteristics:**

### I(Vgs,Vds) Tables Choice Note: K means constant value!!! **IBIS USER** – Table 1 L I(Vgs=K, Vds) Tables How many I(Vgs, Vds=K) or I(Vgs=K, Vds) tables Vas = Vdd are needed? - Table n How do I interpolate them? Vids Is this approach convenient in terms of Table 1 Table n computational effort? I(Vgs, Vds =K) Tables

The effort has been focused to identify an easy implementation of the Kssn coefficients, which also guarantees a good level of accuracy and computational time.

IBIS Futures Subcommitte Special Meeting IBIS Simultaneous Switching Output Simulations Criticality Antonio Girardi - STMicroelectronics

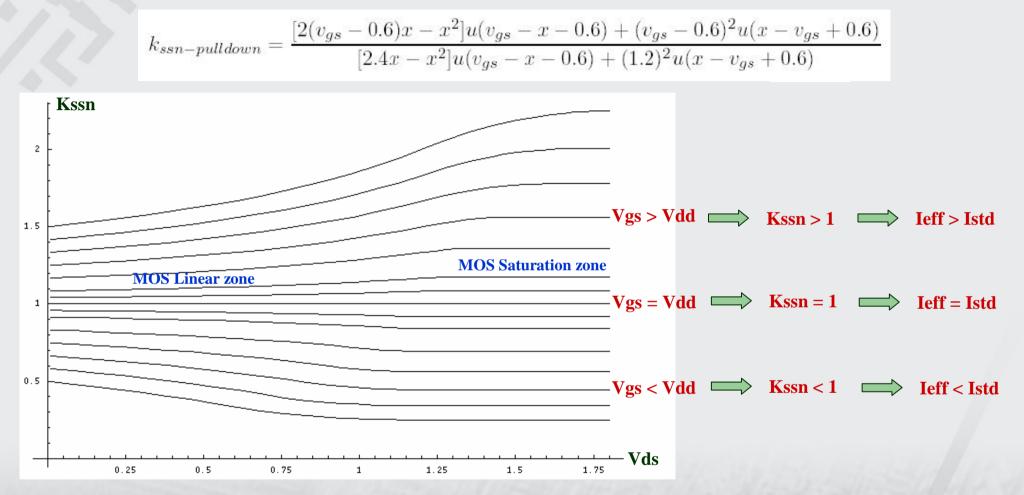

## **Gate Modulation Coefficient Characteristics**

### Gate modulation coefficient equation based on the MOS level 1 equation (Vdd=1.8V):

The Kssn coefficient is indipendent from the Vds voltage in the saturation zone and, approximatively, also in the linear zone, in the case of small Vgs changes. Might be enough one I(Vgs, Vds=k) table?

**Special Meeting**

**IBIS Futures Subcommitte IBIS Simultaneous Switching Output Simulations Criticality** Antonio Girardi - STMicroelectronics

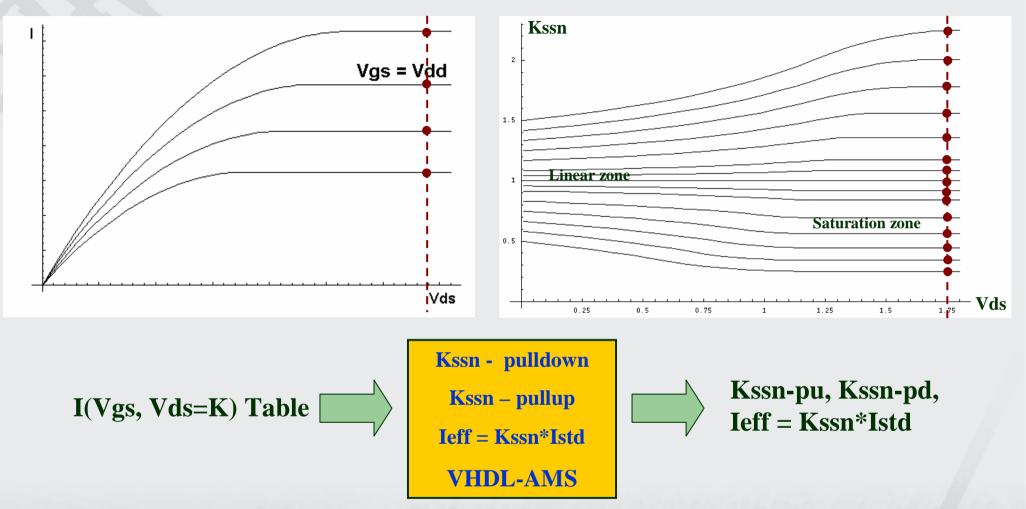

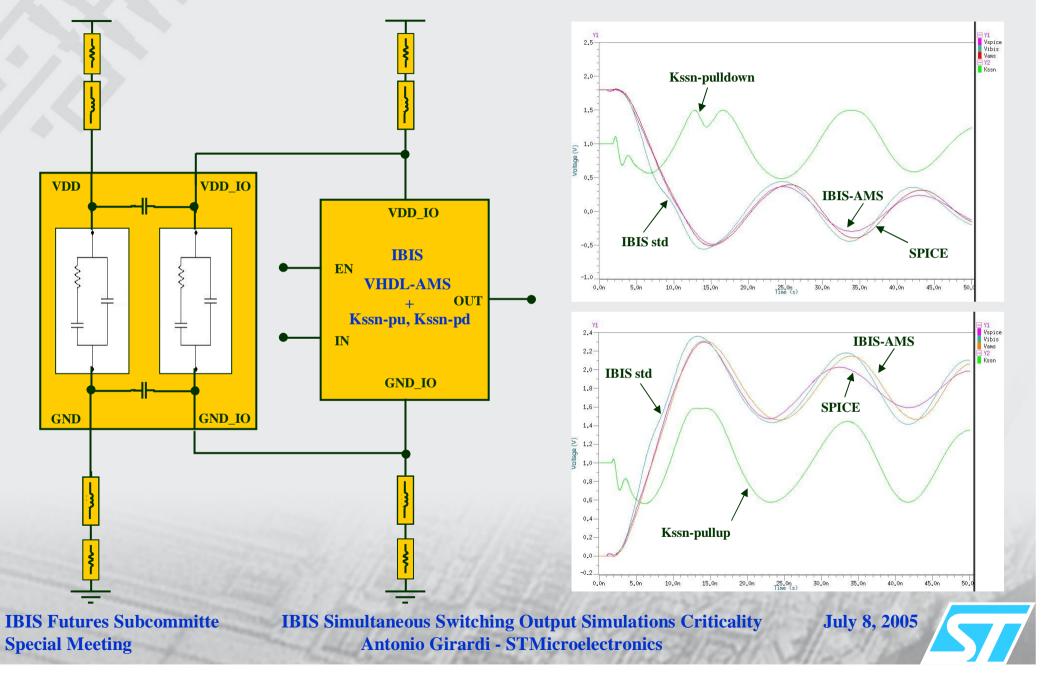

## Gate Modulation by one I(Vgs,Vds=K) Table

As it is not possible to change the EDA tools code which manage the IBIS models, the unique way to implement the Kssn's coefficients is to use the IBIS-VHDL-AMS implementation, adding the Gate modulation coefficients routine.

IBIS Futures Subcommitte Special Meeting IBIS Simultaneous Switching Output Simulations Criticality Antonio Girardi - STMicroelectronics

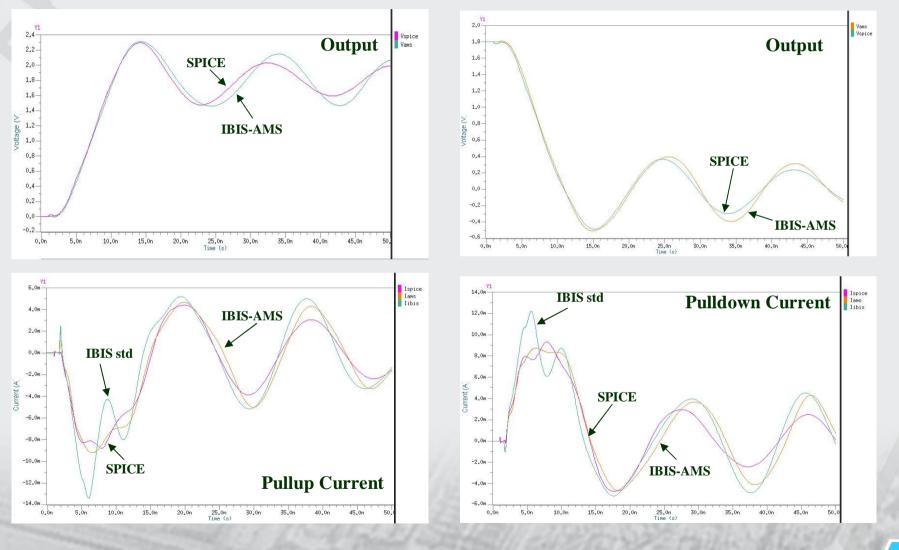

### **SSO simulations by IBIS-VHDL-AMS + Kssns coefficients**

## **Pullup and Pulldown Currents**

#### **SSO – Rise Transition**

**SSO – Fall Transition**

**IBIS Futures Subcommitte** Special Meeting IBIS Simultaneous Switching Output Simulations Criticality Antonio Girardi - STMicroelectronics

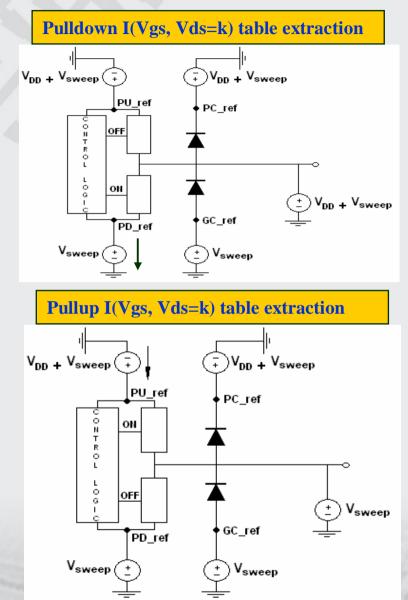

## Extraction of the I(Vgs,Vds=K) Table: Initial Choice

> Vsweep = [-Vdd, Vdd]

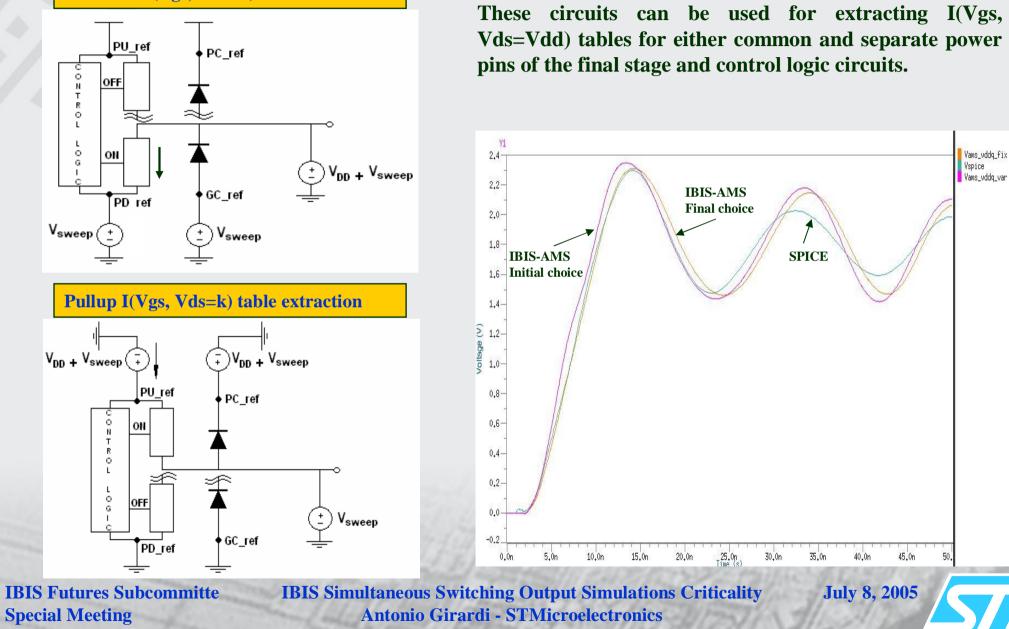

➤ The I-Vgs Pullup and Pulldown tables are extracted with Vds = Vdd

➤ These circuits do not work very well when the control logic and the final stages are powered by the same supply voltage: the behaviour of the control logic and its driving capability to final stage is not modelled correctly.

> During the bouncing, gnd and vdd nodes will change together by the bypass+parasitic capacitance, but the magnitude and phase of noise will be different on each one. Therefore, it is not correct to extract the I(Vgs, Vds=Vdd) tables considering the same Vsweep on both Vdd and Gnd nodes.

> The best way identified is to disconnect the stage that is not under investigation

IBIS Futures Subcommitte Special Meeting IBIS Simultaneous Switching Output Simulations Criticality Antonio Girardi - STMicroelectronics

## **Extraction of the I(Vgs,Vds=K) Table: Final Choice**

#### **Pulldown I(Vgs, Vds=k) table extraction**

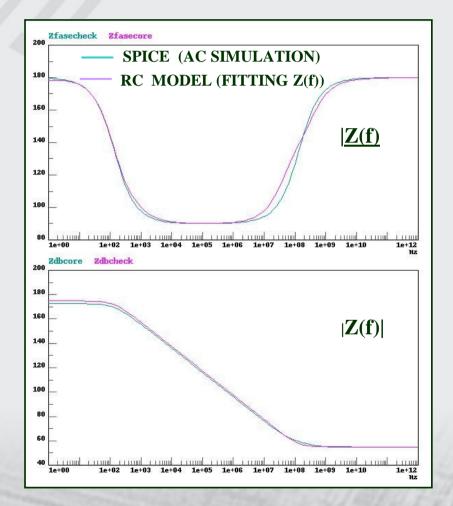

### **Benchmark SPICE vs IBIS (Gate Modulation Coefficients)**

### Very good IBISvsSpice matching for both outputs and power/ground signals

#### **SSO – Rise Transition**

#### **SSO – Fall Transition**

**Special Meeting**

Antonio Girardi - STMicroelectronics

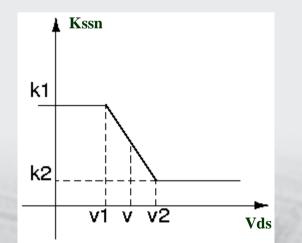

### Future Plan: Gate Modulation by two I(Vgs,Vds=K) Tables

**IBIS Futures Subcommitte Special Meeting**  To improve Vgs modulation accuracy in the linear zone, a solution with two Kssn coefficients for both pullup and pulldown stages, is under investigation.

> K<sub>1</sub> and K<sub>2</sub> coefficients are extracted in the saturation and linear zone, respectively

> V<sub>1</sub> and V<sub>2</sub> threshold voltages delimitate the interpolation zone

$\succ$  the best choice of V<sub>1</sub> and V<sub>2</sub> has not yet been identified

➤ the increase of computational time and IBIS-AMS simulation's speed has to be evaluate

IBIS Simultaneous Switching Output Simulations Criticality Antonio Girardi - STMicroelectronics

## Conclusions

• Actually the IBIS Simultaneous switching output simulations are not accurate

□ A power network model back-annotation and a "Gate modulation effect" implementation are needed

**RC** model for power network is a rough solution but enough accurate

□ Two modulation coefficients, based on table format, seem the best tradeoff between accuracy and computational time effort for describing the "Gate modulation effect"

□ At the moment, the most flexible way to implement the modulation coefficients is to extend the IBIS description by VHDL-AMS language

□ The "Gate Modulation Effect" algorithm might be suggested to CAD vendors and implemented in the EDA tools which manage IBIS models

A solution with two Kssn coefficients, for both pullup and pulldown stages, is under investigation.

**Special Meeting**

IBIS Futures Subcommitte IBIS Simultaneous Switching Output Simulations Criticality Antonio Girardi - STMicroelectronics