# **BUFFER ISSUE RESOLUTION DOCUMENT (BIRD)**

BIRD NUMBER: Draft 27 – December 15, 2015

ISSUE TITLE: Interconnect Modeling Using IBIS-ISS

REQUESTOR: Walter Katz, Signal Integrity Software, Inc.

DATE SUBMITTED: DATE REVISED:

DATE ACCEPTED BY IBIS OPEN FORUM:

#### STATEMENT OF THE ISSUE:

This BIRD enhances IBIS with interconnect modeling features to support broadband, coupled package, and on-die interconnect using IBIS-ISS and Touchstone data.

The BIRD also adds a keyword for buffer rail mapping, to link to new Terminal definitions defined for buffers.

#### ANALYSIS PATH/DATA THAT LED TO SPECIFICATION:

#### **Definitions:**

Enhanced interconnect descriptions in IBIS, called hereinafter "IBIS Interconnect Models", rely on several assumptions:

- 1. IBIS Interconnect Models can be described either using IBIS-ISS subcircuit files or Touchstone files. Interconnect Model definitions may be included inside an IBIS file, but neither IBIS-ISS nor Touchstone data may be included inside an IBIS file.

- 2. If two points in an IBIS Interconnect Model are "Linked", then there is either a low resistance DC electrical path between the two points, or a small insertion loss at the Nyquist frequency between the two points. For the purposes of IBIS Interconnect Models, "point" and "node" refer to identical locations.

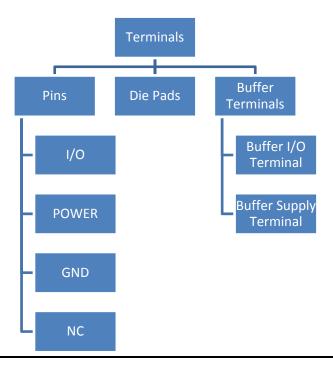

- 3. IBIS Components, and therefore IBIS Interconnect Models, contain terminals consisting of Pins, Die Pads, Buffer I/O Terminals, and Buffer Supply Terminals. Pins are defined under the [Pin] keyword, and may be I/O, POWER, GND, or NC.

- 4. For each I/O Pin, there is a single, associated Die Pad and single, associated Buffer I/O Terminal. All of these shall be considered "Linked".

- 5. Under [Pin], for each signal\_name associated with Model\_name POWER or GND, all Pins, Die Pads and Buffer Supply Terminals that use that signal\_name are "Linked"

- 6. IBIS assumes that each I/O [Pin] is connected to one Die Pad and one Buffer I/O Terminal. Two differential I/O pins shall be connected to two differential die pads and either two single-ended Buffer I/O Terminals or a single true differential Buffer I/O Terminal.

- 7. If multiple Buffer Terminals (Supply or I/O) are connected to a single pin, EMD shall be used for the interconnect description.

8. An Interconnect Model may describe the relationship between a single Pin and Buffer Terminal (Supply or I/O), a signle Pin and linked Die Pad, or between a single Die Pad and a Buffer Terminal (Supply or I/O). An Interconnect Model may also describe connections between multiple Pins and multiple Buffer Terminals (Supply and I/O), multiple Pins and multiple Die Pads, or multiple Die Pads and multiple Buffer Terminals (Supply and I/O).

#### ANY OTHER BACKGROUND INFORMATION:

Parameter is shorted to Param (.param is legal in IBIS-ISS) to differentiate it further from Parameters in the multi-lingual syntax (Parameter has several meanings in IBIS and the Algorithmic Modeling Interface.)

File\_names are not quoted, to be consistent with Corner in the multi-lingual syntax.

For File\_TS, all columns typ, min, and max are entered (or NA for either or both min and max) to follow the corner syntax convention used for most IBIS keywords and subparameters. The typ entry is required, and the typ entry value is used by the EDA tool for any NA entry. The same typ, min, max convention is used for the subparameter Param.

Entries for strings in Param are surrounded by double quotes to be consistent with string\_literal Parameters in the multi-lingual syntax (or where the AMI string\_literal parameter surrounded by double quotes is passed into the multi-lingual Parameters reference). The EDA tool needs to convert string\_literals into the parameter string syntax in IBIS-ISS.

Interaction of Param entries was not discussed. For example, for a transmission line, TD and Z0 could each have max and min entries, but the EDA tool could make available combinations of

min/min, min/max, max/min or max/max for any corner. Due to parameter interactions, some mixing of corner combinations might not be realistic. (E.g., Z0min or Z0max might not correlate with TDmin or TDmax values, where TDmin=sqrt(LminCmin), Z0min=sqrt(Lmin/Cmax), etc.). How corners of File\_IBIS-ISS and Params are processed might be based on vendor supplied documentation. For example some, but not all, combinations are shown below:

- 1. One file\_name for all corners, one .subckt name, and all corner settings controlled by Param settings

- 2. One file\_name, three .subckts (with internal default .param settings), additional corner settings controlled by Param settings or Param is not used

- 3. Three file\_names with the same .subckt name, but with distinct default .param settings, additional settings controlled by Param settings or Param is not used

- 4. Three file\_names with three distinct .subckt name and with distinct default .param settings, additional corner settings controlled by Param settings or Param is not used

No interpretation is given for Param typ, min, and max values. It is possible to independently use typ, min, or max values for any of the Param names that have been defined (e.g., the max value of one parameter may be used with the min value of another parameter).

The following keywords should be added as their own Chapter. The current Chapter 7 should be modified with the existing text placed in a sub-section called "[PACKAGE MODEL]".

\_\_\_\_\_

### 7 PACKAGE MODELING

Several types of package modeling formats are available in IBIS. These include:

- 1. Lumped [Component]-level models for the entire [Component], using the [Package] keyword

- 2. Lumped [Component]-level modeling per-pin, using the [Pin] keyword

- 3. [Package Model] (including [Alternate Package Models] and [Define Package Model])

- 4. [Interconnect Model Selector] and the keywords associated with it

The lumped formats are described in the [Package] and [Pin] keyword defintions above. The [Package Model] format is described in this chapter, while Interconnect Model Selectors are described in Chapter 13.

• • •

## 13 INTERCONNECT MODEL SELECTORS

This chapter defines an advanced format for interconnect descriptions that may be used for packages as well as other types of interconnect between buffer models and pins, for signal and power path modeling purposes.

The specification permits .ibs files to contain the following additional list of interconnect model keywords and subparameters. Note that the actual interconnect models may be in a separate <interconnect\_file\_name>.ict file or may exist in a .ibs file between the [Begin Interconnect Model] ... [End Interconnect Model] keywords for each interconnect model defined. For reference, these keywords and subparameters are listed in Error! Reference source not found.

Table XX – Interconnect Modeling Keywords and Subparameters

| Keyword or Subparameter     | Notes    |

|-----------------------------|----------|

| [Begin Interconnect Model]  |          |

| Manufacturer                | (note 1) |

| Description                 | (note 1) |

| Param                       | (note 1) |

| File_TS                     | (note 2) |

| File_IBIS-ISS               | (note 2) |

| Unused_Terminal_Termination | (note 3) |

| Number Of Terminals         | (note 4) |

| Keyword or Subparameter       | Notes    |

|-------------------------------|----------|

| <terminal line=""></terminal> | (note 5) |

| [End Interconnect Model]      | (note 1) |

- Note 1 Required when the [Begin Interconnect Model] keyword is used

- Note 2 One of either the File\_TS or File\_IBIS-ISS subparameter is required. .

- Note 3 The subparameter token shall be followed by the "=" character and a numeric value (integers and reals are acceptable), with both optionally surrounded by whitespace.

- Note 4 The subparameter token shall be followed by the "=" character and an integer value, with both optionally surrounded by whitespace.

- Note 5 No token or other reserved word is defined to identify terminal lines.

When interconnect model definitions occur within a .ibs file, their scope is "local"—they are known only within that .ibs file and no other. In addition, within that .ibs file, they override any global interconnect package models that have the same name.

Usage Rules for the .ict File:

Package models are stored in a file whose name looks like:

<filename>.ict.

The <filename> provided must adhere to the rules given in Section Error! Reference source not found., "GENERAL SYNTAX RULES AND GUIDELINES". Use the ".ict" extension to identify files containing interconnect models. The .ict file must contain all of the required elements of a normal .ibs file, including [IBIS Ver], [File Name], [File Rev], and the [End] keywords. Optional elements include the [Date], [Source], [Notes], [Disclaimer], [Copyright], and [Comment Char] keywords. All of the elements follow the same rules as those for a normal .ibs file.

Note that the [Component] and [Model] keywords are not allowed in the .ict file. The .ict file is for interconnect models only.

**Keyword:** [Interconnect Model Selector]

Required: No

Description: Used to list available interconnect models for the Component.

*Usage Rules:* Interconnect Models are described by IBIS-ISS or Touchstone files that connect the Pins, Die Pads, and Buffer Terminals (Supply and I/O) of a Component.

A Component may have none, one, or more than one Interconnect Model associated with it. If any Interconnect Models exist for the Component, they shall be listed in this section. An Interconnect Model Selector is required even if only a single Interconnect Model is associated with the Component. [Interconnect Model Selector] is hierarchically within the scope of the [Component] keyword.

The section under the [Interconnect Model Selector] keyword shall have two fields per line, with each line defining the Interconnect Models associated with the Component. The fields shall be separated by at least one white space. The first field lists the Interconnect Model name (up to 40 characters long). The second field is the name of the file containing the Interconnect Model, with the extension ".ict". If the Interconnect Model is in this IBIS file, then the second field shall be "\*".

The file containing the Interconnect Model shall be located in the same directory as the .ibs file. The file name shall follow the rules for .ibs file names given in Section 3, "GENERAL SYNTAX RULES AND GUIDELINES".

The first entry under the [Interconnect Model Selector] keyword shall be considered the default by the EDA tool. Each Interconnect Model name may only appear once under the [Interconnect Model Selector] keyword for a given Component.

## Example:

```

[Interconnect Model Selector]

QS-SMT-cer-8-pin-pkgs_iss *

QS-SMT-cer-8-pin-pkgs_sNp qs-smt-cer-8-pin-pkgs_s16p.ict

[End Interconnect Model Selector]

```

**Keyword:** [End Interconnect Model Selector]

Required: Yes, for each instance of the [Begin Interconnect Model Selector] keyword

Description: Indicates the end of the Interconnect Model selector data.

Example:

[End Interconnect Model Selector]

**Keyword:** [Begin Interconnect Model]

Required: No

Description: Marks the beginning of an Interconnect Model description.

*Usage Rules:* [Begin Interconnect Model] has a single argument, which is the name of the associated Interconnect Model. The length of the Interconnect Model name shall not exceed 40 characters in length. Blank characters are not allowed. The [Begin Interconnect Model]/[End Interconnect Model] keyword pair is hierarchically equivalent in scope to [Component] and [Model].

The [Begin Interconnect Model]/[End Interconnect Model] section defines both the association between a Touchstone or IBIS-ISS file and an Interconnect Model, as well as defining the terminals and terminal usage for the Interconnect Model in the context of the given [Component].

#### Example:

The following subparameters are defined:

Manufacturer

Description

Unused\_Terminal\_Termination = <value>

Number\_of\_Terminals = <value>

Param File\_TS File\_IBIS-ISS

<terminal line>

Unless noted below, no Interconnect Model subparameter requires the presence of any other subparameter.

#### Manufacturer rules:

This optional subparameter specifies the name of the interconnect's manufacturer. The length of the manufacturer's name shall not exceed 40 characters. Blank characters are permitted.

## Description rules:

This optional subparameter provides a concise yet easily human-readable description of what the Interconnect Model represents. The description shall be fewer than 60 characters in length, shall fit on a single line, and may contain spaces.

#### Unused Terminal Termination rules:

This optional subparameter defines the termination that is to be applied by the EDA tool during simulation to the Terminals of any IBIS-ISS subcircuit or Touchstone networks that are not being used in the [Begin Interconnect Model]/[End Interconnect Model] group. The subparameter name shall be followed by a single integer argument greater than zero on the same line. The argument shall be separated from the subparameter name by the "=" character. The subparameter name, "=" character, and argument may optionally be separated by whitespace.

If this subparameter is present, the EDA should connect the unused Terminals to GND through a resistor with the value of resistance in ohms provided in the argument.

If this parameter is not defined and File\_IBIS-ISS is present, then the EDA tool should connect the unused Terminals to GND through a 1 megaohm or larger resistor (the exact value used shall be reported to the user by the EDA tool). If File\_TS is present, then the EDA tool should connect the unused Terminals to GND through a resistor with the Touchstone file's reference resistance for the corresponding Terminal.

Only one Unused\_Terminal\_Termination subparameter may appear for a given [Begin Interconnect Model] keyword.

#### Number\_of\_Terminals rules:

The Number\_of\_Terminals subparameter is required and defines the number of Terminals associated with the Interconnect Model. The subparameter name shall be followed by a single integer argument greater than zero on the same line. The argument shall be separated from the subparameter name by the "=" character. The subparameter name, "=" character, and argument may optionally be separated by whitespace. Only one Number\_of\_Terminals subparameter may appear for a given [Begin Interconnect Model] keyword. The Number\_of\_Terminals

subparameter shall appear before any Terminal lines and after the Manufacturer subparameter for a given Interconnect Model.

#### Param rules:

The subparameter Param is optional and only legal with the File\_IBIS-ISS subparameter documented below. Param is illegal with the File\_TS subparameter documented below. Param shall be followed by three arguments: an unquoted string argument giving the name of the parameter to be passed into the IBIS-ISS, a reserved word for the parameter format, and one numerical value or one string value (surrounded by double quotes) for the parameter value to be passed into the IBIS-ISS.

The numerical value rules follow the scaling conventions in Section 3, GENERAL SYNTAX RULES AND GUIDELINES. The EDA tool is responsible for translating IBIS specified parameters into IBIS-ISS parameters. For example, 1 megaohm, would be represented as 1M in Param value according to The Section 3 rules, but would be converted by the EDA tool to case-insensitive 1meg (1X is not recommended) or 1E6 for IBIS-ISS use. Quoted string parameters in IBIS are converted to the string parameter syntax in IBIS-ISS. For example, the Param value "typ.s2p" would be converted to str('typ.s2p') in IBIS-ISS.

## Examples:

| Param | name    | format | value     |                         |

|-------|---------|--------|-----------|-------------------------|

| Param | abc     | Value  | 2m        | 2E-3 in IBIS            |

| Param | def     | Value  | 4k        | 4E3 in IBIS             |

| Param | ts_file | Value  | "typ_s2p" | file name string passed |

|       |         |        |           | into IBIS-ISS           |

## File IBIS-ISS rules:

Either File\_IBIS-ISS or File\_IBIS-TS is required for a [Begin Interconnect Model]/[End Interconnect Model] group. The File\_IBIS-ISS subparameter is followed by two unquoted string arguments consisting of the file\_name, and circuit\_name (.subckt name) for an IBIS-ISS file. The referenced file under file\_name shall be located in the same directory as the .ibs file.

#### File TS rules:

Either File\_TS or File\_IBIS-ISS is required for a [Begin Interconnect Model]/[End Interconnect Model] group. File\_TS is followed by one unquoted string argument, which is the file name for a Touchstone file. The Touchstone file under file\_name shall be located in the same directory as the referencing.ibs file or .ict file.

#### Terminal Line rules:

Terminal lines shall appear after the Number\_of\_Terminals subparameter and before the [End Interconnect Model] keyword. No token or reserved word identifies terminal lines.

Each Terminal line contains information on a terminal of an IBIS-ISS subcircuit (or Touchstone file).

#### Terminal lines are of the form

<Terminal\_number> <Terminal\_type> <Terminal\_type\_qualifier> Aggressor

#### Terminal number

Terminal\_number is an identifier for a specific terminal. Terminal\_number shall be a positive non-zero integer less than or equal to the value of the Number\_of\_Terminals argument. The same Terminal\_number shall not appear more than once for a given Interconnect Model. If any Terminals are not present for a given Interconnect Model, then those terminals are unused, and shall be terminated according to the Unused\_Terminal\_Termination rules.

Terminal\_type shall be one of the following: Buffer\_I/O, PUref, PDref, PCref, GCref, EXTref, Buffer\_Rail, Pad\_I/O, Pad\_Rail, Pin\_I/O, or Pin\_Rail. Buffer\_I/O, PUref, PDref, PCref, GCref, EXTref and Buffer\_Rail are terminals of an Interconnect Model that connect directly to I/O buffers. Pin\_I/O and Pin\_Rail are terminals that are at the Die/Package interface. Pin\_I/O and Pin\_Rail are terminals that are at the Component PCB interface.

The Terminal\_type\_qualifier for Terminal\_types Buffer\_I/O, PUref, PDref, PCref, GCref and EXTref shall be pin\_name. The Terminal\_type\_qualifier for Terminal\_type Buffer\_Rail may be signal\_name or bus\_label.

The Terminal\_type\_qualifier for Terminal\_type Pad\_I/O shall be pin\_name.

The Terminal\_type\_qualifier for Terminal\_type Pad\_Rail shall be either pad\_name, signal\_name, or bus\_label.

The Terminal\_type\_qualifier for Terminal\_type Pin\_I/O shall be pin\_name.

The Terminal\_type\_qualifier for Terminal\_type Pin\_Rail shall be either pin\_name, signal\_name, or bus label.

The optional Aggressor field is only allowed allowed on Buffer\_I/O records. Connections to Buffer\_I/O terminals may be missing coupling to connects that are not included in this interconnect model.

Table XX summarizes the rules described above.

Table XX – Allow Terminal\_Type Associations

| Terminal_type | pin_name | signal_name | bus_label | pad_name | Aggressor |

|---------------|----------|-------------|-----------|----------|-----------|

| Buffer_I/O    | X        |             |           |          | A         |

| PUref         | X        |             |           |          |           |

| Terminal_type | pin_name | signal_name | bus_label | pad_name | Aggressor |

|---------------|----------|-------------|-----------|----------|-----------|

| PDref         | X        |             |           |          |           |

| PCref         | X        |             |           |          |           |

| GCref         | X        |             |           |          |           |

| EXTref        | X        |             |           |          |           |

| Buffer_Rail   |          | Y           | Y         |          |           |

| Pad_I/O       | X        |             |           |          |           |

| Pad_Rail      |          | Y           | Y         | Z        |           |

| Pin_I/O       | X        |             |           |          |           |

| Pin_Rail      | Y        | Y           | Y         |          |           |

### What do X, Y, and Z mean above?

## Connecting Pins, Pads and Terminals

Three classes of pins are defined for a Component: Signal Pins, Supply Pins and No Connect Pins. Supply Pins have a model\_name of either POWER or GND. No Connect Pins have model\_name NC. All other pins are classified as Signal Pins. Package models defined in this section assume that there is one Buffer\_I/O Terminal and one Die Pad for each Signal Pin. Pins are assumed to use the names listed under the first column of the [Pin] keyword (the pin\_name column).

The model of an I/O buffer has supply terminals in addition to the Buffer\_I/O. These supply (or rail) terminals can be PUref, PDref, PCref, GCref and/or EXTref. The PUref, PDref, PCref, GCref and/or EXTref terminal of a buffer are associated either with a bus\_label under the [Pin Mapping] keyword or a signal\_name under the [Pin] keyword. These terminals can be connected to interconnect models one of two ways:

- 1. By specifying a unique interconnect terminal for each I/O buffer PUref, PDref, PCref, GCref and/or EXTref

- 2. By assuming that all I/O buffer supply terminals connected to a supply signal\_name or bus\_label are shorted together. This is done by specifying a unique terminal for all I/O buffer terminals that are connected to a specific signal\_name or bus\_label on at least one Supply Pin.

Pads are the location of the interface between the die and the package. Interconnect models can either be between the Pins of a component and the I/O buffers, or they can be split into models between the Pins of a component and the Pads of the die, and model between the Pads of the die and the I/O buffer models. There is exactly one Pad (Pad\_I/O) for each Signal Pin. There can be any number of Pads (Pad\_Rail) for each signal\_name or buf\_label on Supply Pins. If interconnect models of supply (rail) networks are split between Pin/Pad and Pad/Buffer models, then the interface of supply connections at the die package interface can be handled in one of two ways:

- 1. By defining a list of Die Supply Pads, and specifying terminals for some or all of the Die Supply Pads that are connected to a bus\_label or signal\_name on at least one Supply Pin.

- 2. By assuming that all supply Pads connected to a supply signal\_name or bus\_label are shorted together. This is done by specifying a unique terminal for all Pads that are connected to a specific signal\_name on at least one Supply Pin.

Pins may be terminals of the Interconnect model that connect directly to a PCB board or other type of system connection to an IBIS component. Pins can be Signal Pins (Pin\_I/O), or Supply Pins (Pin\_Rail). An Interconnect model can connect supply pins in one of two ways:

- 1. By specifying terminals for some or all of the Supply Pins.

- 2. By assuming that all supply Pins connected to a supply signal\_name or bus\_label are shorted together. This is done by specifying a unique terminal for all Pins that are connected to a specific signal\_name on at least one Supply Pin.

For an Interconnect Model using File\_TS with N ports, N shall match the number of ports present in the data of the associated Touchstone 1.x file, or the value associated with the [Number of Ports] field in the associated Touchstone 2 file. The [Number of Terminals] entry in the Interconnect Model shall be an integer equal to N+1. Terminal rules are described below:

• The EDA tool shall use the pin\_name or signal\_name specified for the associated Terminal "N+1" entry as the reference node for each of the N ports. For an Interconnect Model with N ports, the Terminals and Ports are associated as follows:

| 0 | <u>Terminal</u> | <u>Port</u> |

|---|-----------------|-------------|

| 0 | 1               | 1           |

| 0 | 2               | 2           |

| 0 | •••             |             |

| 0 | N               | N           |

| 0 | N+1             | reference   |

- If a Port is not connected, then it shall be terminated by the EDA tool with a resistor to the node on Terminal N+1. The value of this resistance shall be the value associated with the Port Reference Impedance subparameter.

- Terminal N+1 shall be connected to a Pin, Pad, or Buffer which is in turn connected to a signal\_name of POWER or GND.

The Terminals of an Interconnect Model may be located at Pins and Pads, Pins and Buffers, or Pads and Buffers. A single Interconnect Model shall not have Terminals at Pins, Pads and Buffers simultaneously.

## IBIS Specification Change Template, Rev. 1.2

```

Examples:

[Pin] signal_name model_name

R_pin

L_pin

C_pin

Α1

DQ1

DQ

Α2

DQ2

DQ

Α3

DQ3

DQ

D1

DQS+

DQS

D2

DQS-

DQS

POWER

Ρ1

VDD

POWER

Ρ2

VDD

VDD

POWER

Р3

Ρ4

VDD

POWER

Р5

VDD

POWER

G1

VSS

GND

G2

VSS

GND

G3

VSS

GND

G4

GND

VSS

[Diff Pin] inv_pin

vdiff

tdelay_typ tdelay_min tdelay_max

NA

NA

D2

NA

NA

[Die Supply Pads] signal name

VDD1 VDD

VDD2 VDD

VDD3 VDD

VSS1 VSS

VSS2 VSS

[Pin Mapping] pulldown_ref pullup_ref gnd_clamp_ref power_clamp_ref ext_ref

Α1

VSS

VDD

NC

NC

NC

Α2

VSS

VDD

NC

NC

NC

А3

VSS

VDD

NC

NC

NC

D1

VSS

VDD

NC

NC

NC

D2

VSS

VDD

NC

NC

NC

| Full Package/Die Model Complex Power Distribution

Number_of_Terminals 29

1 Pin_I/O

Pin_name A1

DQ1

DQ

2 Pin_I/O

Pin_name A2

DQ2

DQ

Pin_I/O

Pin_name A3

3

DQ3

DQ

4

Pin_name D1

DQS

Pin_I/O

DQS+

Pin_I/O

Pin_name D2

DQS-

DOS

Pin I/O

Pin name P1

VDD

POWER

7

Pin I/O

Pin name P2

VDD

POWER

8 Pin I/O

Pin name P3

VDD

POWER

9 Pin I/O

Pin name P4

VDD

POWER

10 Pin Rail

Pin name P5

VDD

POWER

11 Pin_Rail

Pin_name G1

VSS

GND

12 Pin_Rail

Pin_name G2

VSS

GND

13 Pin_Rail

Pin_name G3

VSS

GND

14 Pin_Rail

Pin_name G4

VSS

GND

15 Buffer_I/O Pin_name A1

DQ1

DQ

16 Buffer_I/O

Pin name A2

DQ2

DQ

17 Buffer_I/O

Pin_name A3

DQ3

DQ

18 Buffer_I/O

Pin_name D1

DQS

DQS+

19 Buffer_I/O Pin_name D2

DQS-

DQS

20 PUref

Pin_name A1

DQ

DQ1

```

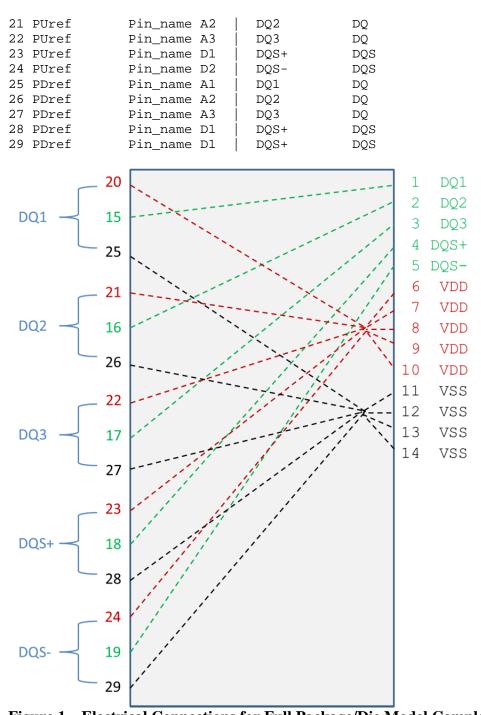

Figure 1 – Electrical Connections for Full Package/Die Model Complex Power Example

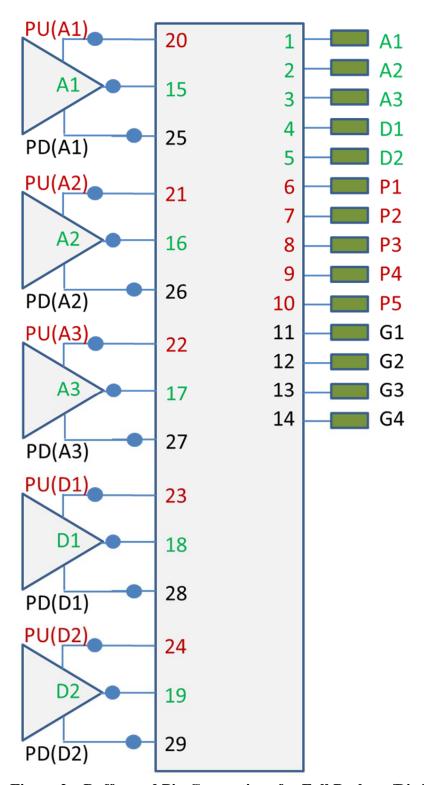

Figure 2 – Buffer and Pin Connections for Full Package/Die Model Complex Power Example

#### | Full Package/Die Model Simple Power Distribution Number\_of\_Terminals 14 1 Pin I/O Pin name A1 DQ1 DQ 2 Pin\_I/O Pin\_name A2 DQ2 DQ Pin\_name A3 3 Pin\_I/O DQ3 DQ 4 Pin I/O Pin name D1 DQS+ DQS Pin I/O Pin name D2 DQS-DQS Pin\_Rail signal\_name POWER 6 VDD VDD Pin\_Rail signal\_name 7 VSS VSS GND 8 Buffer\_I/O Pin\_name A1 DQ1 DQ 9 Buffer\_I/O Pin\_name A2 DQ2 DQ 10 Buffer\_I/O Pin\_name A3 DQ3 DQ 11 Buffer I/O Pin name D1 DQS+ DQS 12 Buffer\_I/O Pin\_name D2 DQS-DQS 13 Buffer\_Rail signal\_name VDD VDD POWER

VSS

VSS

GND

#### | Single DQ (A1)

Number\_of\_Terminals 2

1 Pin\_I/O Pin\_name A1

14 Buffer\_Rail signal\_name

2 Buffer\_I/O Pin\_name A1

#### | Single DQ (A1), Split into package and on-die models

Number\_of\_Terminals 2

1 Pin\_I/O Pin\_name A1

2 Pad\_I/O Pin\_name A1

Number\_of\_Terminals 2

1 Pad\_I/O Pin\_name A1

2 Buffer\_I/O Pin\_name A1

## Full VDD Power Supply Model

| N. | Number_of_Terminals 9 |          |        |     |     |     |       |

|----|-----------------------|----------|--------|-----|-----|-----|-------|

| 1  | Pin_Ra                | ail Pir  | n_name | P1  | VDD |     | POWER |

| 2  | Pin_Ra                | ail Pir  | n_name | P2  | VDD |     | POWER |

| 3  | Pin_Ra                | ail Pir  | n_name | P3  | VDD |     | POWER |

| 4  | Pin_Ra                | ail Pir  | n_name | P4  | VDD |     | POWER |

| 5  | Pin_Ra                | ail Pir  | n_name | P5  | VDD |     | POWER |

| 6  | PDref                 | Pin_name | e A1   | DQ1 | L   | DQ  |       |

| 7  | PDref                 | Pin_name | e A2   | DQ2 | 2   | DQ  |       |

| 8  | PDref                 | Pin_name | e A3   | DQ3 | 3   | DQ  |       |

| 9  | PDref                 | Pin_name | e D1   | DQS | 5+  | DQS |       |

## Full VDD Power Supply Model split into package and on-die

| Nι | umber_of_7 | Terminals | 8    |     |       |

|----|------------|-----------|------|-----|-------|

| 1  | Pin_Rail   | Pin_name  | P1   | VDD | POWER |

| 2  | Pin_Rail   | Pin_name  | P2   | VDD | POWER |

| 3  | Pin_Rail   | Pin_name  | P3   | VDD | POWER |

| 4  | Pin_Rail   | Pin_name  | P4   | VDD | POWER |

| 5  | Pin_Rail   | Pin_name  | P5   | VDD | POWER |

| 6  | Pad_Rail   | Pad_name  | VDD1 | VDD | POWER |

| 7  | Pad_Rail   | Pad_name  | VDD2 | VDD | POWER |

| 8  | Pad_Rail   | Pad_name  | VDD3 | VDD | POWER |

| Nι | umber_of_7 | Terminals | 7    |     |       |

| 1  | Pad_Rail   | Pad_name  | VDD1 | VDD | POWER |

## IBIS Specification Change Template, Rev. 1.2

| 2 | Pad_Rail | Pad_name | VDD2 | VDD  | POWER |

|---|----------|----------|------|------|-------|

| 3 | Pad_Rail | Pad_name | VDD3 | VDD  | POWER |

| 4 | PDref    | Pin_name | A1   | DQ1  | DQ    |

| 5 | PDref    | Pin_name | A2   | DQ2  | DQ    |

| 6 | PDref    | Pin_name | A3   | DQ3  | DQ    |

| 7 | PDref    | Pin name | D1   | DOS+ | DOS   |

Power supply model assuming pins shorted, pads shorted, and buffer rail shorted  $[Number\_of\_Terminals\ 2]$

```

1 Pin_Rail signal_name VDD | VDD POWER

2 Buffer_Rail signal_name VDD | VDD POWER

```

Power supply model assuming pins shorted, pads shorted, and buffer rail shorted, split between package and die

Number\_of\_Terminals 2

| 1  | Pin_Rail        | signal_name | VDD | VDD | POWER |

|----|-----------------|-------------|-----|-----|-------|

| 2  | Pad_Rail        | signal_name | VDD | VDD | POWER |

| Nι | umber_of_Termir | nals 2      | ·   |     |       |

| 1  | Pad_Rail        | signal_name | VDD | VDD | POWER |

| 2  | Buffer_Rail     | signal name | VDD | VDD | POWER |

#### | Single DQ Crosstalk Model

Number\_of\_Terminals 6

- 1 Pin\_I/O Pin\_name A1

- 2 Buffer\_I/O Pin\_name Al Aggressor

- 3 Pin\_I/O Pin\_name A2

- 4 Buffer\_I/O Pin\_name A2

- 5 Pin\_I/O Pin\_name A3

- 6 Buffer\_I/O Pin\_name A3 Aggressor

### Example with signal\_name split into bus\_labels

```

Examples:

[Pin] signal_name model_name

C pin

R pin

L pin

DO1

Α1

DO

Α2

DO2

DO

Α3

DO3

DO

Α4

DQ4

DQ

Р1

VDD

POWER

Ρ2

VDD

POWER

G1

VSS

GND

G2

GND

VSS

[Bus Label] signal_name

VDD1 VDD

VDD2 VDD

[Pin Mapping] pulldown_ref pullup_ref gnd_clamp_ref power_clamp_ref ext_ref

VDD1

NC

VSS

NC

NC

Α2

VSS

VDD1

NC

NC

NC

Α3

VSS

VDD2

NC

NC

NC

NC

NC

NC

Α4

VSS

VDD2

Р1

NC

VDD1

NC

NC

NC

P2

NC

VDD2

NC

NC

NC

G1

VSS

NC

NC

NC

NC

G2

VSS

NC

NC

NC

NC

Power supply model assuming pins shorted, pads shorted, and buffer rail

shorted

Number_of_Terminals 2

1 Pin_Rail

signal_name VDD

VDD

POWER

2 Pin_Rail

signal_name VSS

VSS

GND

3 Buffer_Rail bus_label

VDD

VDD1

POWER

4 Buffer_Rail bus_label

VDD2

VDD

POWER

5 Buffer_Rail signal_name VSS

VDD

POWER

The EDA tool connects the terminals and pins as follows:

1 Pins P1 and P2

2 Pins G1 and G2

3 PUref of buffers A1 and A2

```

**Keyword:** [End Interconnect Model]

|5 PDref of buffers A1, A2, A3 and A4

4 PUref of buffers A3 and A4

Required: Yes, for each instance of the [Begin Interconnect Model] keyword

Description: Indicates the end of the Interconnect Model data.

*Other Notes:* Between the [Begin Interconnect Model] and [End Interconnect Model] keywords is the package model data itself. The data describes any number of interfaces to either IBIS-ISS models or Touchstone files.

Example:

```

[End Interconnect Model]

```

The following keywords should be placed in the specification text near the [Pin Mapping] keyword.

Keyword: [Bus Label]

Required: No

*Description:* Associates a POWER or GROUND signal\_name with one or more bus\_label names within a Component. Bus\_label names can also be associated with specific Pins, Pads or I/O buffer rail terminals. These bus\_labels names can be used to define terminals of interconnect subcircuits.

Sub-Params: signal\_name

*Usage Rules:* The first column shall contain a bus\_label. The second column, signal\_name, gives the data book name for the signal on that bus\_label.

The signal\_name shall be the signal\_name used for a pin under the [Pin] keyword that uses the model\_name POWER or GND.

A bus\_label may not be the same as any signal\_name. Duplicate bus\_labels are not permitted. A bus\_label may be defined also by the [Pin Mapping] keyword.

Column length limits are:

```

[Bus Label] 40 characters max signal_name 40 characters max

```

## Example:

| [Bus | Label] | signal_name |

|------|--------|-------------|

| VDD1 |        | VDD         |

| VDD2 |        | VDD         |

| VDD3 |        | VDD         |

| VSS1 |        | VSS         |

| VSS2 |        | VSS         |

*Keyword:* [Die Supply Pads]

Required: No

Description: Assigns die pads as supply nodes within a Component. IBIS assumes that for I/O pins (pins that have a Model\_name that is not POWER, GND or NC), there is a one-to-one correspondence between a Pin, a Die Pad and the Buffer I/O terminal connection point. There are no such assumptions for POWER and GND pins. A POWER or GND signal\_name may have a different number of Pin nodes, die pad nodes and buffer nodes. If the model maker chooses to make separate package and on-die power distribution networks (PDN), then he shall supply a list of nodes (and their associated signal\_name) that can be used to mate the package and on-die PDN models.

Sub-Params: None

*Usage Rules:* Arguments under the [Die Supply Pads] keyword consist of two strings per line, where the strings define a die pad node name and a corresponding signal\_name or bus\_label, in that order. Signal\_names and bus\_labels may appear multiple times, but die pad node names may appear only once each under the [Die Supply Pads] keyword.

*Other Notes:* The data in this section consists of a list of die pad node names and their corresponding signal\_names or bus\_label that can be used to mate package and on-die PDN networks.

## Example:

[Die Supply Pads]

VDD1 VDD1

VDD2 VDD

VDD3 VDD

VSS1 VSS

VSS2 VSS

**Keyword:** [End Die Supply Pads]

Required: Yes

Description: Indicates the end of the [Die Supply Pads] data.

Other Notes: Example:

[End Die Supply Pads]

An IBIS Interconnect Model section may be included in a separate Interconnect file, with the extension ".ict". The Interconnect file shall contain all of the required elements of a normal .ibs file, including [IBIS Ver], [File Name], [File Rev], and the [End] keywords, and at least one [Begin Interconnect Model] and one [End Interconnect Model] keyword. Optional elements include the [Date], [Source], [Notes], [Disclaimer], [Copyright], and [Comment Char] keywords. All of the elements follow the same rules as those for a normal .ibs file.

Note that the [Component] and [Model] keywords are not allowed in the .ict file. The .ict file is for IBIS Interconnect Models only. One or multiple Interconnect Models may be included in a .ict file.

The following sections should be appended to the end of the IBIS document.

## 12 RULES OF PRECEDENCE

The sections below detail the rules of precedence to be assumed by EDA tools and model makers where multiple keywords may support similar functions.

#### 12.1 PACKAGES

The order of precedence for package model data to be used by EDA tools in simulation is defined below, in ascending order. If a package data format at a numerically higher position on the list is available in an IBIS or related file, that data shall be used by the EDA tool for simulation; any data present in formats numerically lower on the list shall be ignored for that file.

- 1. [Component]/[Package]

- 2. [Component]/[Pin]

- 3. [Package Model] (including [Alternate Package Models] and [Define Package Model])

- 4. [Interconnect Model Selector]