## Channel Simulation Using IBIS Models with Asymmetric Rising and Falling Edges

Ken Willis, Cadence Kumar Keshavan, Cadence Ambrish Varma, Cadence IBIS Summit – DesignCon 2019 Santa Clara, California February 1, 2019

#### Overview

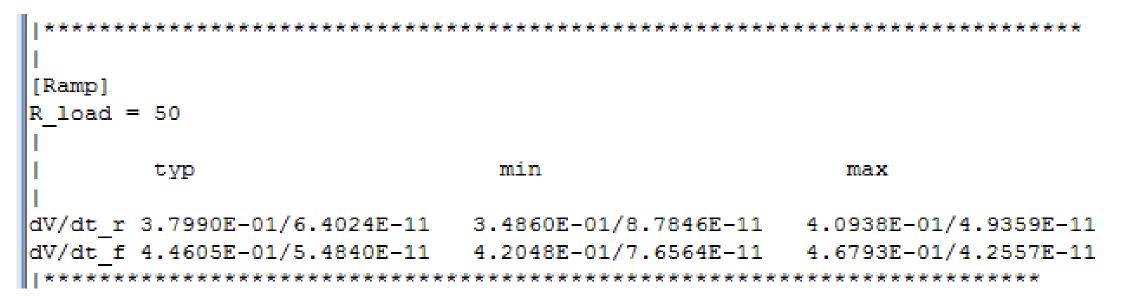

- As channel simulation and IBIS-AMI modeling methods are adapted from serial link to DDR interface analysis, we encounter IBIS IO models with asymmetric rising and falling edges

- This is different from the highly symmetric drivers we typically encounter with serial link analysis

- Traditional single step response methods for impulse response generation may not reproduce circuit simulation results accurately enough

- These slides show how an EDA tool can handle this (without changes to the IBIS specification)

- All cases use Micron's **y11a.ibs** file for 8Gbps DDR5, provided by Randy Wolff

cadence

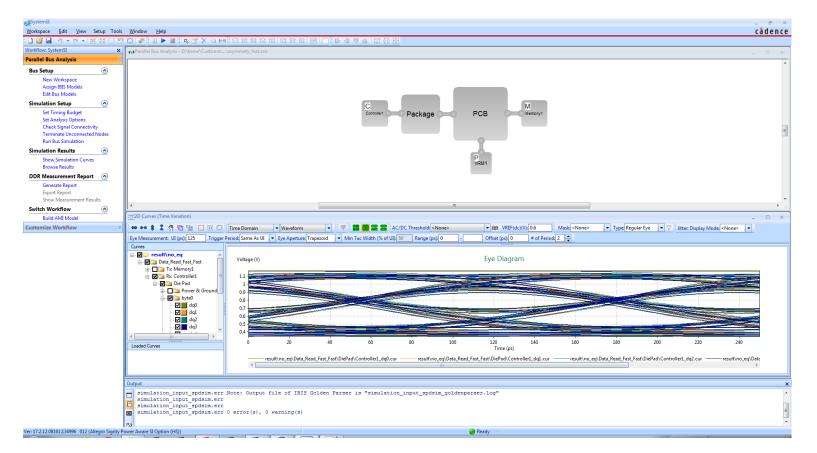

### SystemSI Testbench

- Package block uses an extracted RLCK Spice model

- PCB block uses W-elements with 0.3 meter lengths

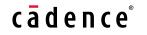

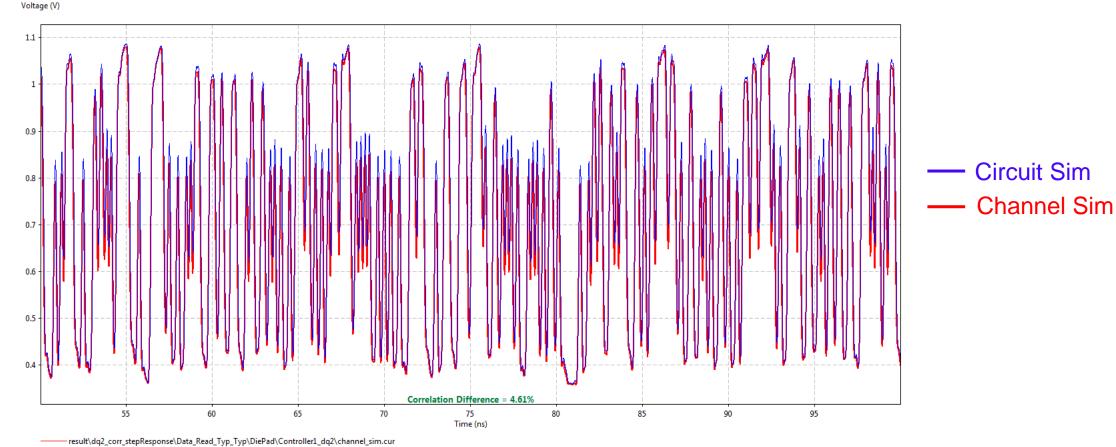

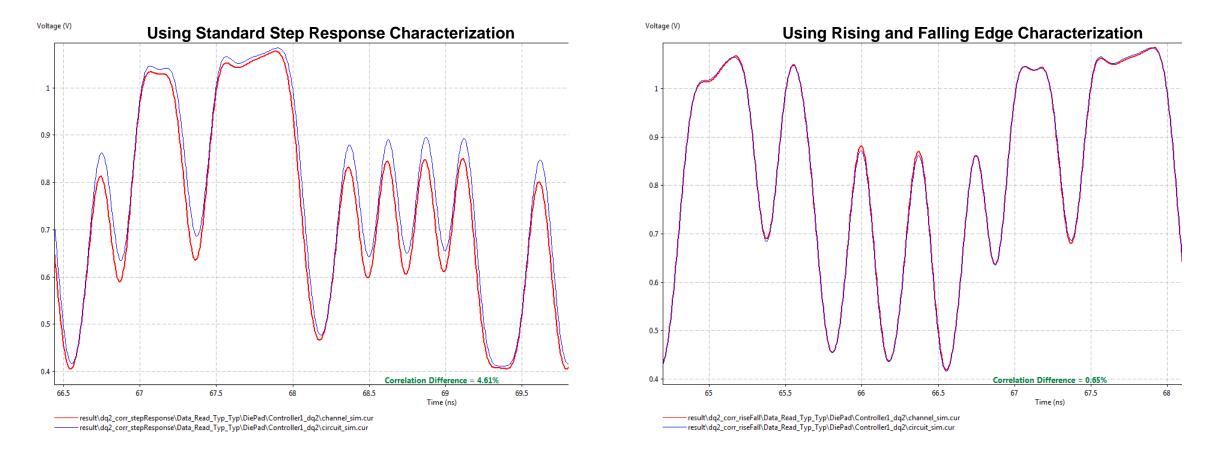

## Using Standard Step Response Characterization

Correlation difference 4.61%

<sup>-</sup>result\dq2\_corr\_stepResponse\Data\_Read\_Typ\_Typ\DiePad\Controller1\_dq2\circuit\_sim.cur

#### Same Result Zoomed In

Voltage (V)

Circuit SimChannel Sim

cādence°

5

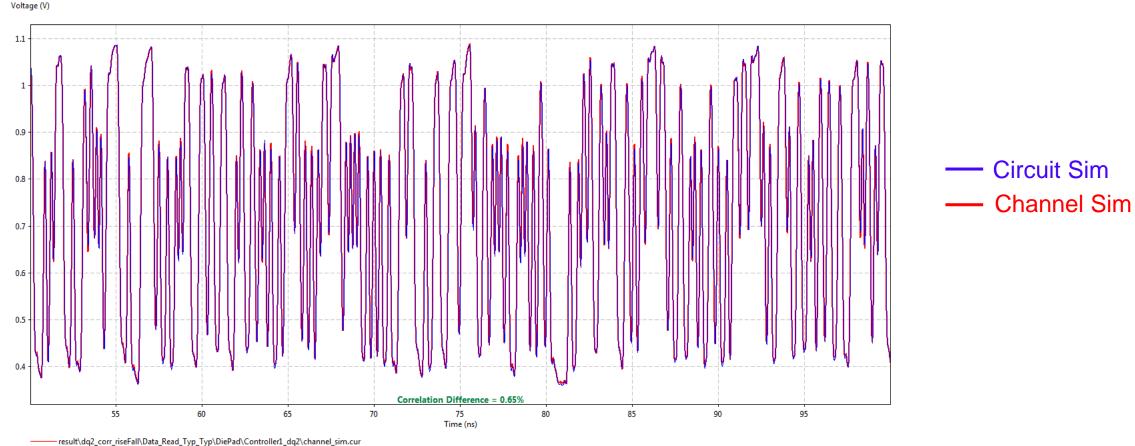

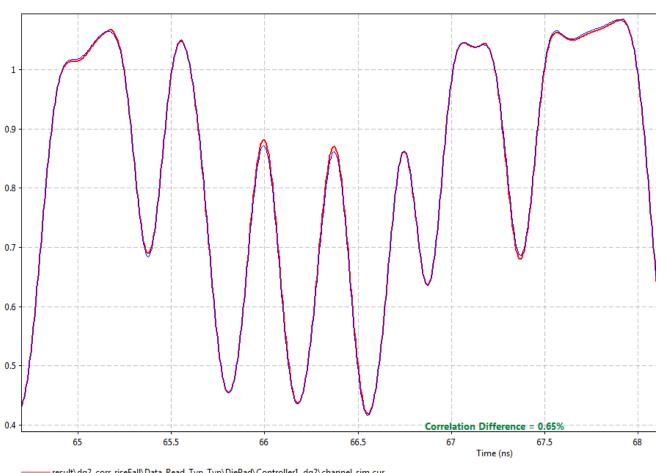

## Using Rising and Falling Edge Characterization

Correlation difference 0.65%

#### Same Result Zoomed In

Voltage (V)

Circuit SimChannel Sim

#### **Comparison of Both Methods**

• Correlation error vs. circuit simulation reduced by about 4%

#### cādence°

### Summary

- The **DQ\_34\_3600** IO model has some asymmetry in its rising and falling edges

- Standard SerDes step response characterization did not do a great job in capturing this behavior, as seen in the circuit / channel sim correlation

- Characterization methods using rising and falling edges captured this behavior very well for channel simulation

9

# cādence®

© 2019 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <u>www.cadence.com/go/trademarks</u> are trademarks or registered trademarks of Cadence Design Systems, Inc. All other trademarks are the property of their respective owners.